緩沖放大器在大多數應用中也像理想的前置放大器一樣工作,但除了前置放大之外,它還起到信號輸入級和功率放大器級之間的高阻抗緩沖器的作用。這尤其允許這些類型的前置放大器與極低電流輸入信號一起使用,而這些信號無法承受其他低阻抗型前置放大器的負載。

此處所示的緩沖放大器在100kHz時的輸入阻抗通常超過1 M,輸入阻抗可以簡單地調整到低于該點的任何可接受電平。電路的電壓增益是單位的。

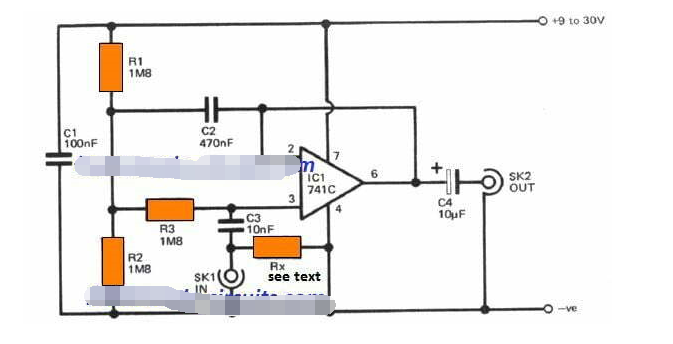

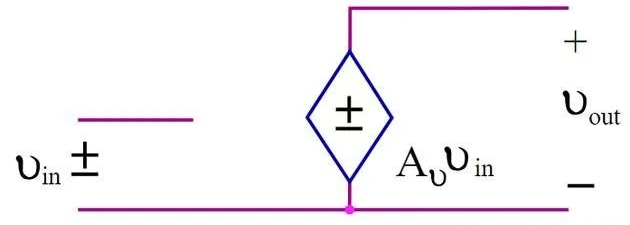

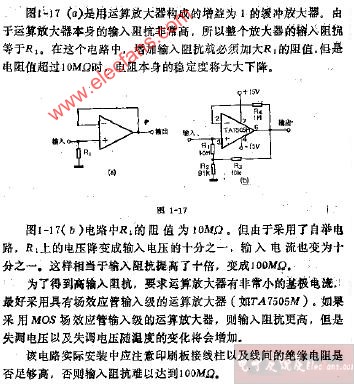

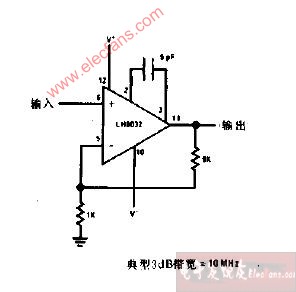

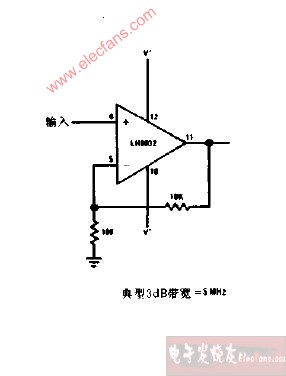

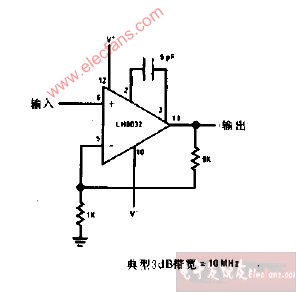

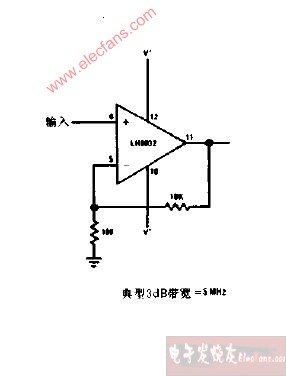

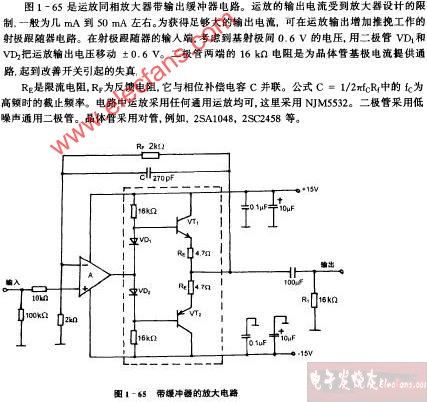

上圖顯示了高阻抗緩沖放大器的電路圖,該單元本質上只是一個運算放大器,用作單位增益的同相放大器。通過將IC1的輸出直接耦合到其反相輸入,在系統上增加100%的負反饋,以實現所需的單位電壓增益以及非常高的輸入阻抗。

盡管如此,偏置電路(在這種情況下包括R1至R3)分流放大器的輸入阻抗,使電路整體提供的輸入阻抗遠小于單獨的IC1。輸入阻抗約為 2.7

兆歐,對于大多數應用,這可能就足夠了。

但是,可以消除偏置電阻的分流作用,這就是C2電容“自舉”的目標。它將輸出信號連接到三個偏置電阻結,因此輸入電壓的任何調整都通過IC1輸出端和三個偏置電阻的交點處的相等電壓偏移來平衡。

在IC1角色中,采用基本的741 C運算放大器,如前所述,這提供了通常在100 kHz時超過1兆歐的輸入阻抗,這對于任何標準實現來說都足夠了。

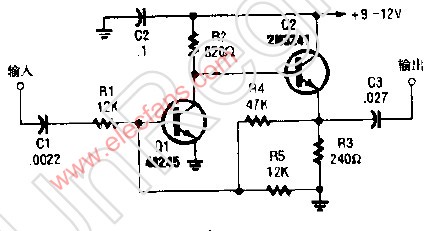

使用工作放大器實現的更高輸入阻抗實際上并不具有任何實際意義,因此本電路中的大多數FET輸入系統都存在一些缺點。

首先,當輸入打開時,它們實際上具有振蕩傾向(當輸入連接到器件時,振蕩被衰減并消除)。

另一個缺點是,許多FET輸入器件的輸入功率遠高于741

IC等雙極器件。通過這種分流動作,在大多數頻率下,輸入阻抗現在降低,而在低低音和中頻下,輸入阻抗更高。

為此,需要相對較低的輸入阻抗(例如具有許多100

k歐姆和M歐姆的推薦電荷阻抗的拾音器),實現此目的的一種方法是消除C2并將R1的數量更改為R3以獲得所需的輸入阻抗。

零件清單

印刷電路板布局

-

緩沖放大器

+關注

關注

1文章

28瀏覽量

16678 -

高阻抗

+關注

關注

0文章

19瀏覽量

10267

發布評論請先 登錄

相關推薦

TI技術專訪:挖掘高帶寬高阻抗緩沖放大器背后的特色技術設計

電壓型緩沖放大器和電流型緩沖放大器的作用?

高速高輸入阻抗穩定緩沖放大器電路

什么是緩沖放大器

高阻抗緩沖放大器的工作原理

高阻抗緩沖放大器的工作原理

評論