上兩篇已經(jīng)總結(jié)和分享了RGB接口TFT-LCD觸摸屏的相關(guān)內(nèi)容。 本篇使用Verilog語言實現(xiàn)RGB的驅(qū)動時序。

前面描述了很多關(guān)于時序的內(nèi)容,但其實在FPGA中實現(xiàn)RGB接口的LCD屏驅(qū)動時序還是很簡單的。 只需要實現(xiàn)行掃描、列掃描的時鐘周期控制,并且在有效區(qū)域輸出對應(yīng)像素點的RGB數(shù)據(jù)便可。 實現(xiàn)控制時序和測試驗證難度不大,主要還是要在實際的項目中應(yīng)用,例如:實時顯示攝像頭的圖像信息等。 由于文字篇幅原因, 本篇僅對RGB接口驅(qū)動時序的實現(xiàn)思想以及Verilog語言代碼進行說明。

下面正式進入本章推送的內(nèi)容。

01 時序參數(shù)

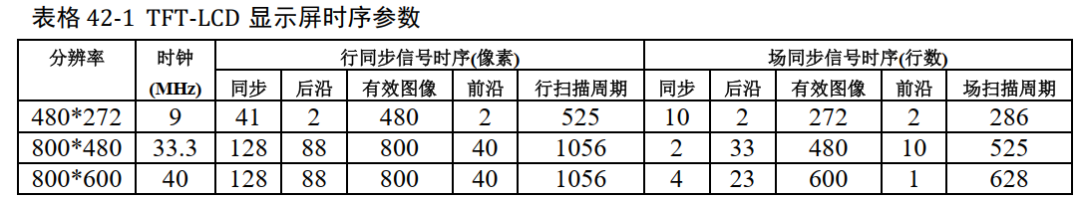

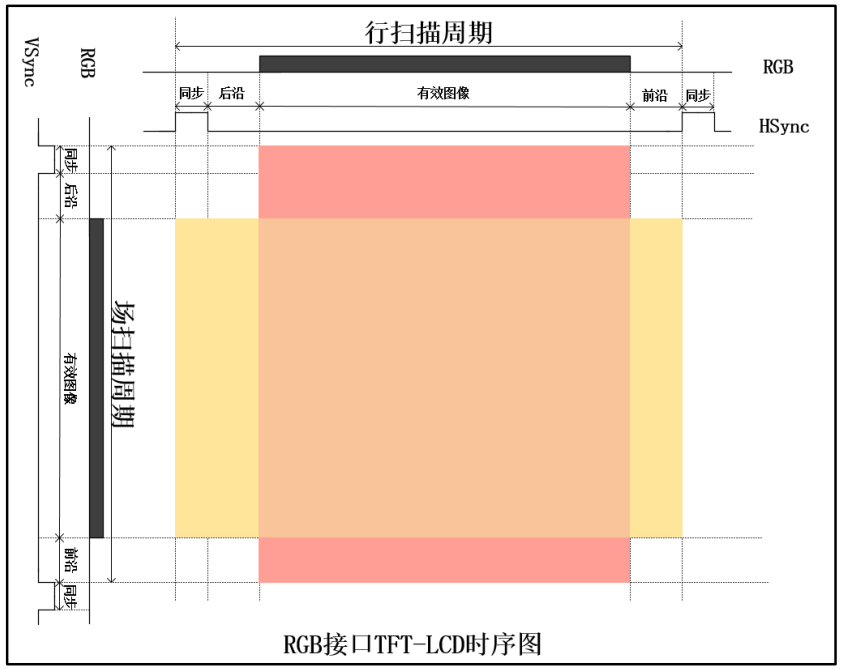

常用的TFT-LCD屏(幀率為60Hz)時序參數(shù)如下圖所示,其中,行同步信號時序的單位是時鐘脈沖,而場同步信號時序的單位是行周期。

對于驅(qū)動時序而言,最重要的是確定幀率和像素時鐘,其他參數(shù)由廠商提供。本示例使用的是分辨率為800*480 的4.3寸TFT-LCD屏,使用的幀率為60Hz(每秒60幀圖像),時序參參數(shù)以及相關(guān)計算公式如下表所示:

02 時序?qū)崿F(xiàn)

對于幀率和分辨率固定的LCD屏幕驅(qū)動時序(RGB接口),有以下特點:

- 圖像輸出的行掃描、列掃描是周期性的邏輯

- 同步時序(SYNC)、有效信號(DE)的脈沖固定

設(shè)計思路

FPGA設(shè)計周期性的時序,可以通過計數(shù)器來控制,在計數(shù)器的對應(yīng)count數(shù)執(zhí)行相對應(yīng)的邏輯; 對于邏輯而言,需要考慮的是同步信號、數(shù)據(jù)有效信號的范圍脈沖數(shù)、以及掃描周期; 行掃描、列掃描對應(yīng)的設(shè)計思路如下(800*480 @60 TFT-LCD屏示例):

| 時序 | 設(shè)計思路描述 |

|---|---|

| 行掃描 | 設(shè)計場掃描脈沖計數(shù)器,對PCLK脈沖計數(shù); 計數(shù)的最大值 = 行掃描周期; 計數(shù)自增條件為時鐘脈沖高電平(PCLK); 當cnt>H Pulse width時, HSYNC=1,否則為HSYNC=0; |

| 場掃描 | 設(shè)計場掃描脈沖計數(shù)器,對行掃描周期計數(shù); 場掃描計數(shù)最大值 = 場掃描周期; 計數(shù)自增條件為行掃描周期; 當cnt>V Pulsewidth時,VSYNC=1,否則為VSYNC=0; |

行掃描時序?qū)崿F(xiàn)

由于FPGA設(shè)計計數(shù)器時,一般從0開始計數(shù),因此行掃描邏輯控制參數(shù)需要減去1,如下表所示:

| 邏輯控制參數(shù) | 說明 | 數(shù)值(單位:PCLK) |

|---|---|---|

| H_SYNC | 行同步持續(xù)時間 | 128-1 |

| H_DATA_START | 行數(shù)據(jù)開始 | 216-1 |

| H_DATA_END | 行數(shù)據(jù)結(jié)束 | 1016-1 |

| H_PERIOD | 行掃描周期 | 1055-1 |

Verilog實現(xiàn)代碼如下:

parameter H_SYNC = 11'd127 ;

parameter H_DATA_START = 11'd215 ;

parameter H_DATA_END = 11'd1015 ;

parameter H_PERIOD = 11'd1055 ;

//行掃描控制時序

reg [10:0] h_cnt;

always @(posedge pclk) begin

if(rst_n == 1'b0) begin

h_cnt <= 11'd0;

end

else if(h_cnt == H_PERIOD) begin

h_cnt <= 11'd0;

end

else begin

h_cnt <= h_cnt + 1'b1;

end

end

assign hsync = (h_cnt > H_SYNC) ? 1'b1 : 1'b0;

assign h_index = (h_cnt > H_DATA_START) ? (h_cnt - H_DATA_START) : 11'd0;

場掃描時序?qū)崿F(xiàn)

由于FPGA設(shè)計計數(shù)器時,一般從0開始計數(shù),因此行掃描邏輯控制參數(shù)需要減去1,如下表所示:

| 參數(shù) | 說明 | 數(shù)值(單位:PCLK) |

|---|---|---|

| V_SYNC | 行同步持續(xù)時間 | 2-1 |

| V_DATA_START | 行數(shù)據(jù)開始 | 216-1 |

| V_DATA_END | 行數(shù)據(jù)結(jié)束 | 1016-1 |

| V_PERIOD | 行掃描周期 | 1055-1 |

Verilog實現(xiàn)代碼如下:

parameter v_SYNC = 11'd1 ;

parameter v_DATA_START = 11'd34 ;

parameter v_DATA_END = 11'd514 ;

parameter v_PERIOD = 11'd524 ;

//場掃描控制時序

reg [10:0] v_cnt;

always @(posedge pclk) begin

if(rst_n == 1'b0) begin

v_cnt <= 11'd0;

end

else if(v_cnt == v_PERIOD) begin

v_cnt <= 11'd0;

end

else if(h_cnt == H_PERIOD) begin

v_cnt <= v_cnt + 1'b1;

end

else begin

v_cnt <= v_cnt;

end

end

assign vsync = (v_cnt > v_SYNC) ? 1'b1 : 1'b0;

assign v_index = (v_cnt > v_DATA_START) ? (v_cnt - v_DATA_START) : 11'd0;

完整Verilog代碼如下:

module parallel_rgb_control

#

(

parameter H_SYNC = 11'd127 ,

parameter H_DATA_START = 11'd215 ,

parameter H_DATA_END = 11'd1015 ,

parameter H_PERIOD = 11'd1055 ,

parameter v_SYNC = 11'd1 ,

parameter v_DATA_START = 11'd34 ,

parameter v_DATA_END = 11'd514 ,

parameter v_PERIOD = 11'd524

)

(

input wire pclk ,

input wire rst_n ,

output wire hsync ,

output wire [10:0] h_index ,

output wire vsync ,

output wire [10:0] v_index ,

output wire de

);

//行掃描控制時序

reg [10:0] h_cnt;

always @(posedge pclk) begin

if(rst_n == 1'b0) begin

h_cnt <= 11'd0;

end

else if(h_cnt == H_PERIOD) begin

h_cnt <= 11'd0;

end

else begin

h_cnt <= h_cnt + 1'b1;

end

end

assign hsync = (h_cnt > H_SYNC) ? 1'b1 : 1'b0;

assign h_index = (h_cnt > H_DATA_START) ? (h_cnt - H_DATA_START) : 11'd0;

//場掃描控制時序

reg [10:0] v_cnt;

always @(posedge pclk) begin

if(rst_n == 1'b0) begin

v_cnt <= 11'd0;

end

else if(v_cnt == v_PERIOD) begin

v_cnt <= 11'd0;

end

else if(h_cnt == H_PERIOD) begin

v_cnt <= v_cnt + 1'b1;

end

else begin

v_cnt <= v_cnt;

end

end

assign vsync = (v_cnt > v_SYNC) ? 1'b1 : 1'b0;

assign v_index = (v_cnt > v_DATA_START) ? (v_cnt - v_DATA_START) : 11'd0;

assign de = ( (h_cnt >= H_DATA_START) && (h_cnt < H_DATA_END) ) && ( (v_cnt >= v_DATA_START) && (v_cnt < v_DATA_END) );

endmodule

05 文章總結(jié)

對于RGB接口的TFT-LCD屏的時序驅(qū)動代碼還是較為簡單的。 使用文字描述實際的應(yīng)用并且讓人容易理解,還是很困難的。 基于此,本篇僅僅只是分享了RGB接口周期時序的實現(xiàn),對于具體的數(shù)據(jù)輸出顯示的應(yīng)用并未說明。 倘若有兄弟想了解實際應(yīng)用,可以添加杰克的微信號來交流。

-

lcd

+關(guān)注

關(guān)注

34文章

4424瀏覽量

167410 -

接口

+關(guān)注

關(guān)注

33文章

8575瀏覽量

151021 -

觸摸屏

+關(guān)注

關(guān)注

42文章

2301瀏覽量

116120 -

RGB

+關(guān)注

關(guān)注

4文章

798瀏覽量

58461 -

時序

+關(guān)注

關(guān)注

5文章

387瀏覽量

37318

發(fā)布評論請先 登錄

相關(guān)推薦

怎樣通過STM32的普通IO口模擬8080總線來控制TFT-LCD的顯示

TFT-lcd液晶屏接口類型之ttl接口相關(guān)資料分享

TFT-LCD驅(qū)動IC設(shè)計

S3C2440A 驅(qū)動RGB 接口TFT LCD的研究

TFT-LCD系統(tǒng)時序控制模塊的設(shè)計

LCD控制及觸摸屏接口設(shè)計

微雪電子10.1寸 電容觸摸 彩色 LCD 顯示模塊簡介

ATK-7 TFT LCD電容觸摸屏模塊測試實驗的工程文件免費下載

如何使用STM32 HAL庫驅(qū)動TFT-LCD實現(xiàn)手畫板功能

LCD | TFT LCD 觸摸屏的選擇

TFT-LCD電容觸摸屏模塊(RGB接口)驅(qū)動時序設(shè)計

TFT-LCD電容觸摸屏模塊(RGB接口)驅(qū)動時序設(shè)計

評論