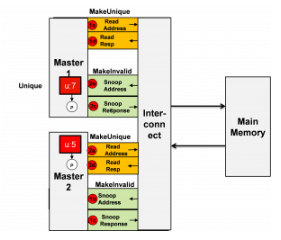

用于片上系統 (SoC) 中功能塊連接和管理的 AMBA 4 規范現在具有支持多核計算的高級可擴展接口 (AXI) 一致性擴展 (ACE)。ACE 規范支持跨多核處理器群集的系統級緩存一致性。對這種系統的核查提出了重大挑戰。在規劃這樣一個系統的功能驗證時,我們需要有一個有效的測試策略,以確保不僅測試協議的所有方面,而且確保以最少的努力捕獲錯誤。換句話說,我們需要有一個分層測試策略,從簡單的序列發展到更復雜的序列。目的是用更簡單的序列捕獲盡可能多的問題,這樣當我們移動到問題空間更大的更復雜的序列時,我們需要處理的錯誤就會減少。在本系列中,我們將提出這樣的分層驗證策略。本系列中的每篇文章都將描述:

正在測試的高級功能以及用于測試這些功能的序列

在此測試級別中,DUT 面臨的常見問題

在這里,您可以找到有關 AMBA 4 AXI 驗證 IP 的更多信息。

ACE 的分層測試 從 ACE

的角度來看,我們應該在每個層次結構級別測試什么?這些可能是:

集成/連接測試

系統是否正確連接?

每個主站能否正確訪問系統中的每個從站?

互連路由事務是否正確?

互連是否正確寫入/讀取數據?

基本一致性事務測試

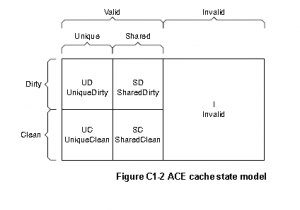

ACE 協議使用許多不同類型的事務。這些事務中的每一個都可以由具有許多不同狀態的相應緩存行(以下稱為初始緩存行狀態)的主服務器啟動。對于這些州中的每一個,都有允許的法律回應。隨著最終緩存行狀態(事務結束后)由各種配置選項確定,問題空間變得更加復雜。我們需要確保測試每個初始緩存行狀態的所有響應類型。在此級別的測試中,我們確保系統針對每種交易類型正確且一致地工作。

涉及訪問重疊地址的測試

該規范給出了當兩個主站訪問相同/重疊地址時互連要遵守的幾條規則。在此級別的測試中,我們執行序列以確保對重疊地址的所有訪問都遵循這些規則

DVM 和屏障交易測試

全面的隨機測試(包括對重疊地址的訪問)

在這篇文章中,我們將詳細說明分層驗證的第一個方面。

集成和連接測試

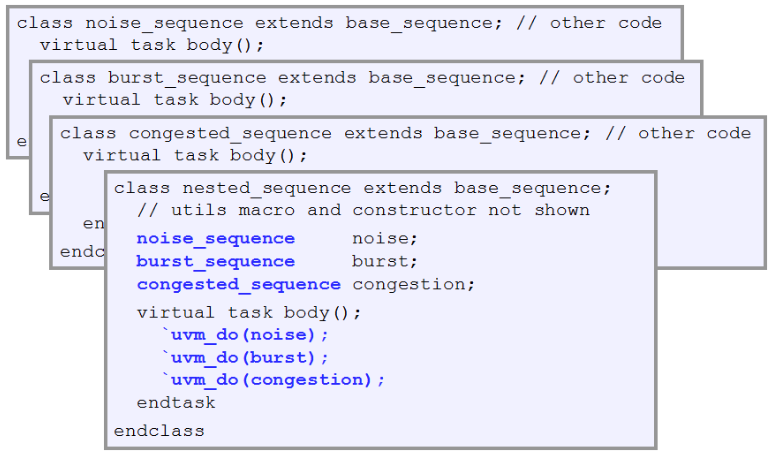

前面已經提到了集成和連接測試的關鍵驗證要求。驗證 IP 通常提供用于生成相關流量的現成序列。VIP附帶的一組此類序列或序列庫可以用作滿足用戶要求的起點。這使用戶能夠在適當的仿真階段方便地使用它們,并修改與其DUT相關的所需參數。因此,即使對于集成測試,用戶也可以利用VIP附帶的一些基本序列。讓我們看一下可用于此目的的序列類型。鑒于我們想要查看所有有效路徑,我們應該有一組序列,這些序列將從 ACE/ACE_LITE 主站啟動 WriteNoSnoop 和 ReadNoSnoop 事務,該主站使用屬性指定,例如port_id,可以是隨機端口或用戶配置的特定端口。“port_id”是一個屬性,可以配置為控制要從中啟動事務的端口。然后,應在系統中的所有主服務器上運行這些序列。

下面是一個示例。以下代碼片段顯示了如何配置 port_id 屬性:

uvm_config_db#(int unsigned)::set(this, “env.axi_system_env.sequencer.svt_axi_ace_master_readnosnoop_sequence”, “port_id”, 1);

此屬性的默認值可以根據系統中的主節點數量隨機化為有效值。

我們還需要確保主站訪問系統中允許它訪問的所有從站,以便測試所有路徑。為此,我們需要根據系統地址映射來約束地址,以便我們可以確保覆蓋所有路徑。這可以通過定義自定義約束來完成。

這就是我們如何在從主端啟動的事務上創建自定義約束:

class cust_svt_axi_master_transaction extends svt_axi_master_transaction;

rand int slave_port_id = 0;

constraint valid_slave_port_id {

slave_port_id inside {[0:`SVT_AXI_MAX_NUM_SLAVES-1]};

//` SVT_AXI_MAX_NUM_SLAVES defines the maximum no. of slaves in the system environment

}

constraint cust_addr_ranges_constraint {

// Accesses from master 0:

if (port_cfg.port_id == 0) {

// Accesses to slave 0

if (slave_port_id == 0) {

addr inside {[0:32’hff]}

}

else if (slave_port_id == 1) {

addr inside {[32’h10000:32’h100ff]};

}

// Accesses from master 1 }

else if (port_cfg.port_id == 1) { }

}

endclass

集成測試中的關鍵驗證點和潛在問題

系統連接

SoC 有數百個信號需要連接,而其中一些信號通常連接不正確。如果未連接,VIP 將在這些信號上觀察到“X”,并報告指示相同的錯誤。例如,此錯誤可能表示互連的主端口和從機[2] VIP之間未連接ARCACHE信號:

ace_system_env.slave[2].monitor [register_fail] 檢查 [效果=錯誤]:執行和失敗 – 啟用 AMBA 檢查:signal_valid_arsnoop_when_arvalid_high_check(ACE_LITE/版本 2.0),描述:當 ARVALID 為高時,監視器檢查 ARCACHE 上的 X 或 Z

事務路由

互連必須根據系統地址映射正確路由事務。應該有適當的方法來指定 VIP 的系統地址映射。如果互連路由事務不正確,系統監視器可以標記相應的“事務路由檢查”。

數據完整性

此級別測試的一個關鍵方面是確保數據完整性。寫入事務中的數據必須正確寫入從站。同樣,從從站獲取的數據必須正確返回給主站。系統監視器應通過在事務完成后(在啟動事務的主服務器上)比較內存中的數據和事務來執行這些檢查。系統監視器應具有跨不同數據寬度的端口執行這些檢查所需的基礎結構。為了使數據完整性檢查正常工作,在從屬VIP上運行的序列必須更新相應代理中的從屬內存實例。如果從屬VIP配置為被動模式,則系統監視器應維護內存鏡像并根據總線上的活動對其進行更新。如果數據未正確寫入/讀取,系統監視器應標記數據完整性檢查。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19920瀏覽量

235655 -

soc

+關注

關注

38文章

4398瀏覽量

222987 -

ACE

+關注

關注

0文章

24瀏覽量

10903

發布評論請先 登錄

如何使用AXI VIP在AXI4(Full)主接口中執行驗證和查找錯誤

數據增大是否是AXI互連的一部分?

將Zynq UltraScale +模塊連接到AXI互連模塊出錯該怎么辦?

請問為什么AXI互連資源如此之大?

ARM系列之ACE協議資料匯總

AMBA 4 ACE和ACE Lite協議校驗器用戶指南

如何使用Xilinx AXI進行驗證和調試

SoC設計中的互連驗證中遇到的問題

驗證符合AXI/ACE標準的互連的策略:第一部分

驗證符合AXI/ACE標準的互連的策略:第二部分

驗證符合AXI/ACE標準的互連的策略:第三部分

評論