前面在時序分析中提到過亞穩(wěn)態(tài)的概念,每天學習一點FPGA知識點(9)之時序分析并且在電路設(shè)計中如果不滿足Tsu(建立時間)和Th(保持時間),很容易就出現(xiàn)亞穩(wěn)態(tài);在跨時鐘域傳輸?shù)囊幌盗写胧┮彩菫榱私档蛠喎€(wěn)態(tài)發(fā)生的概率。

今天再說另一個可能會產(chǎn)生亞穩(wěn)態(tài)問題的電路;

復位電路;

1??recovery time和removal time

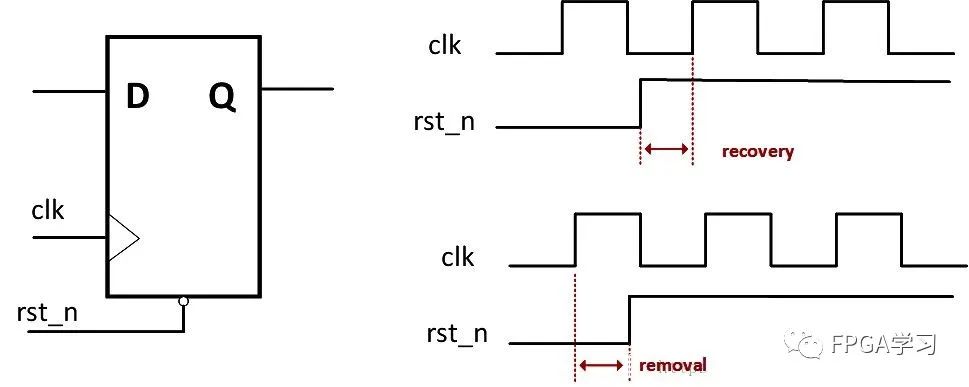

在正式開始復位電路設(shè)計之前,先說明兩個概念,恢復時間(recovery time)和移除時間(removal time)。[注,此處以低電平復位為例]

恢復時間:撤銷復位時,復位信號無效到時鐘有效沿來臨之前需要維持的最小的時間,稱為恢復時間,類似于同步時鐘的建立時間setup time;

移除時間:撤銷復位時,在時鐘有效沿來臨之后復位信號還需要保持復位狀態(tài)的時間為去除時間,類似于同步時鐘的保持時間hold time;

如下圖所示:

[注]:

①概念中所說的兩個時鐘沿并不是同一個時鐘沿,可以從另一個角度解釋:以復位結(jié)束的上升沿(低電平復位的情況下)為基準,復位結(jié)束前一個時鐘沿到復位結(jié)束之間為移除時間;復位結(jié)束后到下一個時鐘沿之間為恢復時間。

②兩個定義都是在復位結(jié)束的時候定義的,因為復位結(jié)束,系統(tǒng)馬上處于工作狀態(tài),所以才需要考慮亞穩(wěn)態(tài)問題。

2??同步復位和異步復位

①同步復位

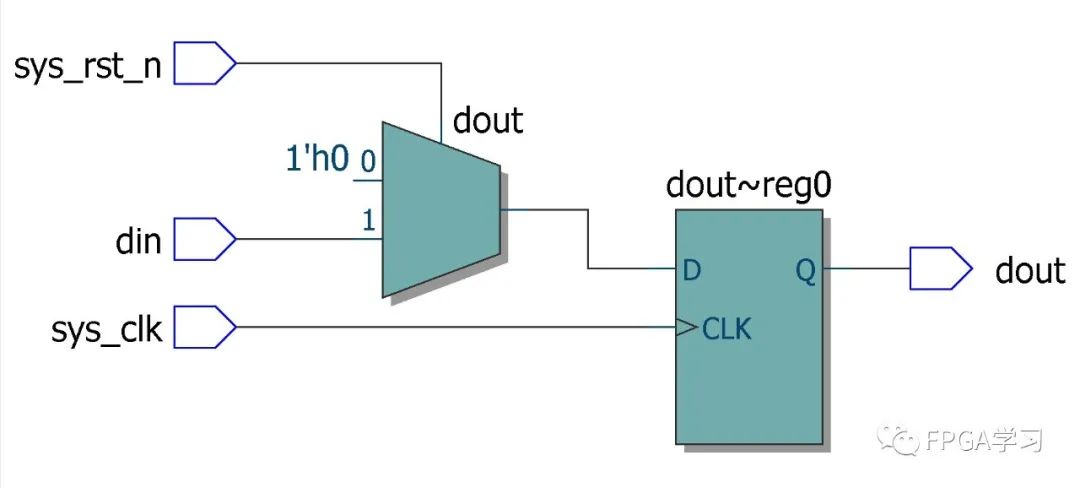

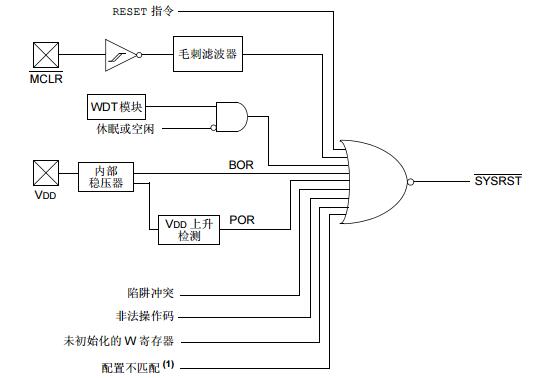

同步復位:指的是加到所有功能觸發(fā)器上的復位信號完全同步于時鐘信號源。復位信號只有在時鐘上升沿到來時,才能有效,否則,無法完成對系統(tǒng)的復位工作。復位原理如下圖所示:

[圖源:CSDN@小汪的IC自習室]

其代碼如下:

module test(

input sys_clk,

input sys_rst_n,

input din,

output reg dout

);

always@(posedge sys_clk) begin

if(!sys_rst_n)

dout <= 1'b0;

else

dout <= din;

end

endmodule

綜合后的電路圖如下:

優(yōu)點 :

*系統(tǒng)為同步時序,有利于時序分析;

*抗干擾性能好,能有效剔除信號中短于時鐘周期的毛刺;

缺點 :

*復位信號的有效時長必須大于時鐘周期,才能真正被系統(tǒng)識別并完成復位。同時還要考慮如:時鐘偏移、組合邏輯路徑延時、復位延時等因素。

*由于大多數(shù)的廠商目標庫內(nèi)的觸發(fā)器都只有異步復位端口,采用同步復位的話,就會耗費較多的邏輯資源(如上圖中使用了一個2選1多路選擇器)。

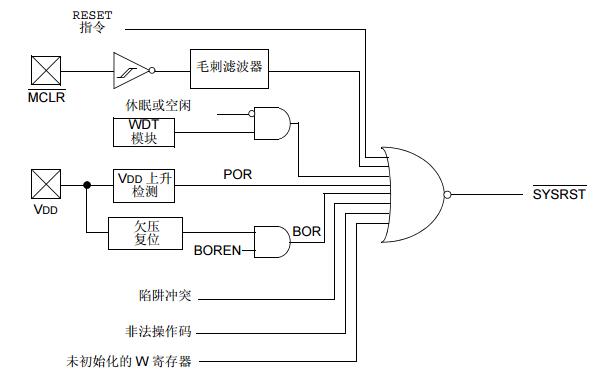

②異步復位

復位信號直接接到功能觸發(fā)器的異步復位引腳,復位只與復位信號有關(guān),與時鐘無關(guān)。無論時鐘沿是否到來,只要復位信號有效,就對系統(tǒng)進行復位。異步復位的工作原理如下圖所示:

其代碼如下:

module test(

input sys_clk,

input sys_rst_n,

input din,

output reg dout

);

always@(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

dout <= 1'b0;

else

dout <= din;

end

endmodule

綜合出的電路圖,如下圖所示:

通過這個圖能很明顯得看出來,比同步復位電路少用了一些資源。

通過這個圖能很明顯得看出來,比同步復位電路少用了一些資源。

優(yōu)點 :

*異步復位信號識別方便,很容易應(yīng)用到全局復位;

*可以節(jié)省邏輯資源(對比兩個復位電路即可看出);

缺點 :

*復位信號容易受到毛刺的影響,一點毛刺信號就有可能引發(fā)電路復位,造成系統(tǒng)運行錯誤。

*復位信號的釋放具有隨機性,如果復位信號釋放不滿足recovery或者removal,則會導致亞穩(wěn)態(tài)的產(chǎn)生。

當然了,其實在同步復位情況下,也會有亞穩(wěn)態(tài)問題的產(chǎn)生,詳情參考文章《 FPGA中亞穩(wěn)態(tài)——讓你無處可逃 》,作者博客園:@屋檐下的龍卷風。

3??異步復位同步釋放

對于復位情況下的亞穩(wěn)態(tài),常常是因為不滿足時序要求造成的(主要是recovery和removal),最常用的處理方式是異步復位,同步釋放。

通過異步復位和同步釋放,可以使復位信號到來時,不受時鐘控制,可以立即復位;但是復位信號釋放時,受同步時鐘控制。

其電路原理圖如下:

先通過兩級觸發(fā)器進行異步復位信號的同步,輸出的信號作為后續(xù)整個系統(tǒng)的復位信號;

其對應(yīng)的代碼如下:

module test(

input sys_clk, //系統(tǒng)時鐘信號

input async_rst_n, //外部輸入的復位信號

input din, //輸入的數(shù)據(jù)信號

output reg dout //輸出的數(shù)據(jù)信號

);

reg sync_rst_n1; //第一級觸發(fā)器輸出

reg sync_rst_n2; //第二級觸發(fā)器輸出,經(jīng)釋放同步后的復位信號

always@(posedge sys_clk or negedge async_rst_n)begin

if(!async_rst_n)begin

sync_rst_n1 <= 1'b0;

sync_rst_n2 <= 1'b0;

end

else begin

sync_rst_n1 <= 1'b1;

sync_rst_n2 <= sync_rst_n1;

end

end

always@(posedge sys_clk or negedge sync_rst_n2) begin

if(!sync_rst_n2)

dout <= 1'b0;

else

dout <= din;

end

endmodule

綜合后的電路圖如圖所示:

接下來,對該電路進行仿真分析,看看是如何異步復位、同步釋放的。testbench文件如下:

`timescale 1ns/1ps

module test_tb;

reg sys_clk; //系統(tǒng)時鐘信號

reg async_rst_n; //外部輸入的復位信號

reg din; //輸入的數(shù)據(jù)信號

wire dout; //輸出的數(shù)據(jù)信號

test test_u1(

.sys_clk(sys_clk), //系統(tǒng)時鐘信號

.async_rst_n(async_rst_n), //外部輸入的復位信號

.din(din), //輸入的數(shù)據(jù)信號

.dout(dout) //輸出的數(shù)據(jù)信號

);

always #10 sys_clk = ~sys_clk;

initial begin

sys_clk = 0;

async_rst_n = 0;

din = 1;

#19;

async_rst_n = 1;

#99;

async_rst_n = 0;

#34;

async_rst_n = 1;

#97;

async_rst_n = 0;

#3;

async_rst_n = 1;

#71;

async_rst_n = 0;

#16;

async_rst_n = 1;

#200;

$stop;

end

endmodule

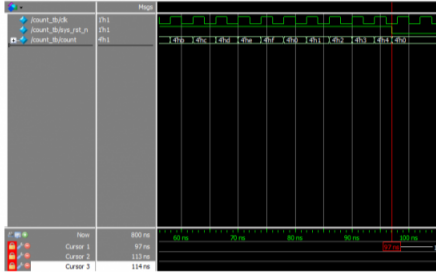

當然了,我只是簡單的仿真一下,也許寫的testbench并不是很好,能說明問題即可,仿真圖如下圖所示:

上圖中,很明顯的可以看出,異步復位信號(低電平)到來時,dout立馬變?yōu)?,但是在復位信號釋放后延遲兩個周期,到第三個周期才真正的恢復到工作狀態(tài);這跟我們一開始使用的兩級觸發(fā)器對釋放信號進行同步有關(guān)系。

異步復位和同步釋放,其實可以分開來看,單純的理解為兩個信號來控制著整個系統(tǒng)。同步釋放信號相對于外部復位信號的釋放總是存在一定的延遲,不過延遲很小,也就兩個周期,實際中也是可以接受的。

關(guān)于復位電路的設(shè)計就暫時說到這里,不過好像沒有說完,還有關(guān)于配置PLL之后的系統(tǒng)復位電路怎么設(shè)計等等,以后再詳細討論

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603009 -

亞穩(wěn)態(tài)

+關(guān)注

關(guān)注

0文章

46瀏覽量

13268 -

復位電路

+關(guān)注

關(guān)注

13文章

322瀏覽量

44586 -

時序分析

+關(guān)注

關(guān)注

2文章

127瀏覽量

22565

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA和CPLD內(nèi)部自復位電路設(shè)計方案

fpga設(shè)計實戰(zhàn):復位電路仿真設(shè)計

Xilinx FPGA入門連載17:PWM蜂鳴器驅(qū)動之復位與FPGA重配置功能

復位電路設(shè)計選型指南

FPGA的理想的復位方法和技巧

FPGA怎么搭復位電路 fpga復位電路設(shè)計方案

實現(xiàn)FPGA實戰(zhàn)復位電路的設(shè)計和仿真

FPGA內(nèi)部自復位電路設(shè)計方案

復位電路設(shè)計分析

FPGA復位的8種技巧

FPGA入門之復位電路設(shè)計

FPGA入門之復位電路設(shè)計

評論