人工智能和機器學習正在迅速滲透到廣泛的設備中,推動了SoC設計的重新架構,需要更多的內存空間和更高的帶寬來傳輸和處理數據。這種變化需要更高速的接口和更寬的總線,為最新 PCIe 協議規范的增強以及升級 PIPE(PCI Express 的 PHY 接口)規范作為首選 PHY 接口鋪平了道路。

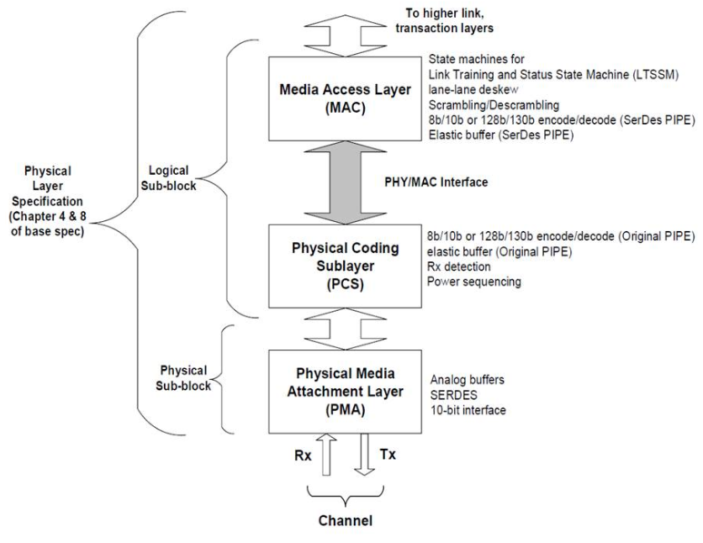

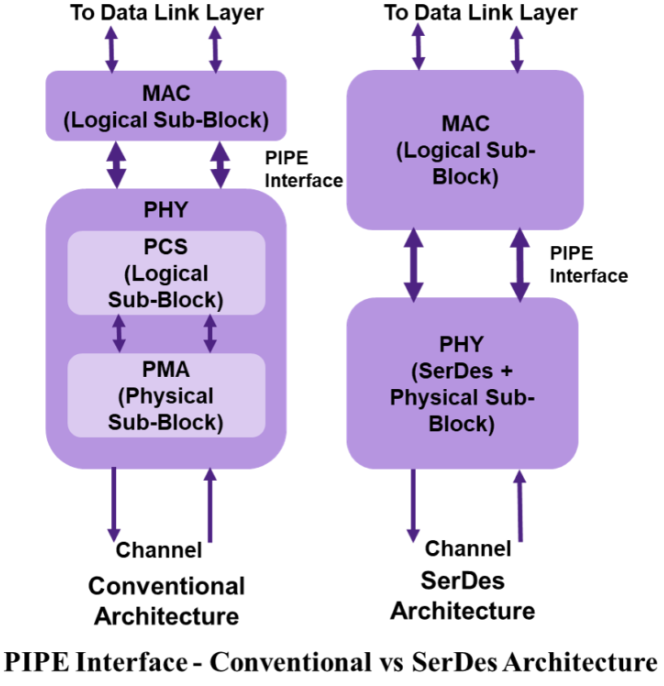

PIPE 規范已發展到版本 5.1.1,不僅是為了匹配最新的規范,而且還是為了擴展協議中的未來增強功能。SerDes 架構使 PIPE 5 PHY 協議不可知,所有協議特定邏輯都轉移到控制器。這簡化了PHY設計,并允許不同的協議棧輕松共享。用于 PIPE 接口的 SerDes 架構通過對物理編碼子層 (PCS) 和媒體訪問層 (MAC) 的職責進行一些關鍵更改以及對信令接口的更新來實現可擴展性。

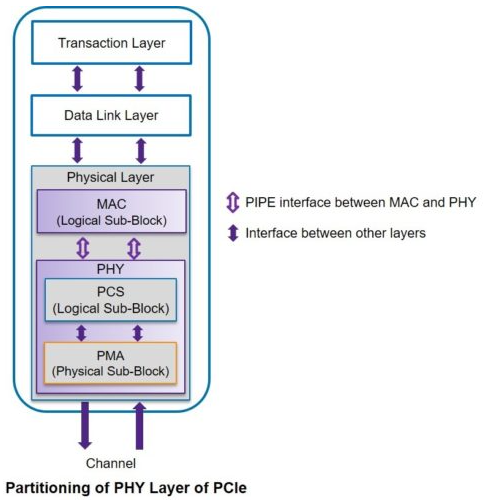

圖 1:PCI Express 的分區 PHY 層

PIPE 5.1規范除了SerDes架構和低引腳數接口之外,還有一些額外的更新。以下列表總結了 PIPE 5.1 中的主要升級:

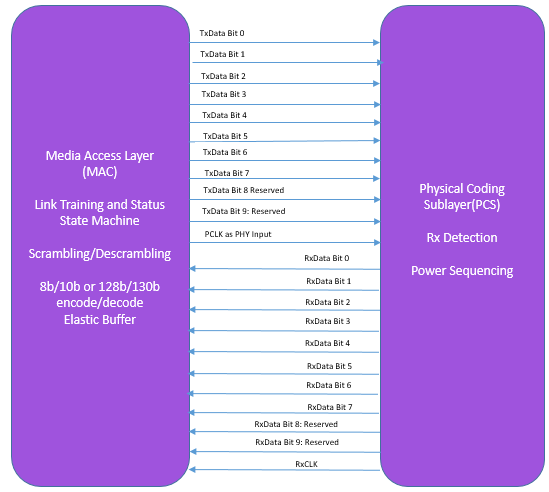

? 由 MAC 執行 8b/10b 或 128b/130b 編碼/解碼 ? 彈性緩沖區控制由 MAC 維護,RxStatus 僅用于接收器檢測目的

? PHY 在由“RxWidth”

確定的管道寬度上呈現與恢復時鐘“RxClk”同步的 RxData ? RxPolarity 場不再用于 SerDes 架構,MAC 負責反相接收器極性

? 由 MAC

執行環回 ? 新的支持的 64 位數據寬度,專門用于 SerDes 架構

? PIPE 數據寬度為 10/20/40 位,而不是 8/16/32

隨著 SerDes 架構帶來的所有變化,調試和理解接口上 PIPE 數據的新格式變得具有挑戰性。具體來說,新的PIPE寬度和編碼器/解碼器到MAC的轉移導致PIPE接口上的數據看起來與以前的任何PIPE版本大不相同。當您繼續閱讀時,您將看到我們如何嘗試將數據分解為更小的單元,以清楚地顯示如何通過界面交換信息。

TxData/RxData 信號寬度為 10 位倍數 (80/40/20/10)。對于 8b/10b 編碼,每 10 位攜帶 10b 編碼數據。在 128b/130b 編碼時,每 10 位攜帶 8 位數據,保留上兩位。

圖 2:跨 PIPE SerDes 架構的數據傳輸

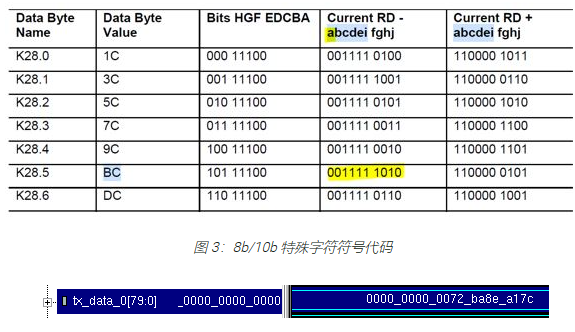

讓我們看一下下圖中在 1 位 PIPE 寬度上以 Gen2/Gen40 速度傳輸的 COM 符號。COM (8) 的 10b/0011111010b 編碼值占用 TxData 的所有位 [9:0]。

位 'a' (來自 'abcdeifghj') 應該首先進入接口,所以它將是 17c。

請注意,2c 中剩余的 17 位(即 0001 0111 1100)對應于下一個符號。

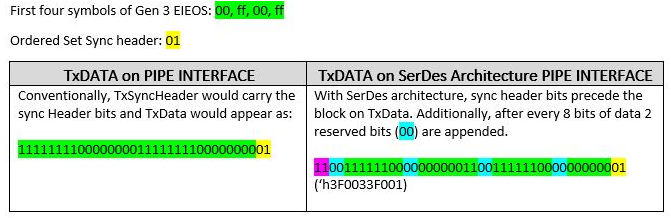

現在讓我們看一下塊編碼數據。在 TxData/RxData 上呈現數據時,每個 8 位切片中僅使用 10 位,并保留上兩位。考慮 3 位管道接口上的第 40 代電氣空閑有序集 (EIEOS)。

? 編碼在塊前面添加 2 個同步標頭位。請注意,它們是TxSyncHeader和RxSyncHeader。

SerDes架構正在全面迅速采用。隨著 PIPE 規范的不斷發展,復雜 PCI Express 控制器和 PHY 的設計和驗證周期將變得更加復雜和耗時。Synopsys PCI Express VIP 完全支持 PIPE 5.1,并提供成熟全面的驗證解決方案。

審核編輯:郭婷

-

人工智能

+關注

關注

1791文章

47350瀏覽量

238759 -

機器學習

+關注

關注

66文章

8422瀏覽量

132714

發布評論請先 登錄

相關推薦

GMII、SGMII和SerDes的差異總結

申請TI Keystone DSP PCIe SerDes IBIS-AMI Models。

請教關于C6678的serdes模塊

請問Virtex7 GTX如何生成PIPE接口PCIE PHY?

axi_pcie3_0編譯的解決辦法?

SerDes協議簡析

參考時鐘對SERDES性能的影響

了解PIPE4.4規范及PCIe 4.0的開發設計

在Arria 10 PCI Express中更改串行和PIPE仿真的方法

適用于PCIe 5.1、DP 1.5、USB 0.1、SATA和未來協議的PIPE 4.3.2

PCIe PIPE 4.4.1:PCIe Gen4的推動者

PCIe 5.0 SerDes 測試

揭秘PCIe PIPE 5.1 SerDes架構

揭秘PCIe PIPE 5.1 SerDes架構

評論