預(yù)計在不久的將來,數(shù)十億的互聯(lián)網(wǎng)連接設(shè)備和數(shù)據(jù)密集型實時應(yīng)用程序?qū)⒊霈F(xiàn)在市場上,而當(dāng)今數(shù)據(jù)中心常見的100千兆以太網(wǎng)(GE)速度將不足以處理帶寬。因此,我們已經(jīng)預(yù)計數(shù)據(jù)中心運營商需要將其網(wǎng)絡(luò)從100 GE遷移到400 GE,從而產(chǎn)生對更快內(nèi)存和更快串行總線通信的需求。

PCIe 是用于點對點通信的高速差分串行標(biāo)準(zhǔn)。每一代 PCIe 標(biāo)準(zhǔn)都提供比上一代產(chǎn)品更多的功能和更快的數(shù)據(jù)傳輸速率。最新一代 PCIe 5.0 將使 PCIe 4.0 的吞吐率翻倍。PCIe 5.0 的傳輸速率為每秒 32 千兆傳輸 (GT/s),而 PCIe 16.4 支持的傳輸速率為 0 GT/s。PCIe 64.5 具有每秒 0 千兆字節(jié) (GB/s) 的單向傳輸帶寬,以 128 GB/s 的雙向流量提供數(shù)據(jù)。

除了將帶寬翻倍外,PCIe 5.0 還提供其他新功能,例如:

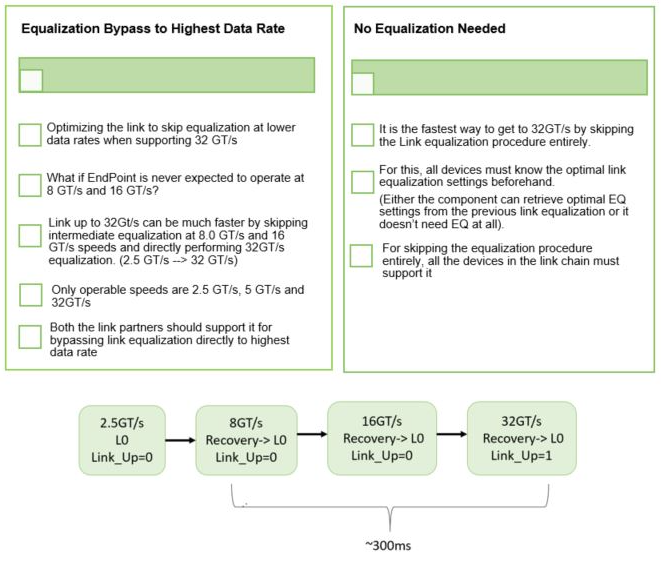

? 均衡旁路模式,可加快鏈路初始化速度

? 允許備用協(xié)議通過鏈路訓(xùn)練

進(jìn)行協(xié)商 ? 預(yù)編碼支持,幫助避免突發(fā)錯誤

? 環(huán)回增強(qiáng)功能允許模擬串?dāng)_行為

在本博客中,我們將介紹 32 GT/s 時的 PHY 邏輯變化,并介紹均衡過程中發(fā)生的主要變化。

但是,在深入研究新的均衡模式之前,讓我們先談?wù)劄槭裁次覀冃枰履J?.....

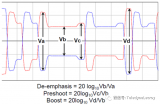

數(shù)據(jù)速率的提高也意味著信號衰減的增加,這對更高頻率的分量影響最大。這最終會導(dǎo)致失真,需要通過均衡程序進(jìn)行補(bǔ)償。與 PCIe 3.0 和 4.0 一樣,對于以 32GT/s 運行的設(shè)備,建議使用均衡來調(diào)整發(fā)射器和接收器設(shè)置以提高信號質(zhì)量。PCIe 0.1 的均衡階段(階段 2、3、5、0)與前幾代相同。

讓我們看一下啟動鏈接到 32 GT/s 所涉及的步驟。鏈路最初必須以 0.2 GT/s 的速度訓(xùn)練到 L5,然后依次以 8.0 GT/s、16 GT/s 和 32 GT/s 的速度進(jìn)行均衡。這被稱為傳統(tǒng)的“完全均衡”模式。

隨著數(shù)據(jù)速率越來越高,這種方法變得越來越耗時,并增加了鏈路啟動的延遲。根據(jù)一些供應(yīng)商的說法,具有均衡功能的單速轉(zhuǎn)換大約需要~100ms,這意味著啟動到300GT / s的鏈路需要~32ms。優(yōu)化鏈路啟動的需求導(dǎo)致引入了兩種新的可選模式:

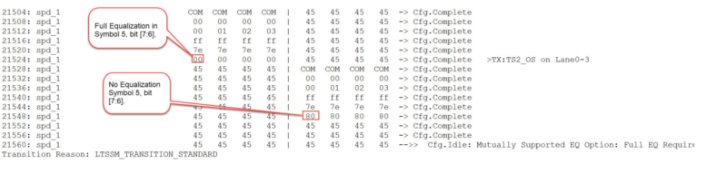

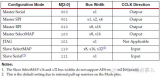

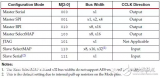

為了方便這些可選的均衡模式,修改了 TS OS 的 Symbol5(訓(xùn)練控制)。鏈路均衡模式由配置狀態(tài)中通告的相互支持的 EQ 模式?jīng)Q定

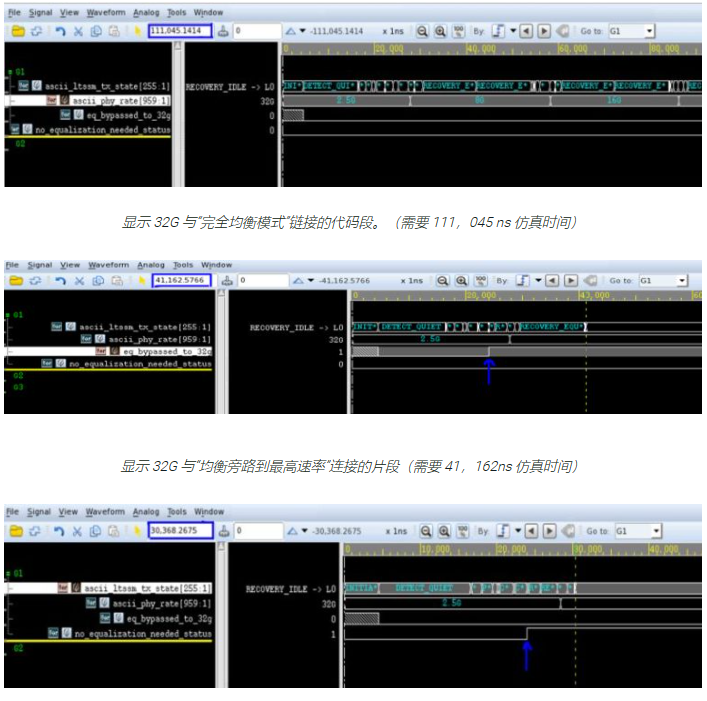

以下是 Synopsys 內(nèi)部模擬的一些片段,顯示了不同均衡模式下高達(dá) 32GT/s 的連接時間

顯示 32G 連接“無需均衡”模式的代碼片段(需要 30,368 ns 仿真時間)

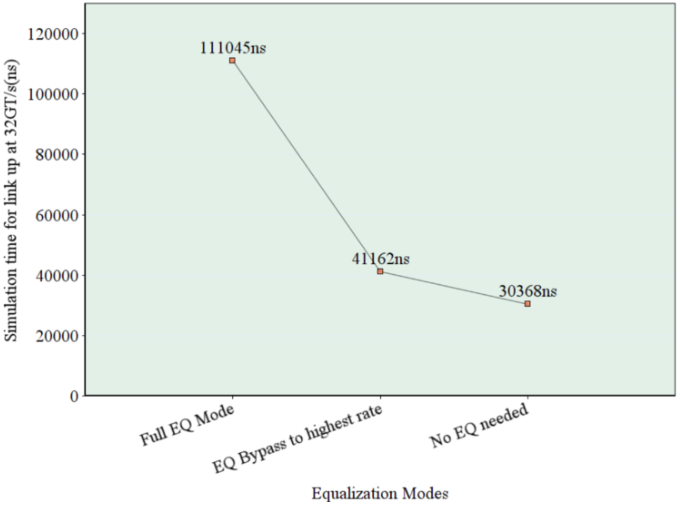

下圖顯示了如何通過新的均衡模式大幅縮短至32GT/s的鏈路啟動時間:

Synopsys PCIe 5.0 VIP 完全符合最新的 PCIe 5.0 規(guī)范。我們的VIP有助于解決鏈路均衡的主要驗證挑戰(zhàn),以確保LTSSM在上圖中列出的所有三種均衡模式下正確轉(zhuǎn)換。選擇可選的均衡功能支持,允許覆蓋整個LTSSM狀態(tài)范圍,以及連接期間的速度轉(zhuǎn)換可能性都是完全可配置的。用戶還可以配置預(yù)設(shè)、預(yù)設(shè)提示或系數(shù)等。以確保 DUT 可以正確執(zhí)行鏈路均衡。

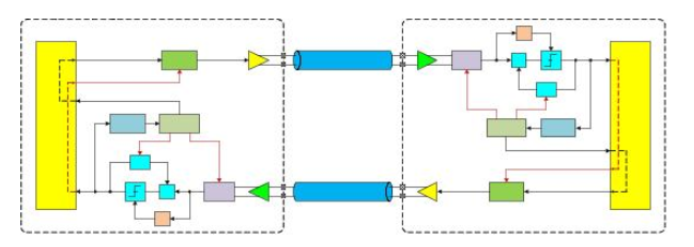

Synopsys VIP 和測試套件提供完整的解決方案,其中包含一系列測試,以驗證 PCIe 5.0 均衡功能的各種類型的 DUT(EP DUT、RC DUT、PHY DUT 和重定時 DUT)。

審核編輯:郭婷

-

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5419瀏覽量

171602 -

數(shù)據(jù)中心

+關(guān)注

關(guān)注

16文章

4761瀏覽量

72034 -

PCIe

+關(guān)注

關(guān)注

15文章

1234瀏覽量

82584

發(fā)布評論請先 登錄

相關(guān)推薦

PCIe Gen3/Gen4接收端鏈路均衡測試(上篇:理論篇)

使用Zynq設(shè)備和Tandem配置的PCIe BOOTUP時間有什么要求?

PCIe 3.0/4.0的鏈路均衡的工作原理

從Bootloader的角度探討如何優(yōu)化進(jìn)而縮短啟動時間

電機(jī)啟動時間一般是多久?怎么縮短啟動時間呢?

Xilinx7系列基于PCIe的設(shè)計如何滿足PCIe啟動時間的要求

基于FPGA的PCIe設(shè)備如何才能滿足PCIe設(shè)備的啟動時間的要求?

什么是 PCIe 5.0? PCIe 5.0規(guī)范以及挑戰(zhàn)

[PCIe] [電源管理] 面向硬件的ASPM鏈路狀態(tài)和L1子狀態(tài)

![[<b class='flag-5'>PCIe</b>] [電源管理] 面向硬件的ASPM<b class='flag-5'>鏈</b><b class='flag-5'>路</b>狀態(tài)和L1子狀態(tài)](https://file.elecfans.com/web1/M00/D9/4E/pIYBAF_1ac2Ac0EEAABDkS1IP1s689.png)

開關(guān)電源啟動性能檢測之啟動時間測試方法

在i.MXRT1xxx系列上用NAND型啟動設(shè)備時可用兩級設(shè)計縮短啟動時間

影響晶振啟動時間的因素

調(diào)試PCIE鏈路動態(tài)均衡介紹

PCIe 5.0均衡模式:縮短鏈路啟動時間

PCIe 5.0均衡模式:縮短鏈路啟動時間

評論