正在尋找縮短調試周期的方法,以快速從根本上解決內存控制器/PHY 和子系統驗證項目中的問題?

在某些時候,您在調試內存模型時很可能面臨以下挑戰之一(計時問題、日志消息、銀行統計信息、分層調試等)。

Synopsys 內存模型 (VIP) 與 Verdi 一起可提高整體調試效率。以下是緊密耦合的調試解決方案如何幫助解決一些痛點的示例:

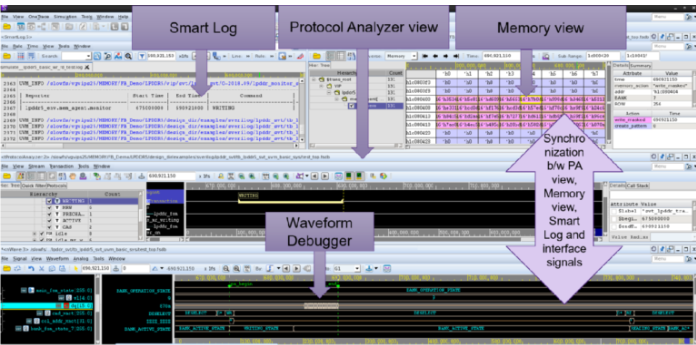

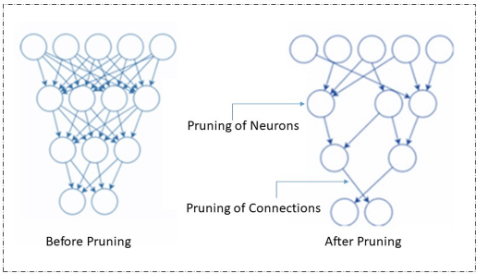

以協議為中心的調試使用戶能夠快速了解協議活動,識別瓶頸并快速查找和調試意外行為

協議視圖中的錯誤、警告和消息注釋可快速確定原因

交易、銀行狀態、內存內容和握手的圖形視圖,可立即訪問特定于上下文的詳細信息

鎖定步驟鏈接到模擬器跟蹤視圖(波形),可在任何抽象級別輕松調試

以下是其他示例,其中包含詳細說明供您參考:

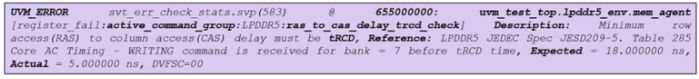

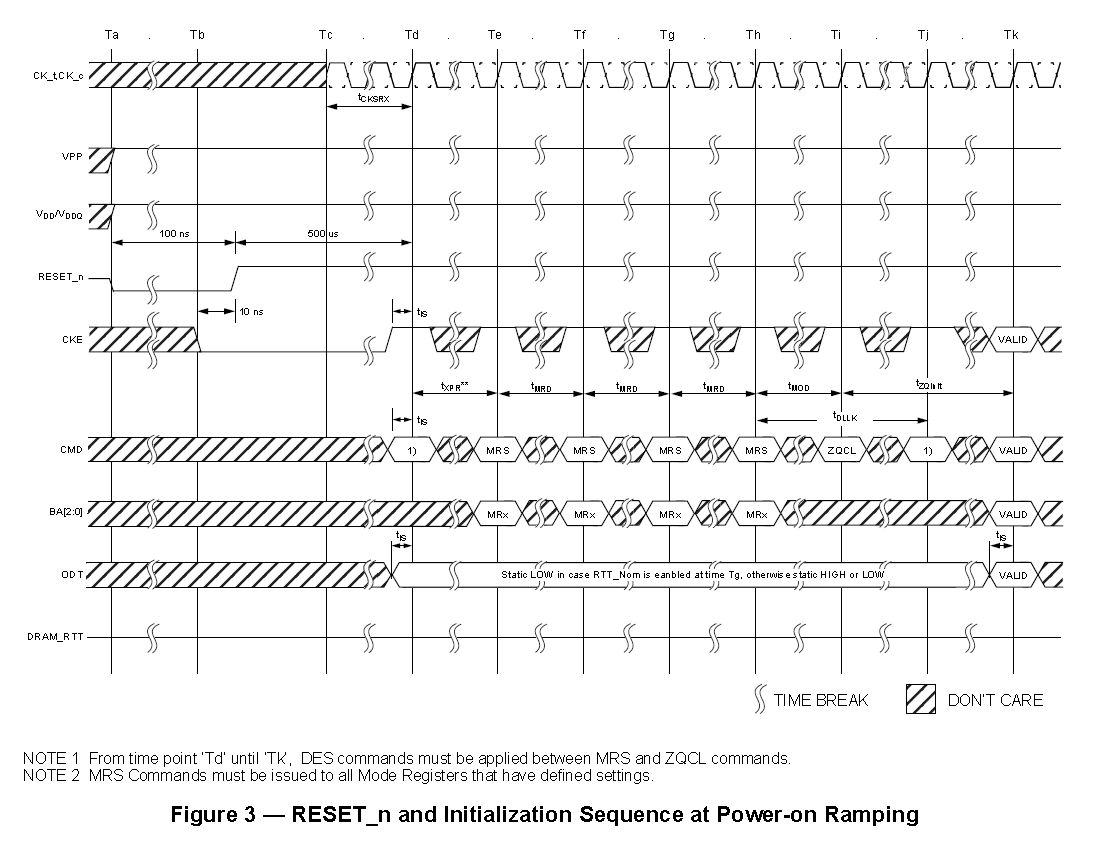

協議和計時沖突: 當內存VIP檢測到協議/時序沖突時,通知將顯示有關被破壞的規范部分的所有命令性信息,包括報告錯誤的組件,協議版本以及針對預期的規范定義值應采取的糾正措施。

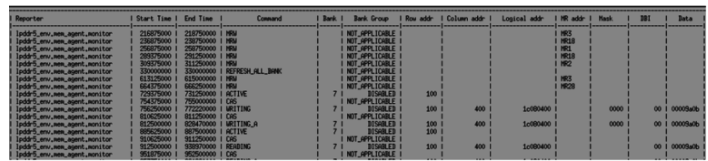

跟蹤文件: 跟蹤是特殊的文本文件,其中包含有用的信息,例如事務的開始/結束時間和命令名稱等。例如,如果命令是“模式寄存器”,則會顯示與“模式寄存器”字段相關的所有信息,例如讀/寫命令、相關地址、數據和重要信息,如延遲、DBI、DM 和模式寄存器設置。

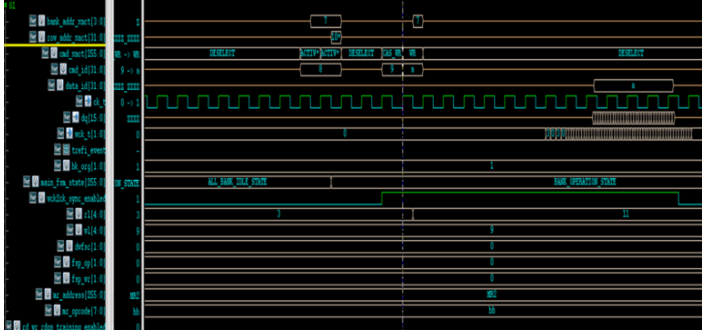

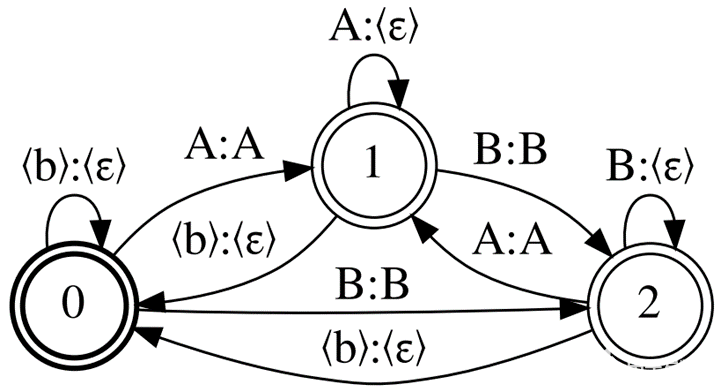

調試端口:它們在高度抽象中提供了協議流量的可視化表示,例如在哪個銀行執行交易、編程模式寄存器值、銀行狀態、命令和數據 ID 標記以將數據與相應的命令相關聯,以及其他功能。調試端口作為 Synopsys 內存 VIP 接口的一部分提供,并可加載到波形查看器(如 Verdi)上。

威爾第協議分析器流程:這提供了交易、銀行狀態、內存內容的配置設置、模擬等的圖形可視化。通過同步視圖,用戶只需單擊ERROR消息,相應的牽引,內存地址位置和信號電平流量信息等詳細信息將突出顯示給用戶。

Synopsys Memory VIP 獨特、靈活的架構使其可以輕松插入任何基于 Verilog/SV/UVM/VMM 的測試平臺設置。

審核編輯:郭婷

-

寄存器

+關注

關注

31文章

5336瀏覽量

120260 -

內存

+關注

關注

8文章

3020瀏覽量

74012 -

模擬器

+關注

關注

2文章

875瀏覽量

43211

發布評論請先 登錄

相關推薦

物理內存模型的演變

調試準備怎么減少時間

嵌入式減少調試時間的3個技巧

用于快速模型的模型調試器11.20版用戶指南

Elastos內存管理對軟件調試的支持

減少調試時間的 3 個技巧

更改CTC規則以減少訓練和解碼中的內存消耗

簡化內存模型的調試

嵌入式軟件開發之如何減少調試時間

如何減少內存模型調試時間

如何減少內存模型調試時間

評論