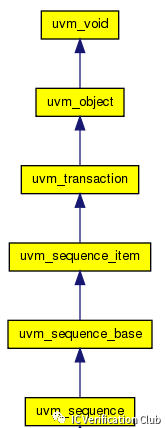

引入sequence的原因:

- 將 生成測試case的語句 從 main_phase 中獨立出來,使得使用不同測試用例時,只需要修改sequence部分即可,而不用關注 UVM剩余部分。(提高剩余部分的可復用性)。

引入sequence的仲裁機制的原因:

- 一個sequencer上通過fork...join可以啟動多個sequence,而多個sequence按照什么順序啟動需要一定的仲裁機制來控制,具體而言主要從兩個角度控制

- sequence角度:自身的優先級、原子性、有效性

- sequencer角度:對多個sequence的仲裁算法

引入sequence相關宏的原因:

- 更方便地控制transaction的產生過程,主要有:

- uvm_do系列宏:實例化transaction+將transaction交給sequencer(對應start_item與finish_item任務)

- uvm_create宏:實例化transaction,可用new代替

- uvm_send宏:將transaction交給sequencer(對應start_item與finish_item任務)

- uvm_rand_send系列宏:對transaction進行隨機化+將transaction交給sequencer(對應start_item與finish_item任務)

不同類型sequence共用sequencer的方法(一個driver):

- transaction類型例化的一個sequencer 對應 多個不同約束的transaction包

- 可以通過一個sequence啟動其他sequence(即嵌套的sequence),然后間接生成多個不同約束的transaction包 —— 注意:這里使用了cseq. start ( m_sequencer );這樣的語句

- 也可以通過一個sequence直接生成多個不同約束的transaction包

- 通過類型轉換,實現同一個sequencer處理不同兩個截然不同的transaction,步驟如下

- 將sequencer和driver能夠接受的數據類型設置為uvm_sequence_item

- driver中使用時,使用cast將uvm_sequence_item轉換為各自transaction的類型

補充:start任務參數說明 seq0.start(env.i_agt.sqr, null, 100);

- 第一個參數:sequencer的位置,指明seq0由哪個sequencer啟動

- 第二個參數:parent sequence

- 第三個參數:seq0的優先級

補充:m_sequencer是一個屬于每個sequence的成員變量,它指向執行當前sequence的sequencer句柄,其類型是uvm_sequencer_base。

sequencer向sequence傳遞變量(約束)的方法:

- 方法一:通過cast轉換將sequence內置變量m_sequencer(類型為uvm_sequencer_base)轉換成my_sequencer類型, 然后引用uvm_sequencer中的成員變量作為約束

- 方法二:在sequence中使用`uvm_declare_p_sequencer(my_sequencer),然后通過宏默認生成的變量p_sequencer來引用uvm_sequencer中的成員變量作為約束

補充:uvm_declare_p_sequence的實質是在base_sequence中聲明了一個成員變量p_sequencer,并將其指向啟動本sequence的sequencer。

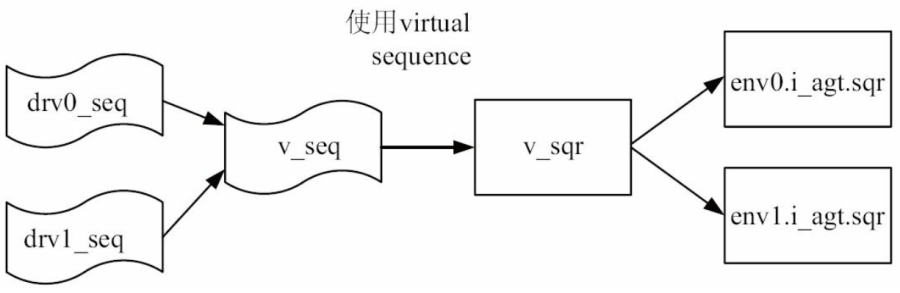

發往不同driver的sequence之間的同步的方法:

- 方法一:通過全局事件進行簡單同步:在drv0_seq中觸發事件,在drv1_seq中等待這個全局事件。

- 方法二:使用 virtual sequence+virtual sequencer,可以實現類似crossbar的連接,且因為virtual sequence的body是順序執行,所以可以輕松實現整體順序(同步),局部并行的效果。

補充:verilog中事件的基本使用

- event變量聲明為:

- event var;

- event觸發為:

- ->var;

- 捕獲觸發為:

- @(var);

sequence library的概念:

- 派生自uvm_sequence,就是一系列sequence的集合,它會根據特定的算法隨機選擇注冊在其中的一些sequence, 并在body中執行這些sequence。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

UVM

+關注

關注

0文章

182瀏覽量

19193 -

sequence

+關注

關注

0文章

23瀏覽量

2852

發布評論請先 登錄

相關推薦

數字IC驗證之“搭建一個可以運行的uvm測試平臺”(5)連載中...

的transaction,以及創建用于產生事物的事物發生器sequence。 在uvm驗證平臺中穿梭各個組件之間的基本信息單元是一個被稱為transaction的數據對象,也就是我們前面所說的事物

發表于 01-26 10:05

UVM sequence分層有哪幾種方式呢

種請求下可以使用第一種分層方式,在high-layer sequence中依然使用low-layer sequencer進行驅動,同時對low-layer sequence進行更加精細化的控制

發表于 04-11 16:37

請問一下在UVM中的UVMsequences是什么意思啊

在UVM方法學中,UVMsequences 是壽命有限的對象。UVM sequences從uvm_sequence_item基類擴展得到,uvm_s

發表于 04-11 16:43

UVM sequence分層的幾種體現

種請求下可以使用第一種分層方式,在high-layer sequence中依然使用low-layer sequencer進行驅動,同時對low-layer sequence進行更加精細化的控制。在上面

發表于 04-14 11:08

如何配置sequence的仲裁算法和優先級及中斷sequence的執行

01 Arbitrary在UVM中,多個sequence可以同時被綁定到相同的sequencer并啟動。這種測試場景在實際中是存在的,比如在模擬同一個總線master口上的不同類型的數

發表于 09-23 14:35

sequence item實際應用中應該包含哪些東西

展開。Sequence item是游走在Sequence-Sequencer-Driver這一基本結構中的數據結構類型,在有些地方也直接叫transaction,可以說是UVM的必用品

發表于 09-23 14:42

UVM中seq.start()和default_sequence執行順序

1. 問題 假如用以下兩種方式啟動sequence,方法1用sequence的start()方法啟動seq1,方法2用UVM的default_sequence機制啟動seq2。那

發表于 04-04 17:15

淺談UVM之sequence/item見解(上)

item指的是uvm_sequence_item, Sequence Item具備UVM核心基類所必要的數據操作方法,對于激勵的生成和場景控制,是由sequence來編織的,item應

UVM sequence機制中response的簡單使用

sequence作為UVM幾個核心機制之一,它有效地將transaction的產生從driver中剝離出來,并且通過和sequencer相互配合,成功地將driver的負擔降低至僅聚焦于根據協議將

UVM中add_typewide_sequence和add_sequence的區別

第2和第3種方式類似,第3種是一下子添加多個sequence,它內部原理就是調用第2種的函數,因此在本質上,只有第1和第2種這兩類區別。

在Sequencer上啟動一個Sequence

Sequencer默認不執行任何Sequence。驗證工程師可以通過調用start()啟動一個Sequence,也可以通過uvm_config_db指定一個自動啟動的Sequence。

UVM中sequence的那些事兒

UVM中sequence的那些事兒

評論