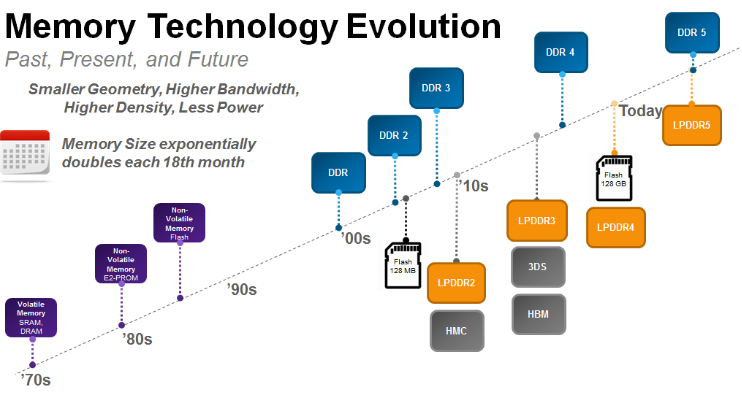

在存儲(chǔ)器密度低、性能緩慢且需要昂貴的硅空間的時(shí)代。然后我快進(jìn)到未來(lái),當(dāng)內(nèi)存技術(shù)已經(jīng)發(fā)展到支持巨大的密度,超快的速度,同時(shí)保持低功耗,所有這些都在非常小的幾何結(jié)構(gòu)中。

我概述了各種內(nèi)存技術(shù)及其支持的細(xì)分市場(chǎng)。為了跟上這種內(nèi)存技術(shù)發(fā)展的步伐,設(shè)計(jì)和驗(yàn)證工具以及創(chuàng)建和產(chǎn)品化這些技術(shù)的方法也得到了發(fā)展。

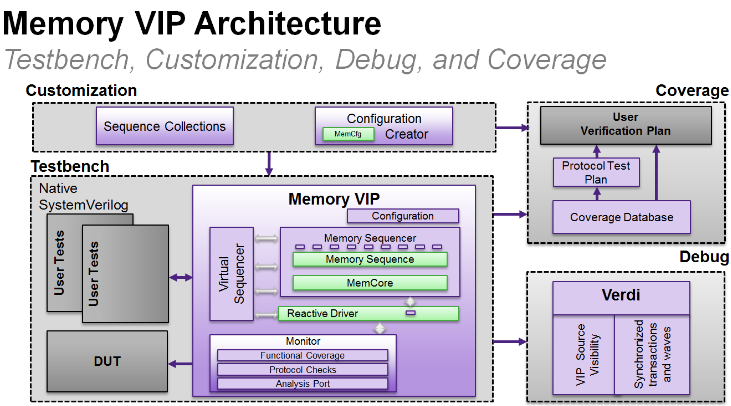

這種存儲(chǔ)器的演變給驗(yàn)證工程師帶來(lái)了一系列全新的挑戰(zhàn)。為了取得成功,驗(yàn)證必須在設(shè)計(jì)周期的早期發(fā)展為徹底、高效和有效。此外,它必須依賴(lài)于對(duì)SystemVerilog的本機(jī)支持,利用最先進(jìn)的驗(yàn)證技術(shù)進(jìn)行測(cè)試平臺(tái)創(chuàng)建和定制,以及調(diào)試和覆蓋率收斂。

需要更快、經(jīng)過(guò)驗(yàn)證且最先進(jìn)的前端內(nèi)存驗(yàn)證基礎(chǔ)設(shè)施來(lái)解決最新內(nèi)存創(chuàng)新帶來(lái)的復(fù)雜性。利用行業(yè)標(biāo)準(zhǔn)的通用驗(yàn)證方法 (UVM),支持高級(jí)協(xié)議級(jí)調(diào)試,以及具有內(nèi)置覆蓋范圍和計(jì)劃的加速驗(yàn)證收斂,驗(yàn)證工程師可以在短時(shí)間內(nèi)自信地驗(yàn)證內(nèi)存技術(shù)。

審核編輯:郭婷

-

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7636瀏覽量

166429 -

DDR

+關(guān)注

關(guān)注

11文章

731瀏覽量

66401 -

內(nèi)存

+關(guān)注

關(guān)注

8文章

3109瀏覽量

74999

發(fā)布評(píng)論請(qǐng)先 登錄

labview串口采集如何保持數(shù)據(jù)同步

2015高品質(zhì)開(kāi)關(guān)電源設(shè)計(jì)驗(yàn)證技術(shù)分享!

使用高級(jí)校準(zhǔn)技術(shù)驗(yàn)證收發(fā)器FPGA

Arm架構(gòu)內(nèi)存的加密與驗(yàn)證是在之前提到的memory filter上進(jìn)行的嗎

ESP-IDF內(nèi)核中的內(nèi)存管理如何驗(yàn)證?

DDR驗(yàn)證和調(diào)試的高級(jí)方法

華為NodeB采用的同步方式,失去同步源后可以保持的時(shí)間

Mentor Graphics 增加內(nèi)存模型,創(chuàng)建業(yè)內(nèi)首個(gè)完整的UVM SystemVerilog 驗(yàn)證 IP 庫(kù)

基于定理證明的內(nèi)存安全驗(yàn)證工具算法綜述

Linux進(jìn)程間共享內(nèi)存通信時(shí)如何同步?

簡(jiǎn)化內(nèi)存模型的調(diào)試

評(píng)論