Analysis port

每個組件通過其TLM接口與系統中的其他組件進行通信,用于給DUT發送激勵或者對DUT的行為進行響應。

然而,在任何絕大多數復雜的驗證環境中,特別是隨機驗證環境中,需要將收集到的transaction發送給環境的其他部分,以便進行端到端檢查(scoreboard)或收集接口覆蓋率。

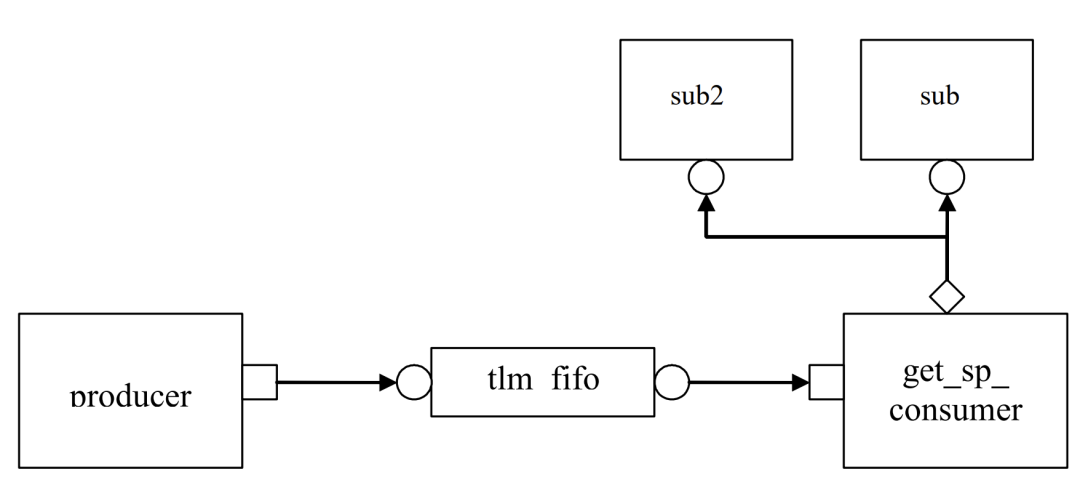

這兩種類型的TLM通信的區別在于,put/get ports通常需要一個相應的export來提供實現。對于analysis port來說,一個monitor能夠產生一個transaction而不用關心連接了哪些組件。各個不同的analysis components連接到monitoranalysis_port,以不同的方式處理transaction。

類比于,互聯網上看到同一個新聞,不同的人會產生不同的反應,有的人興高采烈,有的人捶胸頓足。這就是訂閱者模式。

uvm_analysis_port

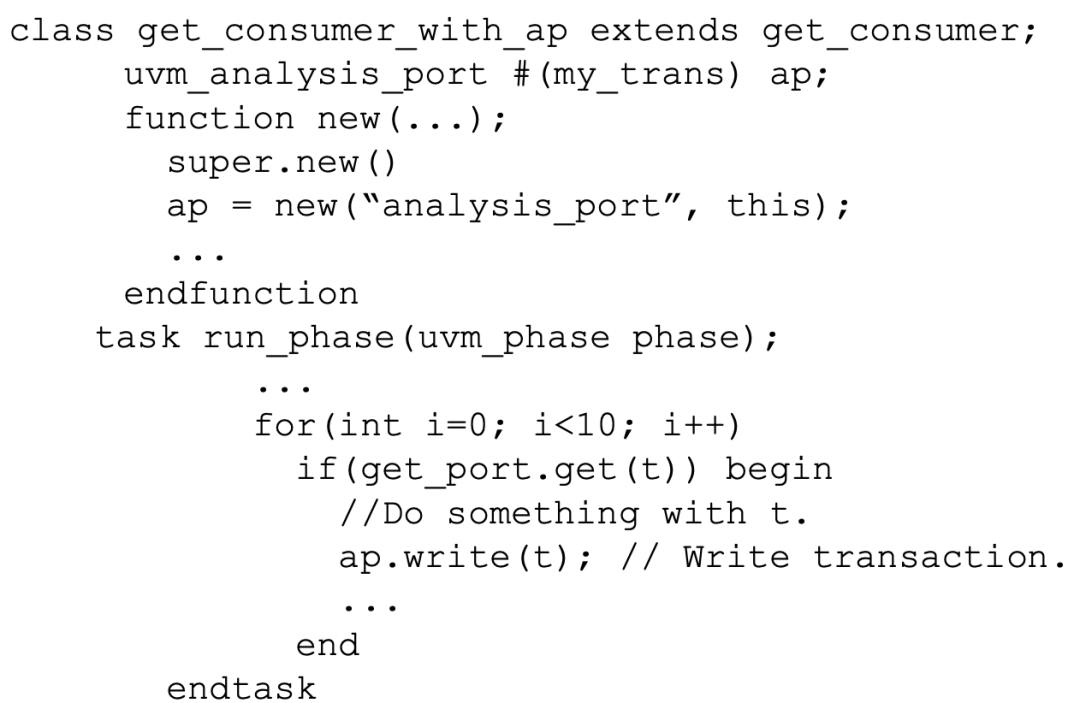

uvm_analysis_port是一個特別的TLM port,其接口包含一個函數 write()。

uvm_analysis_port包含一個連接到它的analysis_exports列表。當組件調用analysis_port.write()時,analysis_port會遍歷該列表并調用每個analysis_export的write()方法。如果沒有任何連接,write()的調用就直接返回。因此,一個uvm_analysis_port可以連接到0個、1個或者多個analysis_exports,但analysis_port.write()操作并不取決于連接的analysis_exports數量。

因為write()是一個void function,所以write()將總是在同一個delta cycle內完成,無論連接了多少個組件。

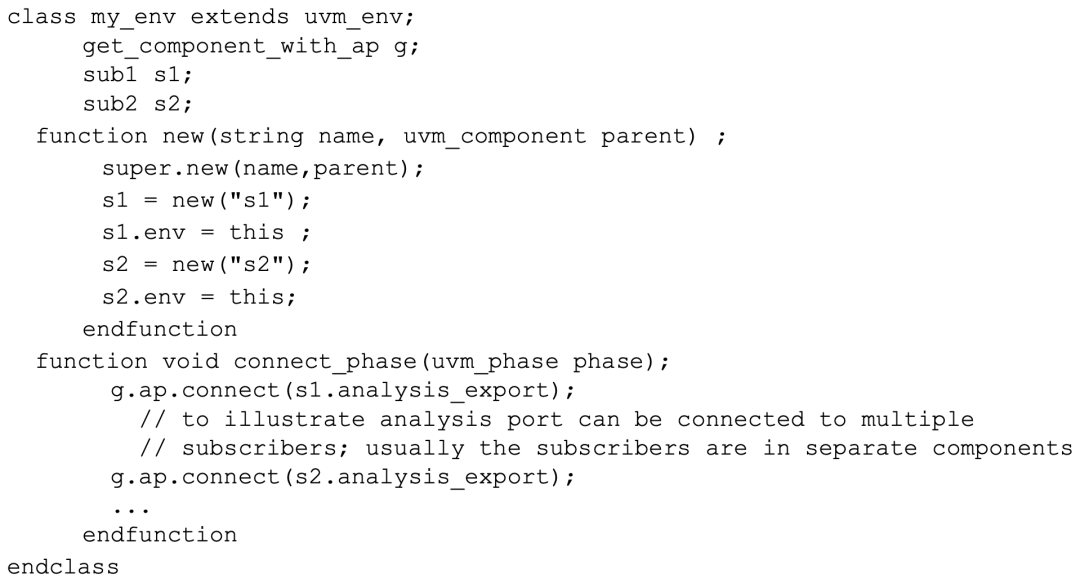

在上一層環境中,analysis port被連接到相應組件的analysis export,如coverage collectors和scoreboards等等。

Analysis Exports

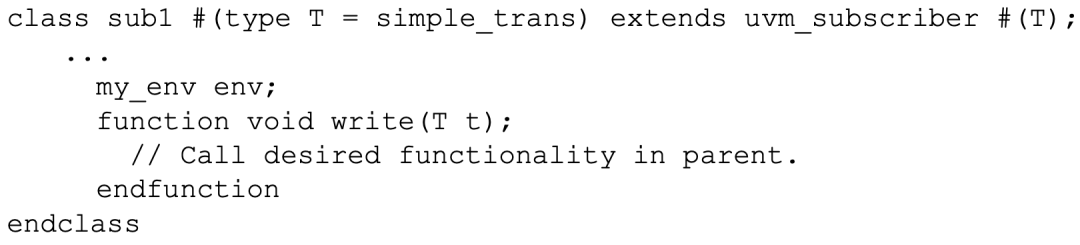

與其他TLM連接一樣,連接到analysis port的每個組件都要通過analysis_export提供write()的實現。

uvm_subscriber基礎驗證組件可以用來簡化這個操作 ,所以一個典型的 analysis component會擴展自uvm_subscriber:

與上面描述的put()和get()一樣,analysis port和analysis_export之間的TLM連接,需要允許analysis_export提供write()的實現。如果多個analysis_export被連接到一個analysisport,該端口將依次調用每個analysis_export的write()方法。

所有write()的實現都必須是function,analysisport的write()function會立即完成,不管連接到多少個analysis_export。

當多個uvm_subscriber連接到一個analysisport時,每個uvm_subscriber都被傳遞同一個transaction對象的指針,即write()調用的參數。每個write()的實現都必須copy這個transaction對象,然后對copy的對象進行操作,以避免破壞傳遞相同指針的其他transaction對象內容。

UVM還包括一個Analysis_fifo,它是一個包括analysis_export 的uvm_tlm_fifo,以允許blocking components訪問analysisport傳遞的transaction對象。

analysis_fifo是unbounded的,所以monitor的write()可以保證立即完成,然后,analysis組件可以隨意從analysis_fifo中獲取transaction。

-

UVM

+關注

關注

0文章

182瀏覽量

19189 -

TLM

+關注

關注

1文章

32瀏覽量

24761 -

Analysis

+關注

關注

0文章

17瀏覽量

10254

原文標題:UVM中的Analysis port

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

什么是uvm?uvm的特點有哪些呢

談談UVM中的uvm_info打印

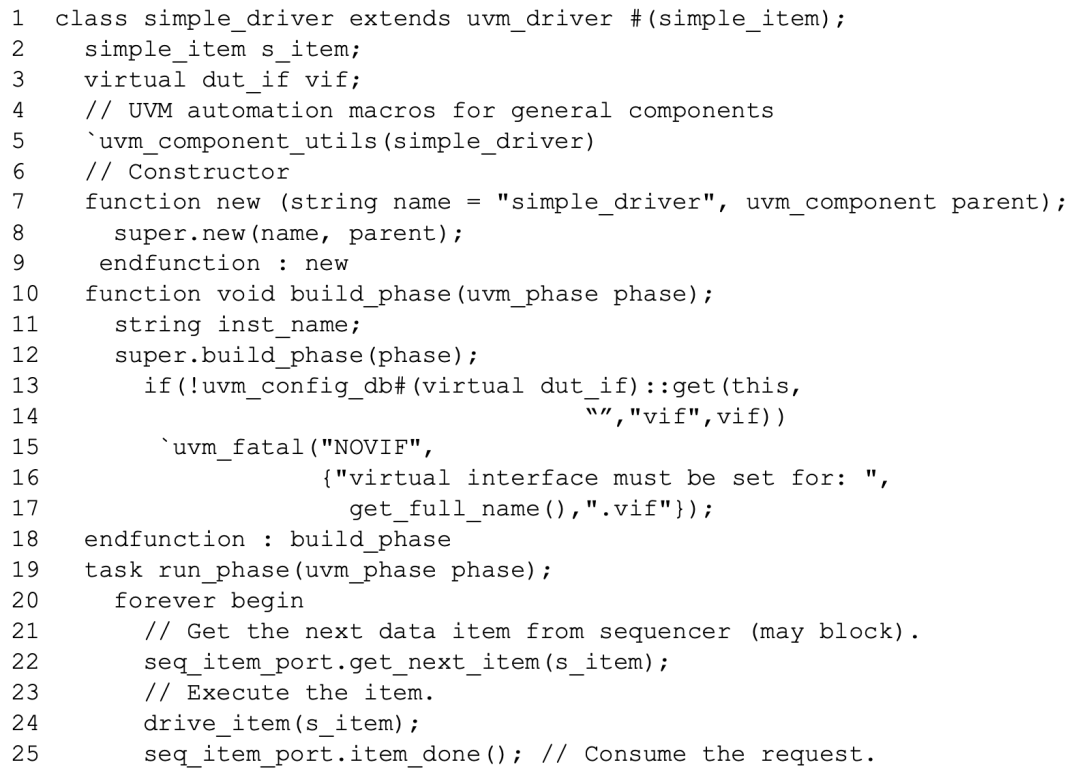

創建UVM Driver

深度剖析UVM中的Analysis port

深度剖析UVM中的Analysis port

評論