DDR 驗(yàn)證是任何 SoC 中最關(guān)鍵和最復(fù)雜的任務(wù)之一,因?yàn)樗婕拔挥?DUT 內(nèi)部的控制器和位于板載 DUT 外部的外部 DDR 存儲(chǔ)器。在這里,我們將討論 DDR VIP 模型的快速初始化。

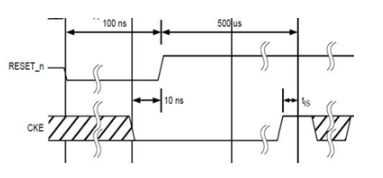

根據(jù) JEDEC 標(biāo)準(zhǔn) JESD79-4 第 3.3.1 節(jié),RESET_n需要至少維護(hù) 200us。在模擬時(shí)間中,此值很長(zhǎng)。此外,如果用戶(hù)的測(cè)試平臺(tái)違反此時(shí)間,Memory VIP 會(huì)將其標(biāo)記為UVM_ERROR并失敗模擬。即使此沖突被標(biāo)記為錯(cuò)誤,也不會(huì)影響 VIP 模型的行為。

有許多方法可以繞過(guò)此違規(guī)行為。在本博客中,我們將討論其中一種方式。

Synopsys Memory VIP 具有稱(chēng)為快速初始化的初始化功能,也稱(chēng)為按比例縮小初始化。此功能的目的是允許控制覆蓋初始化參數(shù)以加快初始化過(guò)程。新值(無(wú)論是默認(rèn)設(shè)置還是由用戶(hù)自定義)都可以縮短初始化時(shí)間,而不會(huì)斷言任何檢查器沖突。此外,它不會(huì)影響模型的初始化行為。此功能僅適用于前門(mén)訪(fǎng)問(wèn) - 與后門(mén)訪(fǎng)問(wèn)相比。我們將在后續(xù)的博客文章中討論內(nèi)存 VIP 訪(fǎng)問(wèn)的類(lèi)型。

有兩種方法可以縮小初始化參數(shù)。一個(gè)是使用默認(rèn)值設(shè)置的,另一個(gè)是自定義設(shè)置的。

根據(jù)標(biāo)準(zhǔn),以下是預(yù)期值:

min_cke_high_after_reset_deasserted_in_pu_and_res_init_time_ps = 500000000

min_reset_pulse_width_in_pu_ps = 200000000

使用默認(rèn)方法,可以從配置對(duì)象的build_phase調(diào)用函數(shù)“set_scaled_initialization_timings()”。該函數(shù)調(diào)用會(huì)將計(jì)時(shí)參數(shù)縮小到下面分配的值,而不會(huì)觸發(fā)檢查器沖突:

min_cke_high_after_reset_deasserted_in_pu_and_res_init_time_ps = 500000

min_reset_pulse_width_in_pu_ps = 200000

要自定義值,用戶(hù)可以設(shè)置自己的自定義值,然后設(shè)置標(biāo)志“scaled_timing_flag”。VIP 將配置為用戶(hù)提供的值。因此:

對(duì)于分立器件:

|

// cfg handle of the svt_ddr_configuration class // Pass the cfg to the DDR Discrete Device component by using // the config_db mechanism. cfg.timing_cfg.min_cke_high_after_reset_deasserted_in_pu_and_res_init_time_ps = 500000; cfg.timing_cfg.min_reset_pulse_width_in_pu_ps = 200000; cfg.timing_cfg. tPW_RESET_ps = 100000; cfg.timing_cfg.scaled_timing_flag = 1; |

對(duì)于內(nèi)存型號(hào):

|

// dimm_cfg is handle of svt_ddr_dimm_configuration foreach(dimm_cfg.data_lane_cfg[i]) begin foreach(dimm_cfg.data_lane_cfg[i].rank_cfg[j]) begin dimm_cfg.data_lane_cfg[i].rank_cfg[j].timing_cfg.min_cke_high_after_reset_deasserted_in_pu_and_res_init_time_ps = 500000; dimm_cfg.data_lane_cfg[i].rank_cfg[j].timing_cfg.min_reset_pulse_width_in_pu_ps = 200000; dimm_cfg.data_lane_cfg[i].rank_cfg[j].timing_cfg.tPW_RESET_ps = 100000; dimm_cfg.data_lane_cfg[i].rank_cfg[j].timing_cfg.scaled_timing_flag = 1; end end |

審核編輯:郭婷

-

控制器

+關(guān)注

關(guān)注

114文章

16912瀏覽量

182645 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7623瀏覽量

166214 -

DDR

+關(guān)注

關(guān)注

11文章

730瀏覽量

66308

發(fā)布評(píng)論請(qǐng)先 登錄

DDR3初始化問(wèn)題

6657的DDR3初始化不成功

如何從.mem文件初始化加密的ddr4內(nèi)存模型?

初始化封裝

手機(jī)模塊初始化向?qū)?/a>

ds1302時(shí)鐘芯片初始化,自動(dòng)決定DS1302是否需要初始化程序

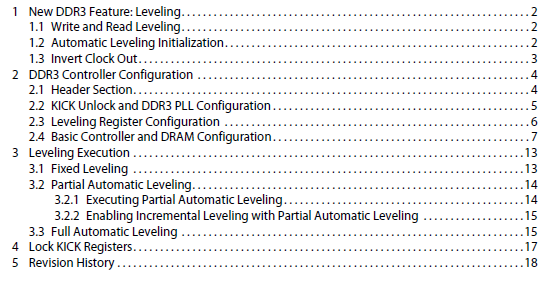

如何讓KeyStone DDR3接口初始化的詳細(xì)資料概述

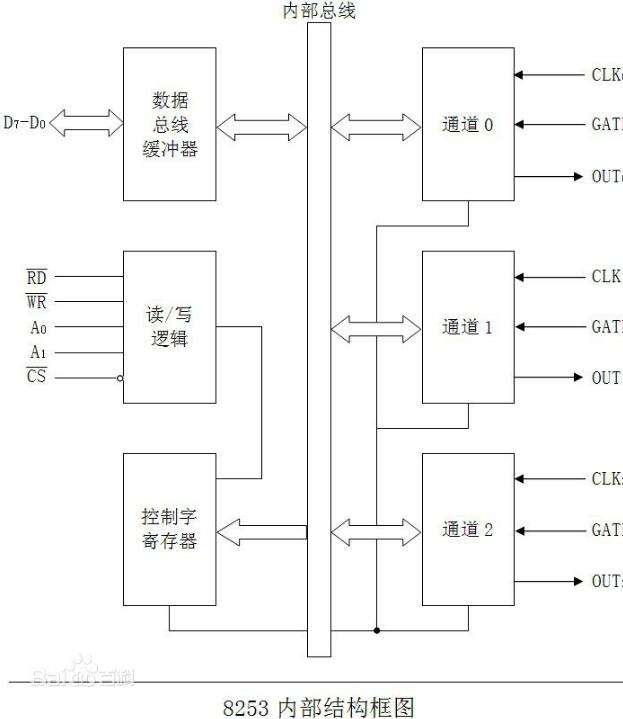

8253初始化程序分享_8253應(yīng)用案例

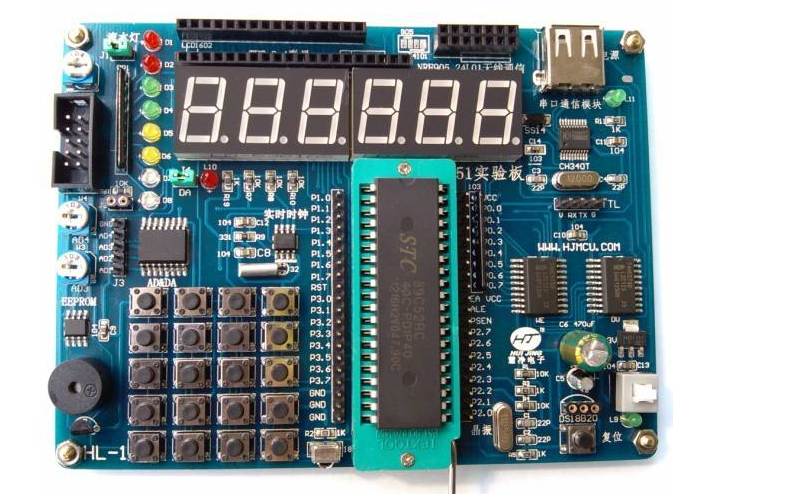

在51平臺(tái)下初始化文件的引入導(dǎo)致全局變量無(wú)法初始化的問(wèn)題如何解決

跳過(guò)DDR VIP模型的初始化

DDR4-初始化、訓(xùn)練和校準(zhǔn)

評(píng)論