驗證復雜的 SoC 需要付出很多努力。我們的用戶調查顯示,流片復雜SoC所涉及的工程資源中約有70%用于驗證,其中一半時間用于調試。

如果沒有經過深思熟慮的驗證環境,驗證團隊會浪費大量時間在 SoC 級別重新創建驗證環境以實現芯片級驗證,因為他們不考慮重用最初開發的環境來驗證其塊級 IP。即使跨相同的抽象級別,也無法重用相同的驗證IP和環境來支持仿真和仿真,也會導致延遲,并消耗不必要的工程資源。

能夠在整個 SoC 項目中一致地重用驗證環境,可顯著提高驗證效率。但是,要從這些生產力優勢中獲益,核查團隊需要仔細規劃其驗證過程所有階段的方法。

驗證范圍

通常,驗證團隊會開發單獨的流來支持塊和 SoC 級別的驗證。除了支持這些不同抽象級別之間的重用外,驗證環境還應可在驗證過程的不同階段重用,以最大程度地減少工作量。

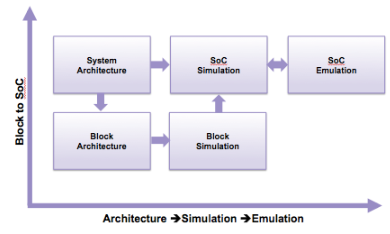

圖1:驗證光譜的兩個維度

每個設計的起點通常是系統架構,因為它定義了整體性能要求或約束。從設計和驗證的角度來看,目標應該是在后續階段重用這些性能約束,并確保設計在集成 RTL 和設計發展時繼續滿足這些約束。

例如,當系統架構師的約束(如總線吞吐量和延遲)已在塊級別進行驗證時,驗證團隊如何確保在 SoC 級別滿足這些約束?

為此,驗證團隊應旨在重用組件,通常是在塊和 SoC 級別監控這些約束的驗證 IP。驗證負責人必須提出具有通用方法、環境和驗證IP的測試平臺架構,該架構可在塊和SoC級別重用。當然,協議驗證 IP 必須能夠利用系統架構師提供的性能約束,并突出顯示整個系統互連中的任何違規行為。同時,為了最大限度地提高工作效率,團隊應確保為塊級驗證編寫的測試也能在 SoC 級別工作,并在模擬和仿真中工作。

一致性是關鍵

系統架構師最有可能使用事務級建模 (TLM) 技術。重用的關鍵是確保 API 在環境和抽象級別之間保持一致。例如,TLM API 應該與用于仿真的 C API 保持一致——無論團隊正在處理驗證流程的哪個階段。

每個 API 下的內容(驅動程序)對于每個環境都是唯一的,例如,用于模擬的 SystemVerilog 驅動程序和用于仿真的 RTL 驅動程序。無論 API 在驅動程序級別與什么接口,重用驗證 IP 的 API 的能力都是支持重用的關鍵。

支持塊到 SoC 重用

雖然一致的 API 支持在整個驗證范圍內重用,但 IP 到 SoC 重用是提高生產力的關鍵領域之一。它需要一種基于遵守最佳實踐準則、一致的驗證環境和一致的 VIP 的方法。

一致的語言和方法

在模塊和SoC級別以及所有驗證IP中使用通用語言(如SystemVerilog和UVM),可以更輕松、更快速地在每個級別集成和測試設計。

通用驗證計劃

再利用原則應盡可能擴大到核查計劃。在塊級別定義驗證計劃所做的工作應轉移到 SoC 級別。這應包括驗證團隊可以重用的功能覆蓋定義和測試。

共享功能覆蓋數據庫

在一開始就擁有一致的覆蓋率數據庫可以節省將多個專有數據庫手動合并為通用格式的大量時間。一致的數據庫將使驗證團隊能夠輕松快速地比較不同抽象級別的結果。

通用序列庫和調試

通過使用通用序列庫,能夠在模塊和SoC級別之間輕松重用激勵,這將提高驗證效率。

設計和驗證團隊在調試上花費了大量時間。在 SoC 級別發現錯誤時,工程師可能必須轉回 IP 級別來調查問題。能夠在單個通用調試環境中執行此操作,可以最大限度地減少團隊在學習和熟悉不同環境上花費的時間。

驗證團隊還可以從整個測試臺的可見性中受益。能夠在 IP 和 SoC 級別查看調試器代碼窗口中的事務,可以節省在不同調試環境之間切換的時間。

通用語言、方法、規劃和調試是在驗證環境的不同階段實現塊到 SoC 重用的先決條件。

有了正確的基礎設施,團隊就可以專注于構建與模塊接口的測試套件。

測試套件

對針對塊級的測試套件采用錯誤的方法,使得在 SoC 級別重用塊級驗證環境和測試變得困難。

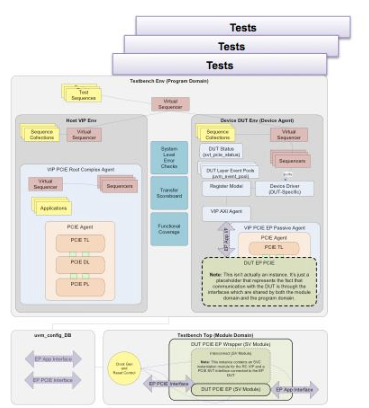

圖 2 顯示了如何配置測試套件以支持在塊級別驗證 PCI Express IP,這也適合在 SoC 級別重用。

圖 2:PCI Express 設計的測試套件

測試套件設計為模塊化。圖 2 右上角的模塊顯示了如何將 PCI Express 端點 RTL、AXI 接口和相關驅動程序封裝到一個環境中。關系圖的左上角顯示了封裝在另一個環境中的根復雜 VIP。將整體環境與“底層”隔離開來是實現塊級和 SoC 級驗證之間平穩過渡的關鍵。

在實現測試套件時,目標應該是避免進行會阻礙重用的更改;以避免多次“觸摸”測試。即使是相對較小的任務,如更改屬性的分層路徑,如果必須更改數百甚至數千個測試,也會產生大量工作。

為了最大程度地減少更改,驗證團隊在規劃和編寫測試時應考慮塊級別和 SoC 級別之間可能更改的內容,并確保測試不引用內部環境。最好的方法是創建“配置感知”的測試,即測試應該了解整體環境和配置。測試應傳遞配置的名稱,并讓驅動程序決定如何應用信息。

驗證團隊必須將所有這些原則付諸實踐,以便實現從塊到 SoC 級別的重用。弄錯它們會產生額外的工作,以便將IP測試套件過渡到芯片級別。

新思科技VC驗證IP

Synopsys 在構建其下一代驗證 IP 解決方案時廣泛使用 SystemVerilog,以支持易用性和重用性。例如,Synopsys 為符合 UVM(通用驗證方法)的測試套件提供 SystemVerilog 源代碼,這可以節省大量開發時間并減少對內部專業知識的需求。內置功能使工程師能夠在整個驗證范圍內應用一致的方法,以便在模塊和 SoC 級別進行高效驗證。

Synopsys 驗證 IP 和測試套件解決方案支持從架構分析到模塊驗證、互連設計、SoC 集成,最后到仿真中的軟硬件協同驗證的整個驗證過程。廣泛的 Synopsys 驗證 IP 產品組合包括驗證復雜 SoC 設計所需的最新協議、接口和存儲器。Synopsys VIP 部署在數千個項目中,支持 AMBA、PCI Express、USB、MIPI、DDR、LPDDR、HDMI、以太網、SATA/SAS、光纖通道、OCP 等。

總結

驗證 IP 已成為驗證流程的關鍵部分,支持廣泛的任務,例如性能分析、IP 模塊、互連和 SoC 的 RTL 驗證,以及以具有仿真功能的事務處理器的形式實現全芯片驗證,包括硬件-軟件協同驗證。

驗證環境中的 IP 到 SoC 級重用可以提高整個驗證過程的工作效率。這種方法要求驗證團隊使用相同的語言、方法和驗證 IP 開發可重用的塊測試環境,所有這些都必須專門構建以支持重用,并具有一致應用的指南。

審核編輯:郭婷

-

soc

+關注

關注

38文章

4161瀏覽量

218167 -

IP

+關注

關注

5文章

1701瀏覽量

149504 -

仿真

+關注

關注

50文章

4070瀏覽量

133552

發布評論請先 登錄

相關推薦

[啟芯公開課] SystemVerilog for Verification

混合信號SoC助力模擬IP發展

基于C的測試和驗證套件集成到常規UVM測試平臺的方法

基于C的測試和驗證套件集成到常規UVM測試平臺的方法

SOC測試訪問機制

CoreSight SoC-400綜合套件解決方案

MIPI聲線測試套件

SystemVerilog測試套件加速IP到SoC的重用

SystemVerilog測試套件加速IP到SoC的重用

評論