隨著半導體行業向更小的工藝節點發展,靜態功耗已成為主要的設計限制。這需要開發各種電源管理技術。例如,設計人員可能會創建多個電壓域,或使用隔離單元將關斷電源域與上電域隔離開來。他們可能會應用電平轉換器在信號從一個域傳播到另一個域時向上或向下縮放信號電壓,或者使用保留單元在關斷前更快地將寄存器返回到其狀態。與用于指定設計功能意圖的硬件描述語言 (HDL) 一樣,實現這些技術需要一種通用語言來指定設計的電源意圖:統一電源格式 (UPF)。

考慮到當今SoC的應用非常復雜且通常具有特定性,設計和實現所需功能以及時序和功耗要求的努力是巨大的。但僅僅實現這些目標是不夠的。最終用戶對在最短的時間內獲得最新功能的永不滿足的渴望給IP開發團隊帶來了壓力。為了滿足上市時間目標,芯片設計公司通常采用并行開發方法,其中不同的團隊編寫寄存器傳輸級別 (RTL)、Synopsys 設計約束 (SDC) 文件、UPF 文件等。

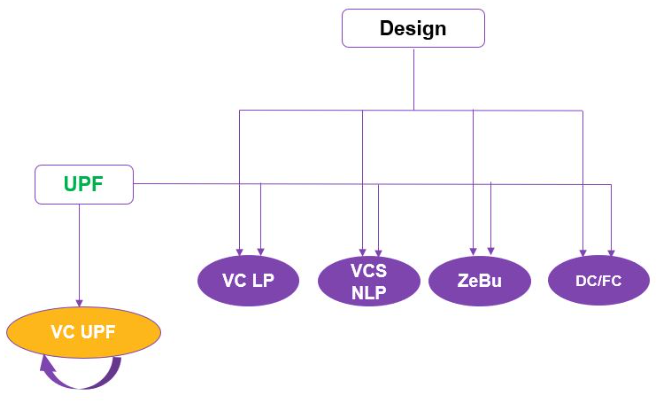

盡管設計和UPF的開發齊頭并進,但它們的時間表可能會有所不同,這可能會導致一些挑戰。在這篇博文中,我將解釋如何使用 Synopsys VC LP? 獨立于設計的 UPF Checker (VC UPF) 克服這些挑戰。請繼續閱讀,了解 VC UPF 如何讓您在 RTL 準備就緒之前清理 UPF 文件中與設計無關的問題。

優化您的 SoC 電源設計

在設計 SoC 時,UPF 的第一個版本甚至在 RTL 最終確定之前就已經準備就緒。除非設計準備就緒,否則無法驗證UPF的準確性和完整性。因此,通常有一個窗口,編寫UPF的工程師只是在等待RTL第一次切割的關閉。一旦設計準備就緒,工程師就會運行一個靜態檢查工具來驗證UPF與設計的關系,這時他或她意識到UPF中存在一些基本問題,即使不閱讀設計,這些問題也可能被捕獲。不幸的是,在這個過程中已經浪費了一些時間。UPF 修復和檢查的多次迭代會導致較長的周轉時間!

這就是VC UPF來拯救的地方。

顧名思義,VC UPF 使電源意圖所有者能夠在 RTL 準備就緒之前清理 UPF 文件中與設計無關的問題。該解決方案包括:

UPF 語法和語義檢查

基于UPF供應分析的檢查

PST 一致性檢查

UPF 網絡相關一致性檢查

基于允許/不允許的命令和選項的方法特定檢查

讓我們看幾個例子來了解這如何提供幫助。

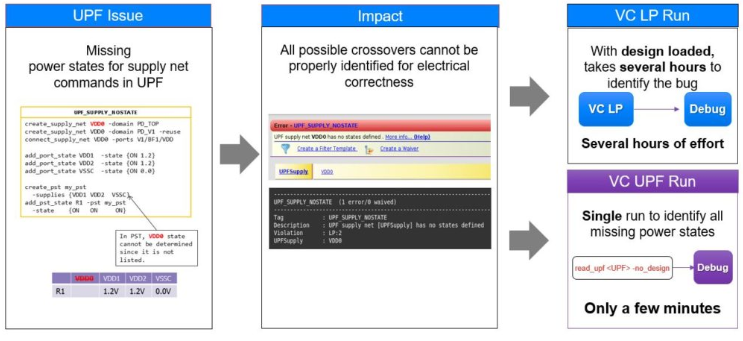

考慮UPF供電網絡未定義任何電源狀態的情況。只有在閱讀設計、加載 UPF 并完成 UPF 檢查后,用戶才會意識到,由于缺少狀態,有些交叉無法進行分析。使用 VC UPF,此信息將在幾分鐘內提供。

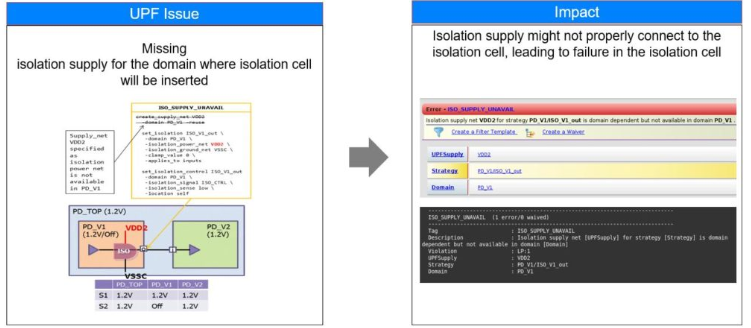

在另一種情況下,隔離策略的隔離電源網絡可能在所需域中不可用。

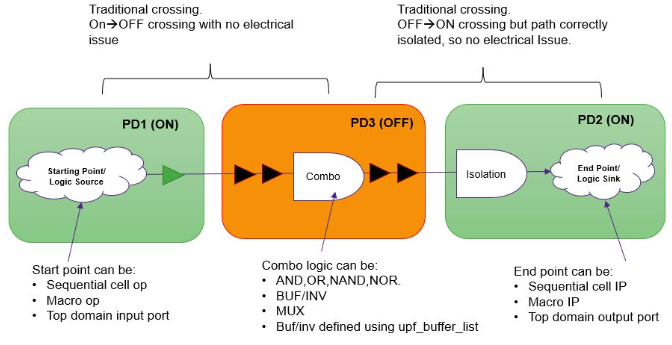

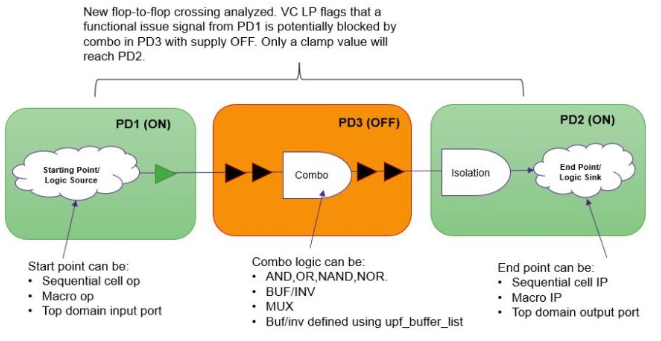

這是另一個例子。考慮從 PD3 到 PD2 的路徑。沒有電氣問題,因為OFF-》ON交叉路口由隔離單元正確保護。因此,傳統的電氣檢查不會標記任何違規行為。但在同樣的情況下,存在一個功能問題,即來自 PD1 的信號被 PD3 中的組合阻擋,該組合已關閉電源。

VC LP 中的新高級檢查正確標記了問題,并提醒設計人員,盡管路徑已正確隔離,但來自 PD1 的信號被 OFF 域中的組合阻止,只有箝位值才能達到 PD2。

根據違規情況,設計人員應驗證路徑是否旨在在指示的電源狀態期間攜帶功能信息。如果它在給定電源狀態下不起作用,則無需進一步操作。另一方面,如果路徑正常工作,則需要打開指示的緩沖器/逆變器/組合,并且需要修復與組合的電源連接。通過仿真識別這些問題非常耗時,但借助 VC LP,您現在可以在設計周期的早期發現這些問題,并節省仿真時間。

雖然VC UPF的主要動機是早期清理UPF,但它也可用于SoC的UPF管理。 復雜的SoC具有來自不同供應商/組的IP塊的UPF文件,這通常會導致UPF修改延遲以及計劃和重新驗證延遲。為了避免這種情況,CAD 團隊可能會強制執行一些引導軟件規則,以符合 IP 供應商的 UPF 可交付成果,以實現平穩的 SoC 集成。VC UPF 可以幫助使用 disallow_* 命令或 allow_* 命令執行此類指南軟件 UPF 構造檢查。

同樣,在 SoC 集成期間,您可能不希望從頂部覆蓋特定的 IP 級 UPF TCL 變量。帶有設計檢查工具的標準UPF永遠不會認識到這是一個問題。但是使用 VC UPF,您可以指定此類受保護變量的列表,并快速找出其中是否有任何變量已被頂級 UPF 覆蓋。還可以驗證 IP 的 UPF 版本與 SoC UPF 的兼容性。根據有關允許和不允許哪些 UPF 版本組合的用戶指南,VC UPF 可以執行 IP 與 SoC 一致性檢查。請注意,否則,VC LP 與 UPF 版本無關,并且“upf_version”沒有后果。

經過生產驗證的功耗感知靜態檢查簽核

Synopsys VC LP 解決方案為 UPF 提供準確且經過生產驗證的支持,與其他用于靜態低功耗檢查和調試的工具緊密集成:

Synopsys Verdi? 自動化調試系統提供事實上的行業標準工作流程、界面和調試功能。

Synopsys IC 編譯器? II 布局布線解決方案使用 VC LP 工具在設計周期的早期識別 UPF 和相關違規行為。IC 編譯器 II 命令可用于修復發現的沖突。

Synopsys VC 正式?的下一代形式驗證解決方案提供功耗感知連接檢查。

總結

不言而喻,設計滿足所需功能、時序和功耗要求的低功耗 SoC 需要付出很多努力。這項事業也面臨著嚴格的上市時間壓力。通常,芯片設計公司選擇并行開發方法,其中不同的團隊編寫 RTL、設計約束文件、UPF 文件等。但是,雖然設計和UPF的開發可能齊頭并進,但它們的時間表可能會有所不同。

VC LP 解決方案使電源意圖所有者能夠在 RTL 準備就緒之前清理 UPF 文件中與設計無關的問題。該解決方案還可用于 SoC 的 UPF 管理,因為復雜的 SoC 通常具有來自不同供應商的 IP 的 UPF 文件,這可能會導致 UPF 修改延遲以及計劃和重新驗證延遲。由于能夠盡早清理UPF,工程師可以在低功耗SoC設計周期中節省時間和精力。

審核編輯:郭婷

-

數據包

+關注

關注

0文章

260瀏覽量

24385 -

MIPI

+關注

關注

11文章

310瀏覽量

48613 -

DSI

+關注

關注

0文章

51瀏覽量

42349

發布評論請先 登錄

相關推薦

RTOS低功耗設計原理及實現_TicklessMode(FreeRTOS的實現)

低功耗藍牙怎么低功耗?如何界定

低功耗ADC的低功耗參考和雙極電壓調節電路精密驗證設計

【NUCLEO-L552ZE-Q開發板試用連載】低功耗智能電表驗證

如何在汽車設計中降低功耗

如何在低功耗Bluetooth? PEPS系統中添加CAN節點

如何在低功耗模式下使用SPC560bxx中的RTC呢?

如何在DDR中完成imx8m低功耗管理?

藍牙低功耗OTA測試系統的無線性能驗證問題解決方案

CPF低功耗解決方案在在低功耗驗證過程中應用分析

如何在RTOS中處理微控制器的低功耗特性

X態傳播在低功耗驗證中的作用

如何在低功耗設計驗證中盡早快速左移

如何在低功耗設計驗證中盡早快速左移

評論