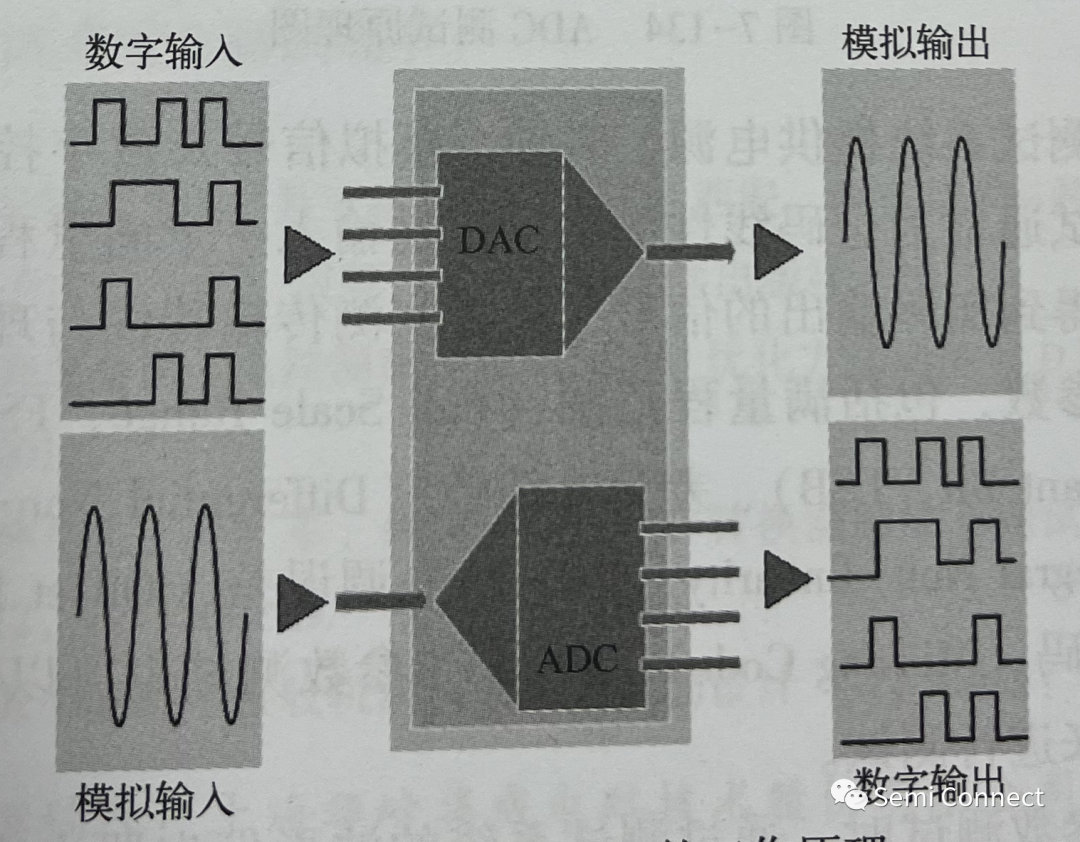

混合信號集成電路是指包括數(shù)宇模塊和模擬模塊的集成電路。將數(shù)字信號轉(zhuǎn)換為模擬信號的電路稱為數(shù)模轉(zhuǎn)換器(D/A 或 DAC),將模擬信號轉(zhuǎn)換為數(shù)字信號的電路稱為模數(shù)轉(zhuǎn)換器(A/D或 ADC)"。圖所示的是 ADC/DAC 的工作原理。目前,已經(jīng)商用化的 ADC/DAC 速率達到數(shù)十 Cbit/ s,位數(shù)達到 32bit。

模數(shù)較換的作用是將時問連續(xù)、幅值也連續(xù)的模擬量錢換為時間離散、幅值也高散的數(shù)字信號,數(shù)模轉(zhuǎn)換的作用則剛好相反。采樣是將連線(即模擬)信號轉(zhuǎn)變?yōu)殡x散(即數(shù)宇)信號的處理過程;反之,重構(gòu)是將離散信號轉(zhuǎn)變?yōu)檫B續(xù)信號的處理過程。采樣和重構(gòu)在混合信號集成電路測試中均得到了廣泛的應(yīng)用。理論上,必須按照采樣定理進行采樣,即采樣頻率應(yīng)大于2倍的信號頻率;但在實際測試中,有時也會用到過采樣(Over Sampling)和欠采樣(Under Sampling)。基于 DSP 的測試涉及兩種采樣類型,即相干采樣和非相干釆樣。相干采樣要求滿足F3/Ft=N/M,其中F3.為采樣頻率,F(xiàn)1為信號頻率,N為采樣點數(shù),M 為采樣周期數(shù),且M 與N互為素數(shù),這樣可避免重復(fù)采樣,提高效率。針對周期信號的不相千采樣容易引起頻譜泄露。

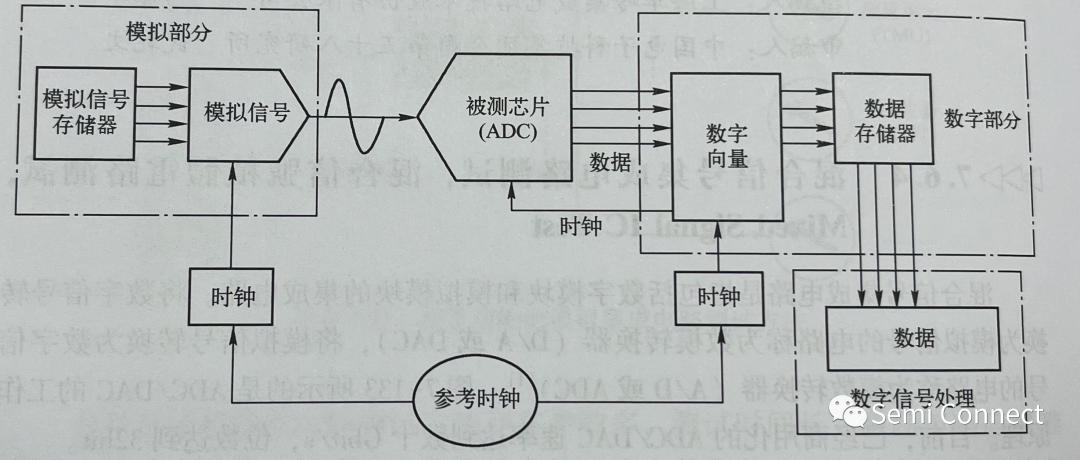

混合信號集成電路的測試包括直流參數(shù)測試和交流參數(shù)測試,如功耗、漏電、電源抑制比、建立時間等;而針對其傳輸特性,則主要測試靜態(tài)參數(shù)與動態(tài)參數(shù)。圖所示為 ADC 測試原理圖。

測試時,由測試系統(tǒng)提供電源、時鐘、模擬信號及數(shù)宇控制信號給被測電路。靜態(tài)參數(shù)測試通常為全碼線性測試,通過輸人一個滿量程的信號頻率較低的三角波,采樣得到實際輸出的信號,通過實測傳輸特性與理想傳輸特性的比較來確定其靜態(tài)參數(shù),包括滿量程范圍 (Full Scale Range, FSR)、最低有效量值 (Least Significant Bit, LSB)、差分非線性 ( Diferential Non-linearity, DNL)、積分非線性 (Integral Non-lineariy, INL)、失調(diào)誤差 (Otfset Error)、增益誤差(Gain Brror)、失碼( Missing Code) 等。靜態(tài)參數(shù)測試也可以通過輸人正弦波采用直方圖方法來進行測試。

在進行動態(tài)參數(shù)測試時,通過測試系統(tǒng)的波形發(fā)生器生成一定頻率的測試波形(通常為正弦波),該測試波形的準(zhǔn)確度必須遠高于被測電路的準(zhǔn)確度;將測試波形輸人被測電路后,采樣得到輸出的時域信號;通過快速傅里葉變換(Fast Fourier Transform, FFT) 將采樣的時域信號變換為頻域信號進行處理,?析得到混合信號集成電路的動態(tài)參數(shù)。動態(tài)參數(shù)包括信噪比 ( Signal Noise Ratio,SNR)、總諧波失真 (Total Harmonie Distorion, THD)、有效位數(shù)(EffeetNumber of Bits, ENOB)、無雜散動態(tài)范圍 ( Spurious Free Dynamic Range,SFDR)、噪聲與諧波總失真 (Signal to Noise and Distortion. SINAD)、互調(diào)失真(Intermodulation Distortion, IMD)等。在理想的轉(zhuǎn)換器中,SINAD 和 SNR 是相同的。如果 SNR 是轉(zhuǎn)換器所能達到的理想狀態(tài),SINAD 是反映轉(zhuǎn)換器實際性能參數(shù)的指標(biāo),則 SINAD 越接近 SNR,表示其性能越好。ENOB 可以在信噪比基礎(chǔ)上計算得出,即

ENOB= ( SINAD-1.76)/6.02

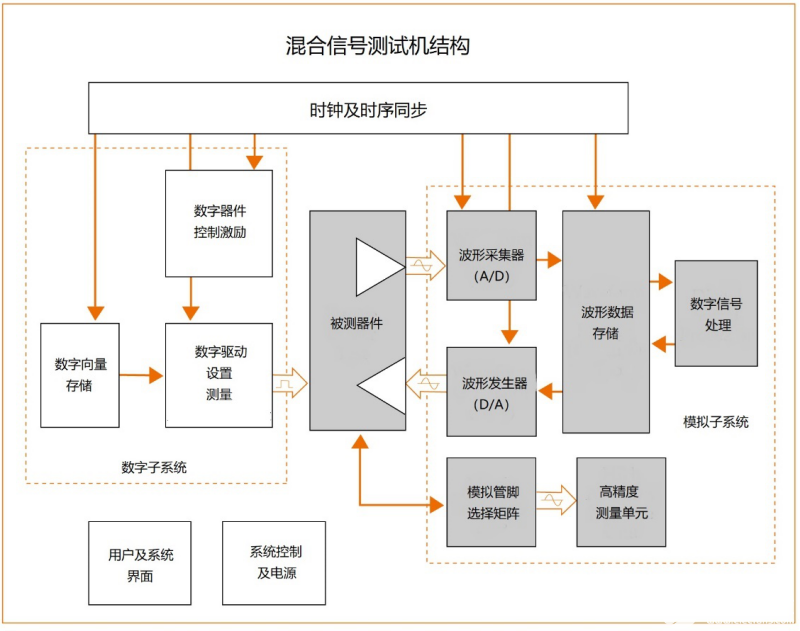

測試混合信號集成電路時,同樣需要考慮可測性設(shè)計,以及設(shè)計與測試的鏈按,提供其測試所需的軟硬件環(huán)境。混合信號集成電路測試系統(tǒng)除了具備數(shù)字集成電路測試系統(tǒng)的能力,還應(yīng)具備產(chǎn)生高準(zhǔn)確度任意波形的能力,捕捉和處理數(shù)字信號及模擬信號的能力,以及數(shù)宇模塊與模擬模塊同步的能力。

針對現(xiàn)階段不斷涌現(xiàn)出的高速、高精度 ADC/DAC,如果測試用的自動測試系統(tǒng)無法提供滿足其要求的高精度時鐘、信號源等,可采用高質(zhì)量的分立儀器,或者進行回環(huán)(Loopback)測試;針對測試負(fù)載板(Load Board),不僅要在設(shè)計上保證電源、地的干凈,還要格外注意時鐘及高速/高精度信號等關(guān)鍵信號的布線問題,并對信號進行充分的濾波處理。目前,新的標(biāo)準(zhǔn) IEEE 邊界掃描方法己經(jīng)完全適用于混合信號測試,如果將來能實現(xiàn)混合信號集成電路的結(jié)構(gòu)測試,將大大降低其測試難度 與測試成本。

審核編輯:湯梓紅

-

集成電路

+關(guān)注

關(guān)注

5387文章

11530瀏覽量

361630 -

混合信號

+關(guān)注

關(guān)注

0文章

472瀏覽量

64949 -

adc

+關(guān)注

關(guān)注

98文章

6495瀏覽量

544461 -

dac

+關(guān)注

關(guān)注

43文章

2291瀏覽量

190974 -

數(shù)模轉(zhuǎn)換器

+關(guān)注

關(guān)注

14文章

1011瀏覽量

83166

原文標(biāo)題:混合信號集成電路測試,混合信號積體電路測試,Mixed Signal IC Test

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

混合集成電路的EMC設(shè)計

集成電路測試儀有什么類別?

集成電路可測性設(shè)計方法

集成電路電磁騷擾測試方法

VXI數(shù)模混合集成電路測試系統(tǒng)

基于虛擬儀器技術(shù)的混合集成電路測試系統(tǒng)的設(shè)計與實現(xiàn)

利用ADMS平臺加速混合信號集成電路設(shè)計

混合集成電路,混合集成電路是什么意思

混合集成電路,什么是混合集成電路

集成電路測試技術(shù)與應(yīng)用

混合信號集成電路分析與設(shè)計

高速信號集成電路測試方法

混合信號集成電路測試方法

混合信號集成電路測試方法

評論