您可以在手持設備的空間中裝入多少個晶體管?這個數字每過十年就會增加幾個數量級。便攜式音樂播放器說明了這一點。1979年,晶體管收音機需要大約200個晶體管。1984年,CD播放器需要大約1,500個晶體管。1990年,MP3播放器需要大約10,000個晶體管。對于2015年的數字音頻播放器,大約有1,000,000個晶體管。工藝技術的進步使這些增長成為可能,如今,主要由先進的AI和5G應用驅動的多芯片系統正在幫助實現另一個巨大的飛躍。事實上,在 2023 年,一部典型的智能手機擁有超過 10 億個晶體管!用戶優勢顯而易見。就音樂而言,這意味著更好的保真度,更多的空間來播放,存儲和流式傳輸您喜歡的音樂,共享,播放,與其他設備的互操作性等方面的更多功能等等。但復雜性并非沒有設計挑戰。

對計算資源的增加需求實際上與本地服務器的資本支出或安裝它們所需的時間不一致。面對成本壓力、不斷縮小的市場窗口和市場需求(更好的性能和更多的功能),本地存儲是許多企業無法再承受的負擔。在云中對IC設計的計算資源進行彈性擴展的需求已經到來。

第一個使您能夠利用云進行 IC 設計的大規模 SaaS 解決方案是 Synopsys Cloud。Synopsys 云將高級計算和存儲基礎架構的可用性與按需無限制地訪問 EDA 軟件許可證相結合。作為臺積電開放創新平臺?(OIP)生態系統的一部分,新思科技最近與臺積電和微軟合作,使用Synopsys IC驗證器?物理驗證(Synopsys Cloud產品)在臺積電N3E流程的Microsoft Azure云中執行設計規則檢查(DRC)的測試用例。

結果呢?云中的 DRC 可以幫助您更快地完成下一個大型復雜 IC 設計 - 方法如下。

顯著縮短設計規則檢查的運行時間

那么,為什么我們選擇DRC作為我們的測試用例呢?DRC 確保設計正常運行,并且可以在鑄造廠制造。使用傳統的本地計算資源執行它們可能需要寶貴的時間,尤其是在設計變得更大、越來越復雜的情況下。

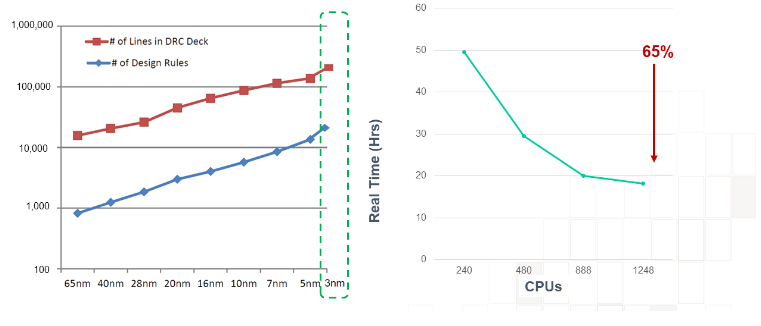

由于當今的設計尺寸更大,因此流程規則的數量也有所增加。事實上,當今許多設計中的流程規則可能達到數千條,而增加的設計復雜性可能導致數百個步驟。對于擁有數十億個晶體管的多芯片系統,DRC 或布局與原理圖 (LVS) 作業可以運行數天并利用數百個 CPU 內核。

在較短的上市時間 (TTM) 窗口中需要增強的計算能力會導致物理驗證挑戰。當工藝節點從 7nm 推進到 5nm 再到 3nm 甚至更高時,尤其如此。例如,在 3nm 時,一個運行集可以包含超過 15,000 個復雜規則,并且需要 10 倍的 DRC 計算操作來執行規則。因此,僅一次迭代,全芯片 DRC 簽核就可能消耗數萬個 CPU 小時。雖然物理驗證一直是計算密集型的,但當今設計的尺寸和復雜性將這一挑戰提升到了一個全新的水平。

運行 DRC 和 LVS 作業的串行依賴關系意味著購買更多計算能力并不一定等同于更快的運行時間。需要計算規模的IC驗證意味著在串行操作期間,部分計算能力有時會處于空閑狀態。如果您沒有找到針對此類場景優化計算資源的方法,這將影響您的底線 - 您將為那些未使用的資源付費。

使用云計算進行 IC 驗證可以幫助您消除這種情況。通過云驗證,您可以從數百個本地 CPU 內核擴展到云中的數千個 CPU 內核。這種彈性為您提供了靈活性、敏捷性和可擴展性,可在需要時僅使用所需的計算資源。運行集中的 DRC 可以分布在多個內核中并行運行,從而優化計算資源,從而節省時間和金錢。

云中的 IC 設計如何將驗證時間縮短 65%

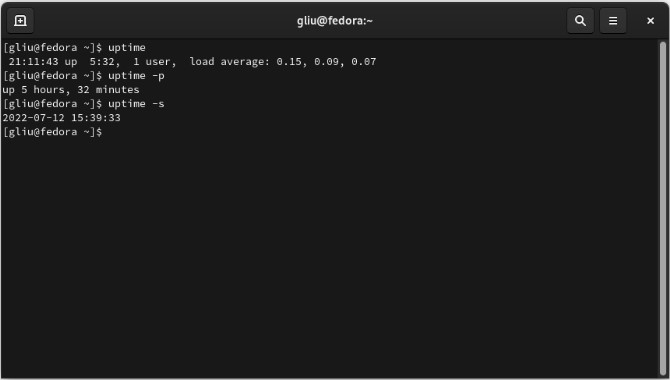

在 Synopsys、臺積電和微軟的合作中,我們根據內部部署驗證評估了云驗證。為了啟動測試,臺積電的工藝設計套件 (PDK) 和 DRC 被上傳到 Synopsys 云環境。我們根據 Synopsys IC 驗證器中的設計類型選擇了不同的資源,這是 Synopsys Cloud 環境中用于物理驗證的單獨應用程序,并且為資源預先選擇了計算選項。在我們上傳運行測試用例所需的腳本并選擇 Microsoft Azure 實例(FX 和 Mdsv2 計算以及用于共享存儲的 Azure Netapp Files (ANF))之后,我們只需單擊一下即可創建虛擬機 (VM) 群集,其中包括數百個 CPU 內核。

我們的實驗流程在幾個小時內就可以執行了,我們快速執行了一個大型測試用例,以比較使用臺積電 N3E 流程在云中運行的作業和臺積電本地運行的作業的結果。所有結果(云和本地)都使用XOR操作保存在GDSII文件中,并且兩次運行中的任何錯誤都必須完全匹配才能獲得干凈的結果。

云作業的實時運行小時數從大約 50 小時減少到 20 小時以下,與本地作業相比,云中的運行小時數提高了 65%。此外,與本地相比,在云中的測試運行中,CPU 小時數和成本降低了 25%。

云端IC設計 臺積電N65E工藝運行時間縮短3%

圖片來源:臺積電

新思科技 IC 驗證器是現代設計的物理驗證工具

Synopsys IC 驗證器是一種物理驗證工具,可以在數千個 CPU 內核之間分配作業。這項技術成功的核心是調度程序,它為每個內核的命令排隊,以使用 DRC 序列優化文件位置。它還估計和平衡內核之間的內存需求,并最大限度地減少峰值磁盤使用,動態監控每個內核上的負載并調整系統以提高內核和內存利用率。由于它在異構配置中工作,通過容錯功能具有實際延遲,因此它可以檢測主機重新啟動、網絡和套接字故障、計算機崩潰和磁盤空間限制并從中恢復。

IC 驗證器動態彈性 CPU 管理可與流行的作業隊列系統(如負載共享設施 (LSF) 和太陽網格引擎 (SGE) )無縫協作。它可以用于不同類型的計算網絡,例如本地和云。其資源和成本優化的同時,它加速了時序收斂以滿足流片計劃,使用高達 40% 的計算資源,同時保持與傳統 DRC 和 LVS 作業相似的性能。這意味著在云中節省了成本,其中資源和存儲按時計費。

除了這些好處之外,IC 驗證器不需要等到所有資源都可用才能開始工作。它可以以最少的資源立即啟動,并在可用時使用更多的資源。Microsoft Azure CycleCloud 和加速網絡(單根 I/O 虛擬化,SR-IOV,可以將 Azure 的大部分軟件定義網絡堆棧從 CPU 卸載到 FPGA 智能網絡接口卡或 NIC),以幫助確保分別針對虛擬機優化的擴展和增加的數據吞吐量。

確保云中的 EDA 安全無虞

除了所有時間和成本優勢之外,您還可以通過采取措施確保您的系統得到適當保護,從而確保云部署中的 EDA 安全。與最新標準保持同步,并確保您的網絡安全系統是最新的。擁有管理良好且隔離的虛擬網絡 (VNET) 是關鍵。

審核編輯:郭婷

-

IC設計

+關注

關注

38文章

1297瀏覽量

104038 -

服務器

+關注

關注

12文章

9206瀏覽量

85564 -

DRC

+關注

關注

2文章

149瀏覽量

36204

發布評論請先 登錄

相關推薦

如何檢查Linux服務器的運行時間

基于本地任務與遠程任務運行時間的CPS和PAA的概念

電機運行時間進行排列 是分為兩個部分來完成這個程序的設計的

MOSIS在領先的FinFET工藝設計中為DRC和LVS signoff部署IC Validator

如何高效測量ECU的運行時間

淺析STM32代碼運行時間的技巧

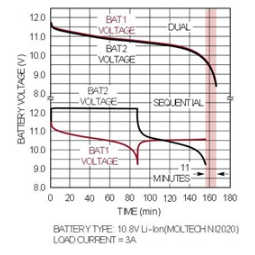

雙電池電源管理器將運行時間延長12%,充電時間縮短一半

單片雙電池電源管理器可延長運行時間并縮短充電時間

ch32v307記錄程序運行時間

西門子SCL編程50臺電機運行時間累計方法

云IC驗證如何將DRC運行時間縮短65%

云IC驗證如何將DRC運行時間縮短65%

評論