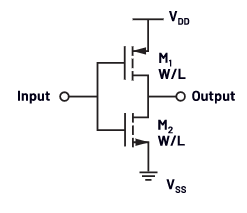

我們將簡單的CMOS反相器邏輯門用作一對開關(guān)。 ADALM2000 的標準CMOS分壓器(推挽模式)。采用最簡單的形式,CMOS輸出可以由一個PMOS器件M1和一個NMOS器件M2組成。通常,CMOS制造工藝經(jīng)過特別設(shè)計,使得NMOS和PMOS器件的閾值電壓VTH大致相等——即互補。然后,反相器的設(shè)計人員調(diào)整NMOS和PMOS器件的寬長比W/L,使其各自的跨導和RON也相等。兩個晶體管中,只有一個處于導通狀態(tài),同時將輸出端連接到VDD或VSS。我們可以考慮將這兩個電壓用作DAC的基準電壓源。

圖1.CMOS輸出驅(qū)動器。

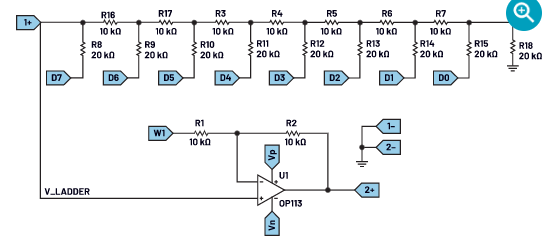

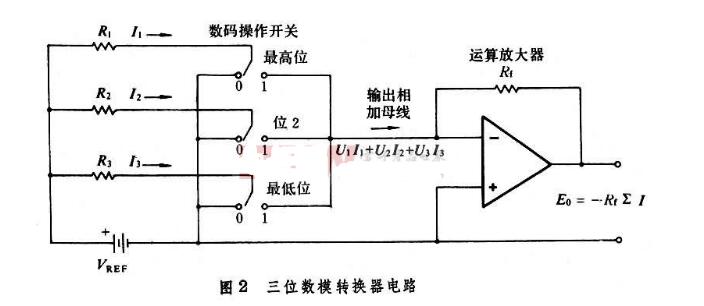

在 “電壓模式”中使用R-2R梯形電阻(如圖2所示),根據(jù)數(shù)字碼交替驅(qū)動到兩個基準電壓電平中的任一個(D0-7)。數(shù)字0表示VREF–,數(shù)字1表示VREF+。根據(jù)數(shù)字輸入碼,VLADDER(圖2)將在兩個基準電平之間變化。兩個基準電壓的負基準電壓(VREF–)通常為地電壓(VSS)。在本例中,我們將正基準電壓(VREF+)設(shè)置為CMOS驅(qū)動器的正電源電壓(VDD)。

材料

ADALM2000主動學習模塊

無焊面包板

跳線

9個20 kΩ電阻

9個10 kΩ電阻

一個 OP27 放大器

說明

最好在無焊試驗板上構(gòu)建圖2所示的8位梯形電阻電路。模擬部件套件(ADALP2000)中提供的電阻數(shù)量通常不足以構(gòu)建完整的8位梯形電阻。如果可以獲得這些電阻,此項目最好使用1%的電阻。

將用藍色框表示的8個數(shù)字輸出、示波器通道和用綠色框表示的AWG輸出連接到梯形電阻電路中,如圖所示。注意將電源連接到運算放大器電源引腳。

圖2.R-2R梯形電阻網(wǎng)絡(luò)電路

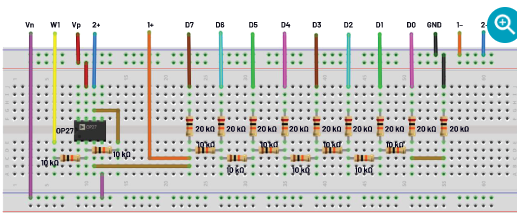

硬件設(shè)置

圖3.R-2R梯形電阻網(wǎng)絡(luò)電路試驗板連接

程序步驟

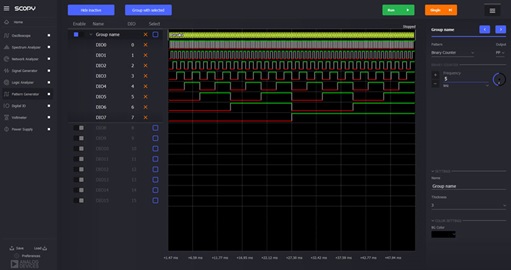

當安裝R1和R2時,設(shè)置AWG1的直流電壓與DAC的VREF+相等,即等于CMOS數(shù)字輸出的3.3 V電源電壓。此時輸出電壓為雙極性,其擺幅為-3.3 V至+3.3 V。斷開AWG1并移除電阻R1,輸出電壓為單極性,擺幅為0 V至+3.3 V。啟動Scopy軟件。打開模式發(fā)生器界面。選擇DIO0至DIO7,并組成一個分組。設(shè)置參數(shù),將模式設(shè)置為二進制計數(shù)器。輸出設(shè)置為推挽輸出(PP),頻率設(shè)置為256 kHz。此時能看到類似圖4所示的內(nèi)容。最后,點擊運行按鈕。

圖4.模式發(fā)生器界面。

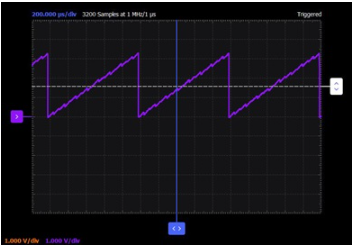

打開示波器界面,開啟通道2,并將時基設(shè)置為200μs/div,點擊綠色運行按鈕開始運行。有時可能還需要調(diào)整通道的垂直范圍(初始條件下,1 V/div比較合適)。通過示波器界面能看到(如圖4所示)電壓從0 V上升到3.3 V,斜坡信號的周期應(yīng)為1 ms。

圖5.示波器界面。

改變數(shù)字模式。嘗試隨機模式,并打開示波器上的FFT窗口。您還可以通過生成具有一列0到255(對于8位寬總線)數(shù)字的純文本.csv文件,來加載自定義模式。加載自定義模式,看看會出現(xiàn)什么情況。

您可以嘗試加載以下這些預(yù)制波形文件:正弦、三角、高斯脈沖等:waveforms_pg。

AD5626 12位 nanoDAC

背景信息

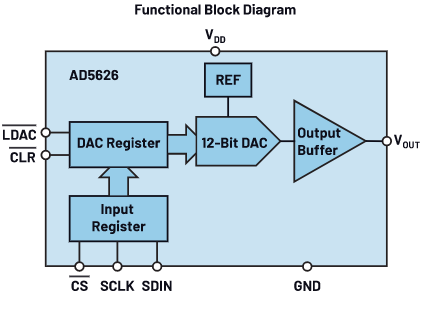

AD5626 是一款可以使用5 V單電源供電的電壓輸出DAC。它集成了DAC、輸入移位寄存器和鎖存、基準電壓源以及一個軌到軌輸出放大器。輸出放大器擺幅可達到任一供電軌,且設(shè)置范圍為0 V至4.095 V,分辨率為每位1 mV。該器件采用高速、三線式、兼容數(shù)據(jù)輸入(SDIN)的DSP、時鐘(SCLK)和負載選通(LDAC)的串線接口。它還有芯片選擇引腳,可連接多個DAC。上電時或用戶要求時,CLR輸入可將輸出設(shè)置為零電平。

圖6.AD5626的簡化功能框圖。

除1位DAC寄存器外,AD5626還有一個獨立的串行輸入寄存器,新數(shù)據(jù)值可以預(yù)載到該串行寄存器中,而不會干擾現(xiàn)有DAC輸出電壓。通過選通LDAC引腳,可以將加載值傳輸?shù)紻AC寄存器。

單極性輸出操作

這種操作模式是AD5626的基本模式。您可以根據(jù)DAC的單極性代碼表驗證AD5626的功能是否正常。

| DAC寄存器中的十六進制數(shù) | DAC寄存器中的十進制數(shù) | 模擬輸出電壓(V) |

| FFF | 4095 | 4.095 |

| 801 | 2049 | 2.049 |

| 800 | 2048 | 2.048 |

| 7FF | 2047 | 2.047 |

| 000 | 0 | 0 |

材料

ADALM2000主動學習模塊

無焊面包板

跳線

一個AD5626 12位 nanoDAC?

一個2.2 kΩ電阻

一個0.001 μF電容

一個0.1 μF電容

一個10 μF電容

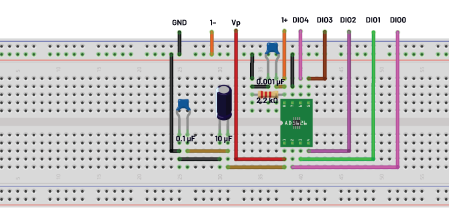

硬件設(shè)置

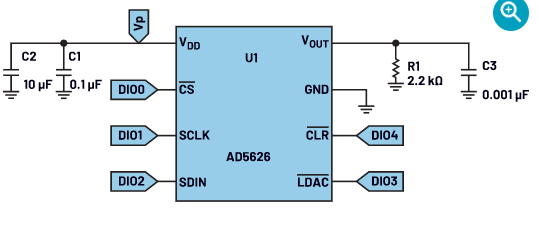

如圖7所示連接AD5626的引腳。

圖7.AD5626實現(xiàn)單極性操作的連接。

程序步驟

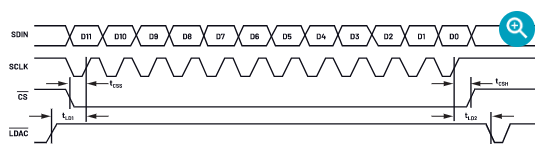

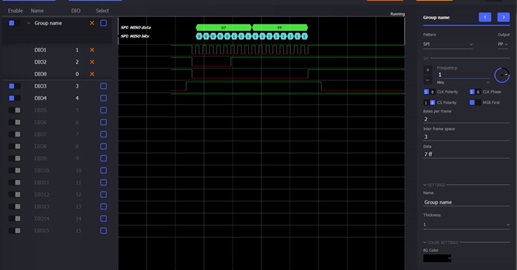

打開Scopy,使能正電源為5 V。在模式發(fā)生器中,根據(jù)數(shù)據(jù)手冊中AD5626的時序圖配置DAC輸入信號。從配置SPI信號開始。使用DIO0、DIO1和DIO2創(chuàng)建通道組。如果連接如圖7所示,則DIO1表示時鐘信號,DIO2表示數(shù)據(jù)信號,DIO0表示CS信號。在進行SPI分組時,確保數(shù)字通道的順序是正確的(參見圖10)。數(shù)據(jù)手冊中指明,高電平和低電平狀態(tài)下的時鐘寬度應(yīng)達到至少30 ns。由此可計算時鐘周期,進而計算最大頻率。將時鐘頻率設(shè)為1 MHz。將CLK極性和CLK相位設(shè)為1。

由于AD5626是12位DAC,因此通過SPI發(fā)送的數(shù)據(jù)長度應(yīng)至少為12位。將每幀的字節(jié)數(shù)設(shè)為2,在轉(zhuǎn)換開始時,它會發(fā)送16位。在數(shù)據(jù)文本框中,您可以輸入將發(fā)送至DAC的值。SPI組通道的信號應(yīng)類似于AD5626 DAC的時序圖。

圖8.AD5626試驗板連接。

圖9.AD5626 SPI時序圖。

現(xiàn)在,您應(yīng)該配置LDAC和CLR信號。從數(shù)據(jù)手冊中,我們得知在CLR處于高電平時,移位寄存器的內(nèi)容會在LDAC的上升沿更新。將DIO4 (CLR)的模式設(shè)置為“數(shù)值”,輸入數(shù)值1。只要位是串行傳輸,LDAC信號(DIO3)的CS下降沿之前應(yīng)該有一個上升沿,且應(yīng)處于高電平。為了滿足上述條件,DIO3信號可以設(shè)置為采用13 kHz頻率和160°相位。AD5626數(shù)模轉(zhuǎn)換所需的所有輸入信號如圖9所示。

圖10.模式發(fā)生器信號設(shè)置。

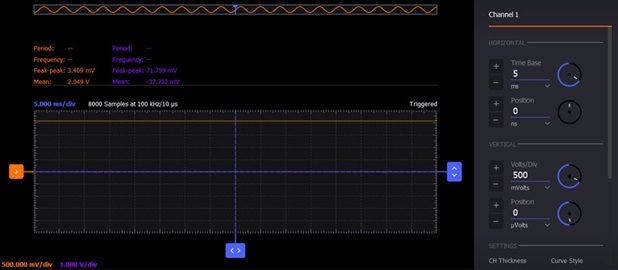

最后一步是在Scopy中打開示波器,將通道1連接到AD5626的輸出端。啟用通道1測量,并在SPI的“數(shù)據(jù)”區(qū)域輸入一個值。如果通過SPI發(fā)送的數(shù)據(jù)為7FF,在圖11中,您可以查看相應(yīng)的輸出電壓。

圖11.輸入為7FF時,AD5626的輸出電壓。

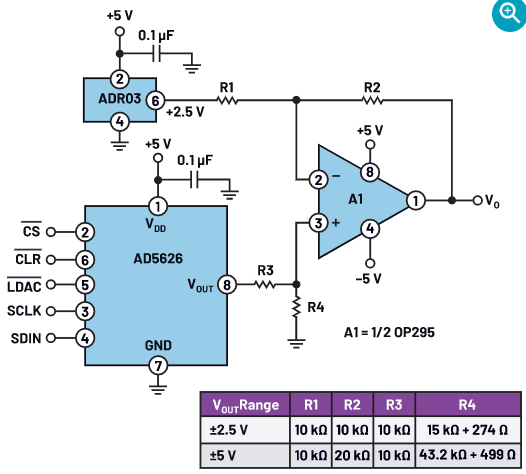

雙極性輸出操作

雖然AD5626設(shè)計用于單電源操作,但使用圖12所示的電路也可以實現(xiàn)雙極性操作。

圖12.雙極性輸出操作,未經(jīng)調(diào)節(jié)(數(shù)據(jù)手冊中建議的電路)。

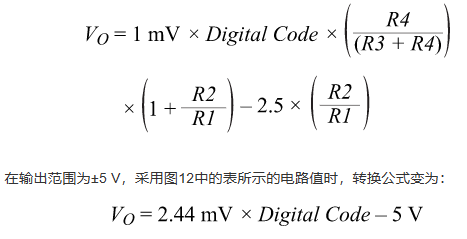

此電路可用于不需要高精度的應(yīng)用。輸出電壓以偏移二進制格式編碼,由以下公式給出:

材料

ADALM2000主動學習模塊

無焊面包板

跳線

一個AD5626 12位 nanoDAC

一個 OP484 運算放大器

一個0.1 μF電容

一個1 kΩ電阻

一個20 kΩ電阻

兩個10 kΩ電阻

一個47 kΩ電阻

一個470 kΩ電阻

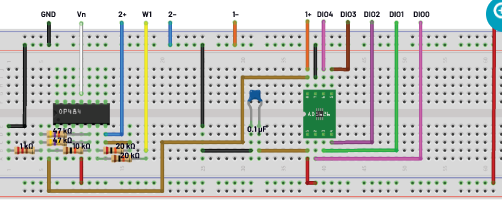

圖13.AD5626雙極性輸出操作試驗板連接

硬件設(shè)置

在無焊試驗板上構(gòu)建圖12所示的電路。

程序步驟

您可以將DAC配置為單極性輸出操作,如圖7所示。對于基準電壓,使用信號發(fā)生器的通道1,設(shè)置為恒定2.5 V。在示波器的第二個通道上,可顯示運算放大器輸出端的電壓。您可以在示波器上同時顯示單極性操作和雙極性操作的電壓。

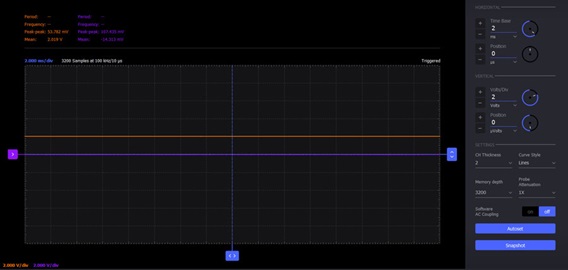

圖14.000輸入的單極性和雙極性輸出電壓。

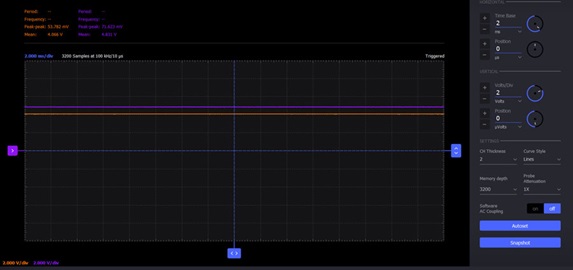

圖15.800輸入的單極性和雙極性輸出電壓。

圖16.FFF輸入的單極性和雙極性輸出電壓。

審核編輯:郭婷

-

CMOS

+關(guān)注

關(guān)注

58文章

5710瀏覽量

235418 -

分壓器

+關(guān)注

關(guān)注

0文章

191瀏覽量

18910 -

晶體管

+關(guān)注

關(guān)注

77文章

9682瀏覽量

138082

發(fā)布評論請先 登錄

相關(guān)推薦

數(shù)模轉(zhuǎn)換器的基本原理及DAC類型簡介

#硬聲創(chuàng)作季 數(shù)字設(shè)計FPGA應(yīng)用:1.數(shù)模轉(zhuǎn)換器DAC基礎(chǔ)篇

#硬聲創(chuàng)作季 01-數(shù)模轉(zhuǎn)換參數(shù)

數(shù)模轉(zhuǎn)換器是什么

數(shù)模和模數(shù)轉(zhuǎn)換器

并行數(shù)模轉(zhuǎn)換實驗

基于MELSEC iQ-R的數(shù)模轉(zhuǎn)換模塊RB的設(shè)計指南

模數(shù)轉(zhuǎn)換(A/D)與數(shù)模轉(zhuǎn)換(D/A)

數(shù)模轉(zhuǎn)換器的速度極限_數(shù)模轉(zhuǎn)換器工作原理

數(shù)字信號處理教程之模數(shù)轉(zhuǎn)換和數(shù)模轉(zhuǎn)換

DAC 數(shù)模轉(zhuǎn)換程序

探討數(shù)模轉(zhuǎn)換的概念

探討數(shù)模轉(zhuǎn)換的概念

評論