1、 概述

隨著超大規模集成電路的發展,芯片工作電壓越來越低,而工作速度越來越快,功耗越來越大。芯片內部成千上萬個晶體管組成的門電路、組合邏輯、寄存器以及其他邏輯功能電路,芯片外部電源引腳提供給內部晶體管一個公共的工供電節點,因此內部晶體管狀態的轉換會引起電源噪聲在芯片內部的傳遞,從而影響芯片的正常工作。除了對芯片本身工作狀態產生影響外,電源噪聲會影響晶振、鎖相環的抖動特性等,產生其他電磁干擾的問題。

2、 噪聲來源

第一,穩壓穩壓電源芯片本身的輸出并不是恒定的,會有一定的波紋。 這是由穩壓芯片自身決定的,一旦選好了穩壓電源芯片,對這部分噪聲我們只能接受,無法控制。穩壓電源大體分為線性電源和開關電源兩種。線性電源(LDO)通常具有很好的輸出紋波特性,電源本身輸出噪聲低,供電穩定,但是輸出功率不大,轉換效率低。開關電源(DC-DC)可以輸出很大的電流,轉換效率高,但是通常輸出紋波較大。

第二,穩壓電源無法實時響應負載對于電流需求的快速變化。 穩壓電源芯片通過感知其輸出電壓的變化,調整其輸出電流,從而把輸出電壓調整回額定輸出值。多數常用的穩壓源調整電壓的時間在毫秒到微秒量級。因此,對于負載電流變化頻率在直流到幾百KHz之間時,穩壓源可以很好的做出調整,保持輸出電壓的穩定。當負載瞬態電流變化頻率超出這一范圍時,穩壓源的電壓輸出會出現跌落,從而產生電源噪聲。現在,微處理器的內核及外設的時鐘頻率已經超過了600兆赫茲,內部晶體管電平轉換時間下降到800皮秒以下。這要求電源分配系統必須在直流到1GHz范圍內都能快速響應負載電流的變化,但現有穩壓電源芯片不可能滿足這一苛刻要求。我們只能用其他方法補償穩壓源這一不足,比如電源去耦方法。

第三,負載瞬態電流在電源路徑阻抗和地路徑阻抗上產生的壓降。 PCB板上任何電氣路徑不可避免的會存在阻抗,不論是完整的電源平面還是電源引線。對于多層板,通常提供一個完整的電源平面和地平面,穩壓電源輸出首先接入電源平面,供電電流流經電源平面,到達負載電源引腳。地路徑和電源路徑類似,只不過電流路徑變成了地平面。完整平面的阻抗很低,但確實存在。如果不使用平面而使用引線,那么路徑上的阻抗會更高。另外,引腳及焊盤本身也會有寄生電感存在,瞬態電流流經此路徑必然產生壓降,因此負載芯片電源引腳處的電壓會隨著瞬態電流的變化而波動,這就是阻抗產生的電源噪聲。在電源路徑表現為負載芯片電源引腳處的電壓軌道塌陷,在地路徑表現為負載芯片地引腳處的電位和參考地電位不同。

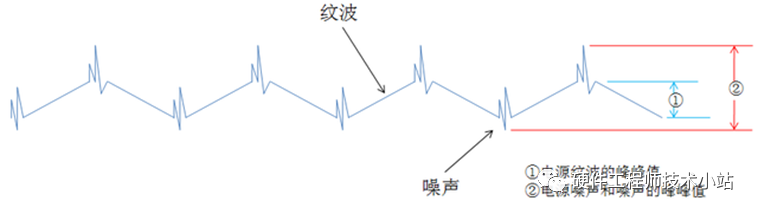

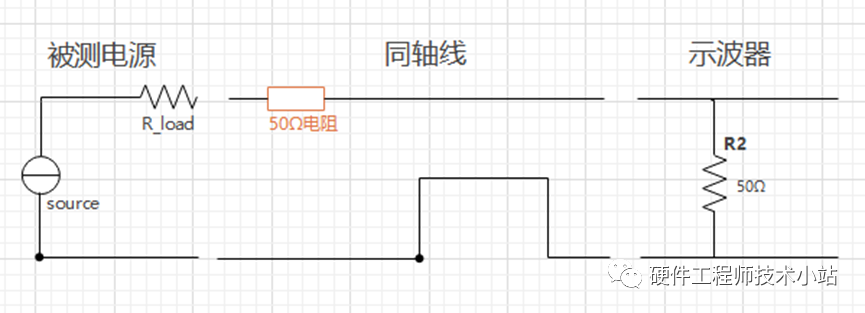

電源紋波和電源噪聲是一個比較容易混淆的概念,如下圖所示,藍色標注為

電源紋波,紅色標注為電源噪聲。電源紋波的頻率為開關頻率的基波和諧波,而

噪聲的頻率成分高于紋波,是由板上芯片高速I/O的開關切換產生的瞬態電流、

供電網絡的寄生電感、電源平面和地平面之間的電磁輻射等諸多因素產生的。因

此,在電源IC輸出側測量電源紋波,而在SINK端(耗電芯片端)測量的是電源噪聲。

圖:紋波和噪聲的區別

3、基本概念

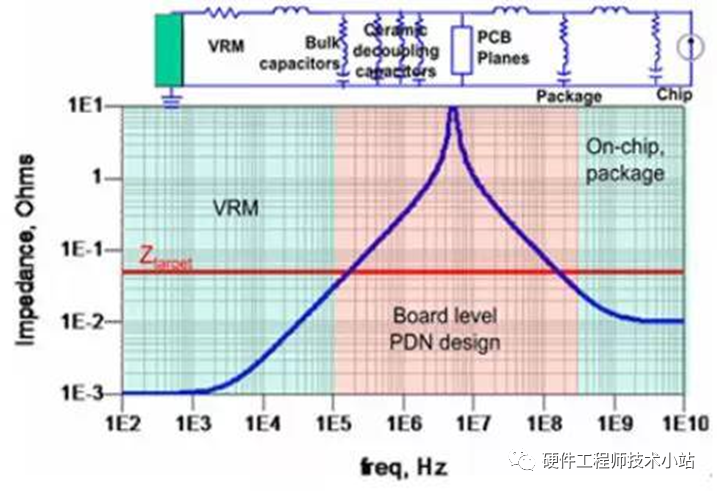

什么是PDN?

電源分配網絡又稱為電源配送網絡,包含了從穩壓電源(VRM)到芯片的焊盤,再到返回電流路徑上的所有互連。PDN系統主要有以下幾部分組成:VRM(電源芯片或電源模塊)、PCB上的電容、PCB上的電源和地平面、芯片封裝內的電容、封裝內的電源和地網絡、Die上的電容。對于PCB板級設計來說,盡管不可能得到芯片內PDN系統詳細信息,但是并不意味著它不起作用,如何將PCB和芯片內的PDN系統進行聯合設計也是難點之一。

圖:電源分配系統的構成

電源分配系統在現代電路占有越來越重要的作用,一方面,芯片的開關速度不斷提高,高頻瞬態電流的需求越來越大。另一方面,芯片的功能不斷增加,功能越來越強大,芯片的功耗也隨之增加。在高頻瞬態電流需求的情況下滿足PDN系統的噪聲要求,對設計提出了很大的挑戰,PDN系統的作用主要包含兩個方面:

1) 為負載提供干凈的供電電流。

2) 為信號提供低噪聲的參考路徑(返回路徑)

芯片最關心的是其焊盤上的電壓,假設從VRM到芯片沒有電流流動,那么在這路徑上不會有電壓降,芯片得到的電壓接近于VRM輸出電壓。如果芯片消耗的是一個恒定直流電流,那么由于PDN系統中的串聯電阻存在,該直流電流將在電源分配網絡互連上產生壓降,通常稱為 IR壓降 。當芯片上的電流發生波動,電源分配網絡上的壓降也會隨之波動,從而使芯片焊盤上的電壓也產生波動。

實際除了串聯電阻造成的電阻性阻抗,PDN互連中還包括了感性阻抗和容性阻抗,從片上焊盤看過去的電源分配網絡阻抗,通常是一個和頻率相關的阻抗,記為Z(f)

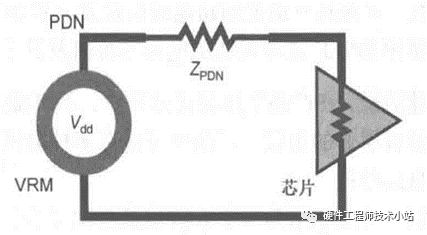

圖:從VRM到芯片,由于PDN的阻抗造成的壓降

當具有一定頻譜寬度的波動電流I(f)通過電源分配網絡的復阻抗時。電源分配網絡上將會產生電壓降:

V(f)表示電壓,是隨頻率f變化的函數,I(f)表示芯片消耗電流的頻譜,Z(f)表示由芯片焊盤看到的電源分配網絡阻抗曲線。

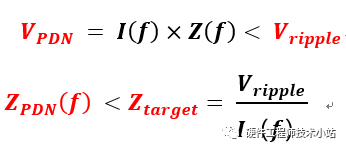

這一壓降表示VRM輸出的恒定電壓芯片是得不到的,在進入芯片前已被改變。芯片焊盤上的電壓變化必須小于某一電壓噪聲誤差,比如要求為額定電壓的5%。這就要求電源分配網絡阻抗必須低于某一阻抗值,即目標阻抗:

VPDN表示電源分配網絡上實際的噪聲壓降(V);

Vripple表示芯片允許的電壓噪聲誤差(V);

I(f)表示芯片消耗電流的頻譜(A);

Z PDN (f)表示由芯片看過去的電源分配網絡阻抗曲線(Ω);

Ztarget表示電源分配網絡所允許的最大阻抗(Ω)

因此電源分配網絡上的軌道塌陷或電壓噪聲的根本原因在于,流過電源分配網絡阻抗的芯片電流導致互連上出現了電壓降。要保持芯片供電電壓穩定,就需要保持電源分配網絡阻抗低于目標阻抗,這就電源分配網絡設計中最根本的指導原則

如何理解去耦電容?

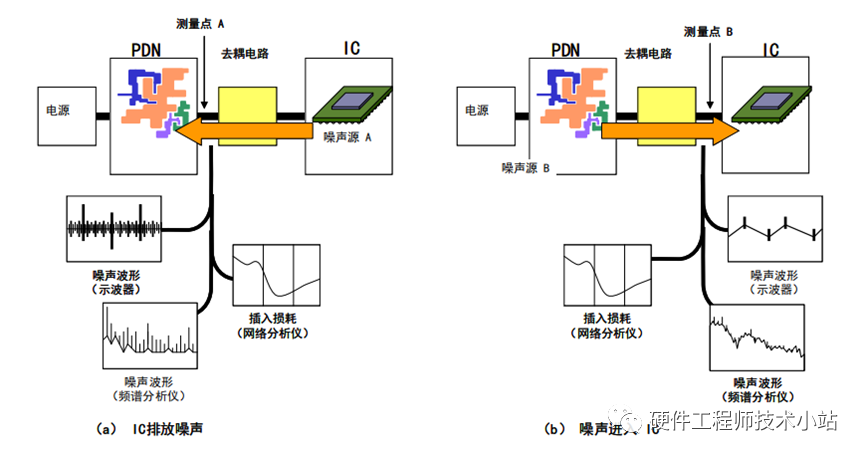

為了使負載芯片的供電滿足要求,通常會在芯片的周圍用很多電容連接到電源平面上,這些電容稱為去耦電容。 去耦電路主要有三種功能:①抑制噪聲,②暫時供應電流,③形成信號返回通道。 在這三種功能中,第一種功能抑制噪聲是針對 IC 電源泄漏的噪聲進行過濾,并且切斷從外部進入 IC 的噪聲。當懷疑噪聲從 IC 泄漏時,在 PDN(測量點 A)側進行測量,當懷疑噪聲從外源進入 IC 時,在 IC電源端子(測量點 B)側進行測量。

去耦電容之所以能夠減小電源噪聲,可以從多個角度進行解釋,下面從儲能和阻抗的兩個角度進行說明去耦電容減小電源噪聲的原理

1、 從儲能的角度來理解

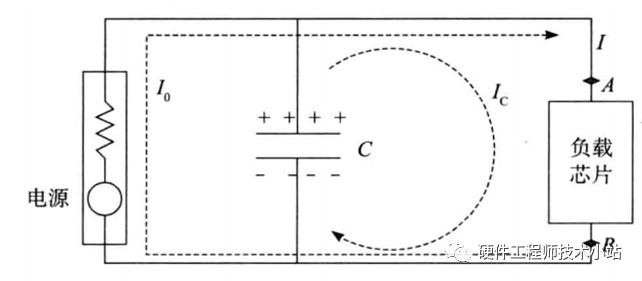

帶有去耦電容的供電系統可以等效為下圖所示的簡化結構。我們把電源系統分成電源模塊和去耦電容兩部分,圖中電容代表了所有外加去耦電容的組合,電源模塊和去耦電容聯合起來共同為AB兩點之間的負載芯片供電。

圖 去耦電容儲能等效電路

當負載電流保持不變,穩態情況下,負載芯片處的電壓是恒定的,因而電容兩端電壓也是恒定的,與負載兩端電壓一致,流經電容的電流 IC為0,負載電流由電源模塊提供,即圖中的IO此時電容兩端存在電壓,因此電容上存儲了相當數量的電荷,其電荷數量和電容量有關。

當負載電流發生瞬間變化時,由于負載芯片內部晶體管電平轉換速度極快,必須在極短的時間內為負載芯片提供足夠的電流。但是穩壓電源無法很快響應負載電流的變化,電流I不會馬上變化滿足負載瞬態電流的要求,因此負載芯片感受到的電壓會降低。去耦電容也同時感受到電壓變化,對于電容來說電壓變化必然產生電流,此時電容對負載放電,電流IC不再為0,要為負載芯片提供電流。根據電容上電壓和電流之間的關系∶

理想情況下,只要電容量C足夠大,放電并為負載提供瞬態電流只會引起電容兩端很小的電壓變化,這樣就保證了負載芯片電壓的變化在容許的范圍內。這里,相當于電容預先存儲了一部分電能,在負載需要的時候釋放出來,即電容是儲能元件。儲能電容的存在使負載消耗的能量得到快速補充,因此保證了負載兩端電壓不至于有太大變化,此時電容擔負的是局部電源的角色。

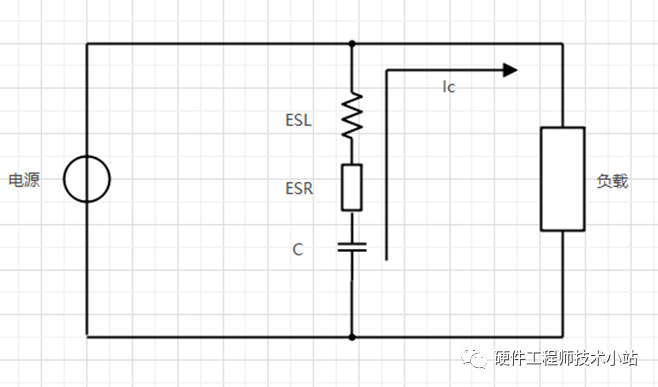

從儲能角度理解電容容易造成一種錯覺,認為電容越大越好。而且容易誤導大家認為儲能作用發生在低頻段,不容易向高頻擴展。實際上,去耦電容工作在全頻段。我們把一個去耦電容中的一個拿出來進行分析,實際電容的電路模型如下所示,由三部分組成:C+ESR+ESL

假設在低頻段,由于低頻信號在電感上產生的感抗可以忽略,所以低頻段電容的ESL可以近似為0,當負載瞬間需要大電流的時候,電容通過ESR給負載供電,實時性很高,只是ESR消耗了一部分電量。由于頻率比較低,所以放電時間(頻率的倒數)比較長,所以需要電容的容量大一些來滿足長時間放電。

假設我們將頻率提高到MHz級別,那么當負載瞬時變化的時候,ESL形成的感抗不容忽視,這個感抗會形成反向電動勢阻止電容給負載充電,負載上獲得的電流瞬態性能比較差,盡管電容容量很大,但由于ESL較大(一般電容的容量越大,電容本身的ESL也就越大),此時的大容量儲能發揮不了作用。實際上,頻率較高,電容給負載供電的時間縮短(頻率的倒數),也不需要電容有那么大的容量。對于高頻,關鍵的因素是ESL,要降低電容的ESL,選擇小封裝的小電容,ESL顯著降低,這就是為什么我們高頻選擇小電容的原因,另外走線長度引入的電感也會折算到ESL參數里,所以小電容一定要靠近pin。

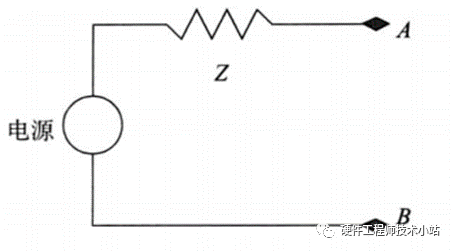

2、 從阻抗的角度來理解

從阻抗的角度理解電容退耦,可以給我們設計電源分配系統帶來極大的方便。實際上,電源分配系統設計的最根本的原則就是使阻抗最小。最有效的設計方法就是在這個原則指導下產生的。根據上圖我們去掉負載芯片,僅觀察供電系統本身,如下圖所示。從 AB兩點向左看過去,穩壓電源以及去耦電容組合在一起,可以看成是一個復合的電源系統。對這個復合電源系統的要求是;不論 AB 兩點間負載的瞬態電流如何變化,都能保證 AB 兩點間的電壓保持穩定,即 AB兩點間電壓變化很小。

我們可以用一個等效電源模型表示上面這個復合的電源系統:

對于這個電路可寫出如下等式∶△V= Z·△I

我們的最終設計目標是,不論 AB兩點間負載瞬態電流如何變化,都要保持 AB 兩點間電壓變化范圍很小,根據上式,這要求電源系統的阻抗 Z要足夠小。電源系統中去耦電容和電源模塊是并聯關系,對于變化的瞬態電流,由于具有交流特性,去耦電容表現出低阻抗的特性(通交流,阻直流)。從端口看進去對交流成分表現出的阻抗很低。因此從等效的角度出發,可以說去耦電容降低了復合電源系統的阻抗。電源PDN做的就是如何在各個頻率段下阻抗盡可能小。理論上,并聯無數個電容,電源內阻總可以無限接近于0,從而電源無限接近于恒壓源或恒流源。

總結:

綜上而言,PCB電容都不是理想電容,而是存在寄生效應的(ESL、ESR);

PCB電容的阻抗特性在自諧振頻率點阻抗最小,低于自諧振頻率阻抗呈容性,高于自諧振頻率呈感性;

通常容值越小,電容的自諧振頻率越高,可用于更高的頻率去耦。因為要抑制高頻噪聲,小電容的回路電感要控制很小,所以需要放置到離電源地管腳很近的位置并合理扇出,多個小電容并聯可以降低回路電感;

不同容值的自諧振頻率點不同,不同容值的去耦電容并聯可以取得更大范圍內的頻率去耦,在工程上通常用不同數量級容值的電容搭配進行設計去耦方案。

-

寄存器

+關注

關注

31文章

5336瀏覽量

120244 -

微處理器

+關注

關注

11文章

2259瀏覽量

82407 -

晶體管

+關注

關注

77文章

9684瀏覽量

138091 -

寄生電感

+關注

關注

1文章

155瀏覽量

14595 -

電源芯片

+關注

關注

43文章

1092瀏覽量

77032

發布評論請先 登錄

相關推薦

電源紋波和噪聲的測試測量和分析

基于FPGA的軟硬件協同測試設計影響因素分析與設計實現

【硬件篇之電源紋波噪聲測試】

硬件測試-噪聲的測試分析(1)

硬件測試-噪聲的測試分析(1)

評論