基于DWC2的USB驅動開發-0x08 GLPI接口詳解 (qq.com)

1.1 前言

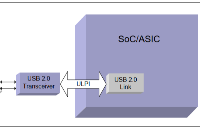

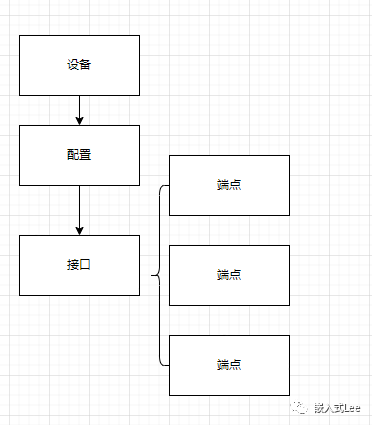

進行USB驅動開發,有必要了解整個數據流涉及的設備,而PHY是重要的一環,它負責物理層的處理,是模擬數字的橋梁。而PHY的了解重點是其和LINK之間的接口,USB中PHY和LINK之間的標準接口是UTMI,而ULPI是其低引腳的實現。

介紹ULPI之前有必要先了解下GLPI,因為ULPI是基于GLPI的一個具體的實現。

GLPI即Generic Low Pin Interface,通用低引腳接口,是應用于LINK和PHY之間的接口。可以基于此接口定義特定應用的接口,也就是該接口規范是一個通用的接口設計,可以基于此有具體的應用實現,比如基于該接口實現UTMI協議的低引腳接口即ULPI。

1.2信號

- GLPI定義了如下的信號,這些信號是通用的,可以用于傳輸不同的數據類型。根據應用的不同,數據流可以用于發送和接收數據包、訪問寄存器集、生成中斷,甚至重新定義接口本身。

- 所有信號都是和clock同步的,如果沒有clock則所有信號也可以是異步的。也就是規范本身并沒有完全限定死一定要clock,一定要是同步的。

- 作為通用接口,規范并不規定數據流本身,數據流定義是特定應用實現決定的,只要具體的實現明確定義,實現互操作性即可。

- 通常來說控制信號dir、stp和nxt是在假設PHY是數據總線的主機的情況下指定的。當然為了通用性,也并沒有完全限定死。如果需要,實現也可以將LINK定義為主機此時則控制信號的方向和前者要顛倒過來。

| 信號 | 方向(以PHY的角度看) | 描述 |

|---|---|---|

| PHY****接口 | 以下都是以PHY作為主機描述 | |

| clock | I/O | 接口時鐘.雙向都可以,即可以LINK產生該時鐘也可以PHY產生該時鐘,即對應于PHY時鐘的兩種模式,后面文章會講到.如果有clock所有信號都是和clock同步的.當然本規范也沒有限定死,即實現也可以沒有clock則所有信號都是異步的。所有信號和clock的上升沿同步。 |

| data | I/O | 雙向數據總線,空閑時LINK驅動為低,LINK和PHY驅動為非0的數據則表示有數據傳輸。(為什么? 如果一方驅動為0則另一方怎么驅動? 因為誰低誰強) .從后面總線權限可以看出不會出現主從都驅動總線的情況,?因為總線所有權由主機調度,且由dir決定。并且驅動為0只是一個特殊值,用于區別其他正常數據的情況,理論上驅動為全1也?可以。這里為什么LINK一定要發一個數據是因為PHY不發數據就拉低dir監聽數據,所以CLK上升沿總是會采集到數據用一個特殊值來表示空閑無效數據?。 總線的擁有權是由主機決定的,比如PHY作為主機則由PHY驅動dir來決定.在clock的上升沿同步數據即單邊沿模式.當然實現也可以設計為雙邊沿傳輸數據模式。 |

| dir | OUT | 主機驅動dir決定data總線的所有權.如果PHY有數據需要傳輸給LINK,則PHY驅動dir為高擁有總線.如果PHY沒有數據要傳輸給LINK則拉低dir,表示LINK擁有data總線,此時PHY監聽總線有非0 的數據則表示LINK發過來了數據給PHY.如果PHY不能接收LINK的數據也可以拉高dir.比如PHY的PLL沒有穩定時就會拉高dir,此時LINK不能往PHY發非0數據. |

| stp | IN | 停止.LINK拉高該信號1個時鐘來停止當前的數據流(LINK到PHY的或者PHY到LINK的).如果此時是LINK發送數據到PHY,LINK拉高stp則表示前一個時鐘的數據是最后一個數據.原文是stp indicates thelast byte of data was on the bus in the previous cycle 我覺的從后面波形圖理解來說應該不是前一個時鐘而應該就是本STP拉高對應的CLK上升沿的數據是最后一個數據。 如果此時是PHY發送數據到LINK,LINK拉高stp則PHY會強制停止本次數據發送,并且PHY會拉低dir,表示交出數據總線控制權給LINK。 |

| nxt | OUT | PHY拉高nxt表示是否還有數據或者是否接收到數據.1.如果LINK發送數據給PHY,PHY拉高nxt表示當前字節被PHY接收了.LINK可以在下一個時鐘繼續發送數據給PHY.。2.如果是PHY發送數據給LINK則PHY拉高nxt表示后面還有數據LINK可以繼續讀。 |

1.3 協議

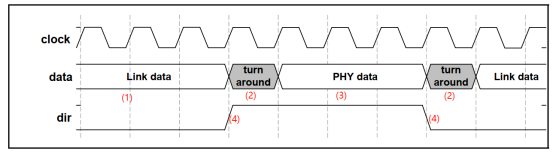

1.3.1 總線所有權

非特殊實現都是PHY作為主機,PHY驅動dir來決定總線的所有權。

PHY需要發送數據時拉高dir,其他時候都是拉低dir監聽總線。

如果LINK需要獲取總線權可以等PHY發送完不再需要發送數據時PHY主動拉低dir,LINK也可以主動拉高stp一個時鐘來結束PHY的發送,讓PHY主動讓出總線所有權,讓LINK來發送數據,這種情況LINK主動請求的則必須進行一次數據發送,PHY才會重新拉高dir重新擁有總線。

dir為0時LINK擁有總線所有權,LINK可以往data總線發數據,

dir為1時PHY擁有總線所有權,PHY可以往data總線發數據,

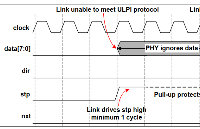

所有信號都是和CLK同步的,且在CLK的上升沿修改數據,所以CLK的上升沿時dir翻轉,

dir翻轉時的那一個CLK叫做turnaround,LINK和PHY都不能往data總線發送數據,LINK和PHY也要丟棄該時候的總線數據。

所以在實現時dir可以直接用于控制PHY和LINK的輸出緩沖器,只是PHY和LINK兩邊的使能電平是反的。

- dir為低,LINK擁有總線所有權,LINK可以往總線發數據

- dir翻轉時對應的那一個CLK,LINK和PHY都不能發數據,總線上的數據無效,即turnaround

- dir為高,PHY擁有總線所有權,PHY可以往總線發數據

- dir和clock同步,dir總是在clk的上升沿翻轉

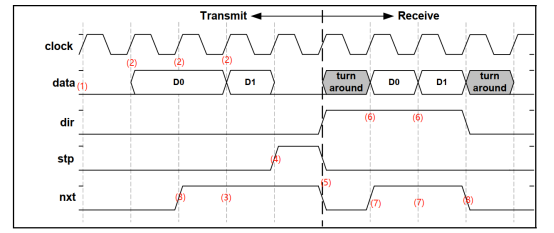

1.3.2 傳輸數據

- dir為0, LINK擁有總線所有權,而LINK又沒有數據要發給PHY,此時就是空閑階段,LINK驅動data總線為0,此時PHY監聽到全0就認為是無效數據.

- dir為0, LINK擁有總線所有權,LINK有數據要發送給PHY,則LINK驅動總線為非0值D0。

但是此時PHY拉低了nxt,表示不能接收,所以LINK只能下一個CLK重發D0

- PHY收到LINK發送過來的數據D0,拉高nxt,表示PHY收到了,這樣LINK可以繼續發D1。

- LINK主動拉高stp表示結束傳輸

- stp保持高一個CLK后拉低,此時PHY也會拉低nxt,如果PHY需要發送數據,需要擁有總線權則會拉高dir,否則會繼續拉低dir等待LINK的下一次傳輸。上圖中dir拉高了,說明PHY需要發數據了,dir拉高的一個CLK內是turn around總線無效。

- Turn around之后PHY發送數據。

- PHY發送數據,同時拉高nxt表示后續還有數據要發。

- PHY后面沒有數據要發了拉低nxt,并且拉低dir交出總線所有權。

所以PHY拉低nxt可以用于掐斷數據傳輸(LINK或者PHY發送的數據), 在傳輸期間,nxt可以在拉高stp的相同周期中拉高。

從以上可以看出由LINK發送最后一個字節,轉到PHY發送第一個字節需要2個周期,即stp要一個周期,turn around需要一個周期。

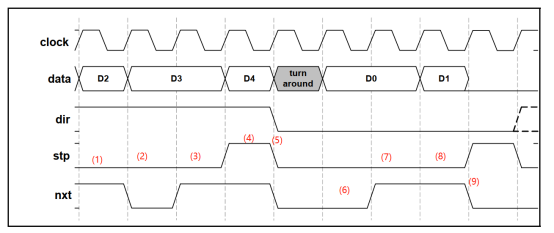

1.3.3 停止傳輸數據

PHY可以拉高dir用于結束LINK的發送

LINK可以拉高stp一個時鐘來結束PHY的發送,此時PHY需要無條件拉低dir,準備接收LINK的數據。PHY必須等接收完LINK的數據才能重新拉高dir。也就是LINK拉高stp以結束上一次PHY的傳輸,告訴PHY強制拉低dir來使得LINK擁有總線權,這也是LINK主動需要切換到總線所有權的一種方式,這時則LINK必須進行一次發送,只有這樣PHY才會重新拉高dir 使得PHY擁有總線權。這里有個未定義行為,假設LINK進行了stp拉高但是又不發送數據或者一直發送數據不stp,那么PHY是不是只能一直等待,不能重新拉高dir擁有總線權了?。

- dir為高 PHY在發送數據D2,nxt為高說明后面還有數據待發送

- dir為高 PHY在發送數據D3,nxt為低說明后面的數據無效

- 這個CLK由于前面一次nxt為低,所以數據無效,LINK不接收, nxt拉高說明下一個CLK PHY又有數據要發

- 這個CLK PHY發送D4, LINK接收,nxt為高表示PHY還有數據要發,但是在此時LINK想要發送數據,于是拉高stp一個CLK.

- Stp拉高一個CLK后要拉低,此時PHY無條件拉低dir交出總線所有權,同時拉低nxt.

- 一個turn around時鐘后,LINK發送數據D0,此時PHY拉低nxt為0表示PHY沒有準備好接收數據

- 由于上一次PHY沒有準備好接收數據,LINK只能重新發D0,此時PHY拉高nxt表示接收了數據D0

- LINK繼續發送D1,PHY拉高nxt表示接收了數據D1

- LINK發送stp主動結束發送,此時PHY也要拉低nxt。

之后PHY再看需要是不是要發送數據來決定是拉高還是拉低dir。

1.4 總結

GLPI的接口是比較簡單的,需要注意主從機,PHY是主機LINK是從機,

Stp是從機驅動,nxt和dir是主機驅動。

需要注意總線的擁有權由主機決定,主機需要發送是拉高dir擁有總線權,其他時候拉低dir交出總線權監聽總線。而LINK可以在dir為高,PHY在發送數據時主動拉高stp一個CLK來請求PHY交出總線權,PHY必須無條件交出,并且必須等LINK發送完數據之后才能重新擁有總線。

所以關鍵點是了解誰驅動什么信號,總線擁有權的切換,了解這兩點就基本了解了該接口的邏輯了。

1.5 參考

《UTMI+ Low Pin Interface (ULPI) Specification Revision 1.1 October 20, 2004》

審核編輯:湯梓紅

-

接口

+關注

關注

33文章

8575瀏覽量

151015 -

usb

+關注

關注

60文章

7936瀏覽量

264474 -

信號

+關注

關注

11文章

2789瀏覽量

76730 -

總線

+關注

關注

10文章

2878瀏覽量

88051 -

DWC2

+關注

關注

0文章

35瀏覽量

125

發布評論請先 登錄

相關推薦

基于DWC2的USB驅動開發-0x02 DWC2 USB2.0 IP功能特征介紹

基于DWC2的USB驅動開發-0x07 DWC2 USB2.0 IP 配置參數

基于DWC2的USB驅動開發-高速設備枚舉為全速設備問題案例分析

基于DWC2的USB驅動開發-發送相關的寄存器DMA寄存器詳解

基于DWC2的USB驅動開發-USB包詳解

如何對基于hal庫的DWC2 USB IP進行調試呢

基于DWC2的USB驅動開發-0x0A ULPI接口同步模式介紹

基于DWC2的USB驅動開發-0x08 GLPI接口詳解

基于DWC2的USB驅動開發-0x08 GLPI接口詳解

評論