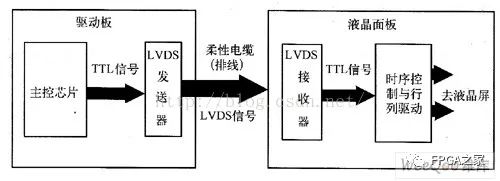

1.1.1 LVDS接口分類

1.1.1.1 單路6bit LVDS

這種接口電路中,采用單路方式傳輸,每個基色信號采用6位數(shù)據(jù),共18位RGB數(shù)據(jù),因此,也稱18位或18bit LVDS接口。此,也稱18位或18bit LVDS接口。

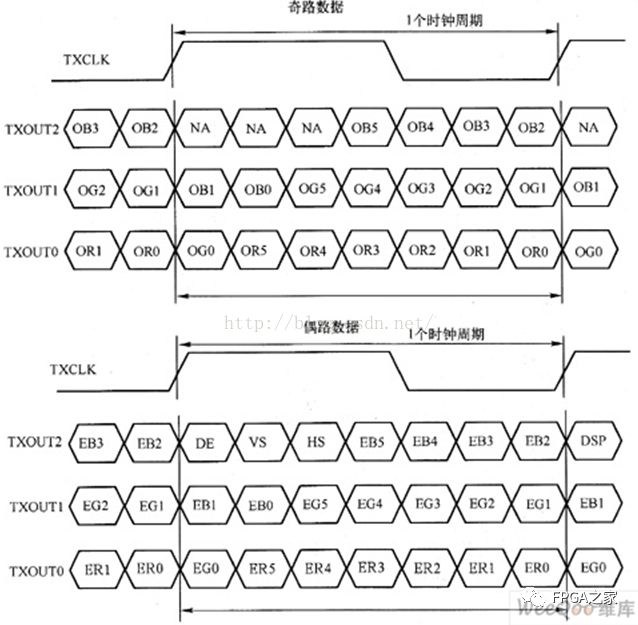

1.1.1.2 雙路6bit LVDS

這種接口電路中,采用雙路方式傳輸,每個基色信號采用6位數(shù)據(jù),其中奇路數(shù)據(jù)為18位,偶路數(shù)據(jù)為18位,共36位RGB數(shù)據(jù),因此,也稱36位或36bit LVDS接口。

1.1.1.3 單路8bit LVDS

這種接口電路中,采用單路方式傳輸,每個基色信號采用8位數(shù)據(jù),共24位RGB數(shù)據(jù),因此,也稱24位或24bit LVDS接口。

1.1.1.4 雙路8bit LVDS

這種接口電路中,采用雙路方式傳輸,每個基色信號采用8位數(shù)據(jù),其中奇路數(shù)據(jù)為24位,偶路數(shù)據(jù)為24位,共48位RGB數(shù)據(jù),因此,也稱48位或48bitLVDS接口

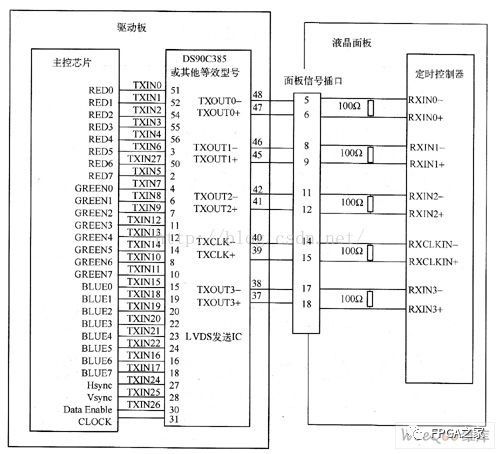

1.1.2 LVDS發(fā)送芯片介紹

典型之LVDS發(fā)送芯片分為四通道、五通道和十通道幾種,下面簡要進行介紹。

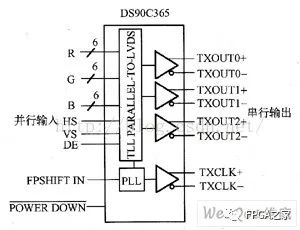

1.1.2.1四通道LVDS發(fā)送芯片

圖2 所示為四通道LVDS發(fā)送芯片內(nèi)部框圖。包含了三個數(shù)據(jù)信號(其中包括RGB、數(shù)據(jù)使能DE、行同步信號HS、場同步信號VS)通道和一個時鐘信號發(fā)送通道。

4通道LVDS發(fā)送芯片主要用于驅動6bit液晶面板。使用四通道LVDS發(fā)送芯片可以構成單路6bit LVDS接自電路和奇/偶雙路6bit LVDS接口電路。

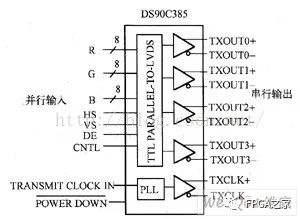

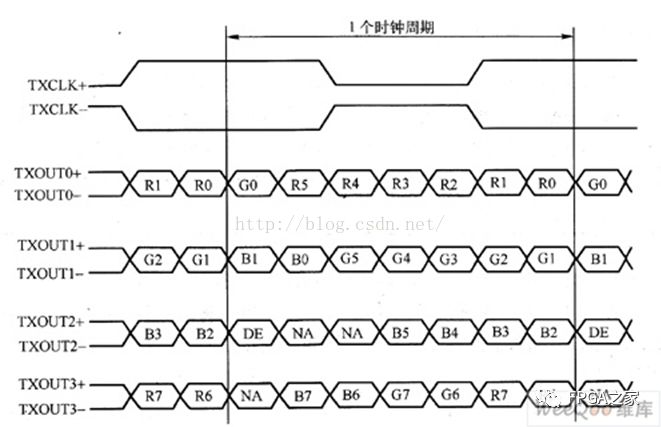

1.1.2.2 五通道LVDS發(fā)送芯片

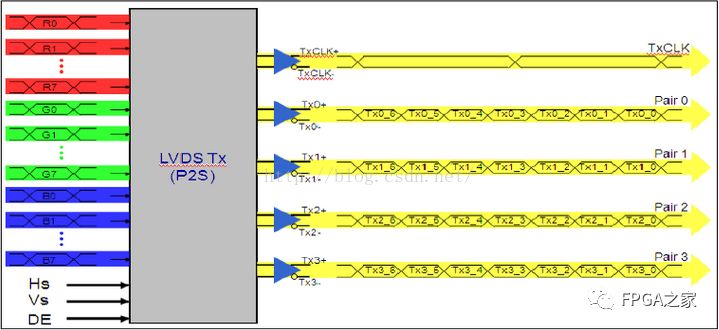

圖3 所示為五通道LVDS發(fā)送芯片(DS90C385)內(nèi)部框圖。包含了四個數(shù)據(jù)信號(其中包括RGB、數(shù)據(jù)使能DE、行同步信號HS、場同步信號VS)通道和一個時鐘信號發(fā)送通道。

五通道LVDS發(fā)送芯片主要用于驅動8bit液晶面板。使用五通道LVDS發(fā)送芯片主要用來構成單路8bit LVDS接口電路和奇/偶雙路8bitLVDS接口電路。

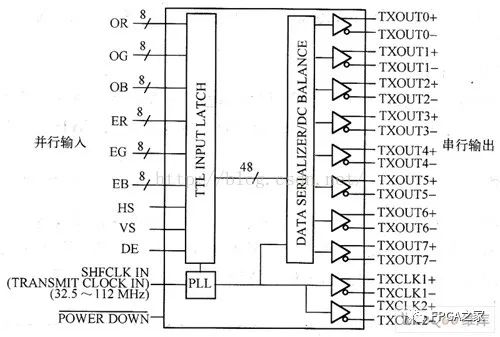

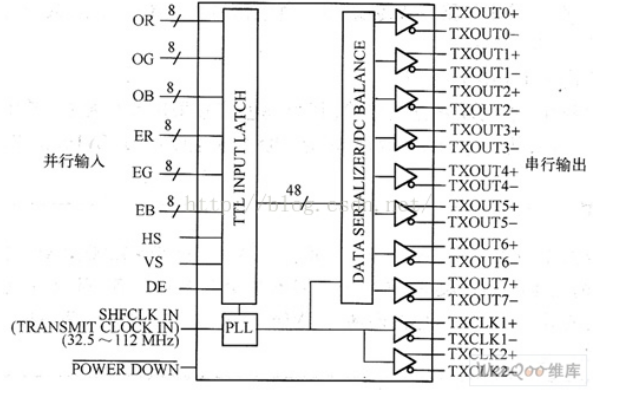

1.1.2.3 十通道LVDS發(fā)送芯片

圖4所示為十通道LVDS發(fā)送芯片(DS90C387)內(nèi)部框圖。包含了八個數(shù)據(jù)信號(其中包括RGB、數(shù)據(jù)使能DE、行同步信號HS、場同步信號VS)通道和兩個時鐘信號發(fā)送通道。

十通道LVDS發(fā)送芯片主要用于驅動8bit液晶面板。使用十通道LVDS發(fā)送芯片主要用來構成奇/偶雙路8bit LVDS位接口電路。

在十通道LVDS發(fā)送芯片中,設置了兩個時鐘脈沖輸出通道,這樣做之目之是可以更加靈活之適應不同類型之LVDS接收芯片。當LVDS接收電路同樣使用一片十通道LVDS接收芯片時,只需使用一個通道之時鐘信號即可;當LVDS接收電路使用兩片五通道LVDS接收芯片時,十通道LVDS發(fā)送芯片需要為每個LVDS接收芯片提供單獨之時鐘信號。

1.1.3LVDS發(fā)送芯片之輸入與輸出信號

1.1.3.1 LVDS發(fā)送芯片之輸入信號

LVDS發(fā)送芯片之輸入信號來自主控芯片,輸入信號包含RGB數(shù)據(jù)信號、時鐘信號和控制信號三大類。為了說明之方便,將RGB信號以及數(shù)據(jù)選通DE和行場同步信號都算作數(shù)據(jù)信號。

輸入數(shù)據(jù)信號

在供6bit液晶面板使用之四通道LVDS發(fā)送芯片中,共有十八個RGB信號輸入引腳;一個顯示數(shù)據(jù)使能信號DE(數(shù)據(jù)有效信號)輸入引腳;一個行同步信號HS輸入引腳;一個場同步信號VS輸入引腳。也就是說,在四通道LYDS發(fā)送芯片中,共有二十一個數(shù)據(jù)信號輸入引腳。

在供8bit液晶面板使用之五通道LVDS發(fā)送芯片中,共有二十四個RGB信號輸入引腳;一個顯示數(shù)據(jù)使能信號DE(數(shù)據(jù)有效信號)輸入引腳;一個行同步信號HS輸入引腳;一個場同步信號VS輸入引腳;也就是說,在五通道LVDS發(fā)送芯片中,共有二十八個數(shù)據(jù)信號輸入引腳。

應該注意的是,液晶面板的輸入信號中都必須要有DE信號,但有的液晶面板只使用單一的DE信號而不使用行場同步信號。因此,應用于不同的液晶面板時,有的LVDS發(fā)送芯片可能只需輸入DE信號,而有的需要同時輸入DE和行場同步信號。

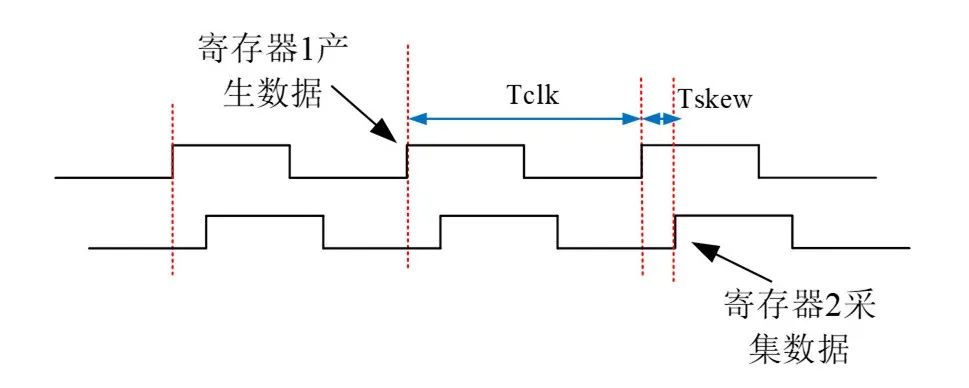

輸入時鐘信號:即像素時鐘信號,也稱為數(shù)據(jù)移位時鐘(在LVDS發(fā)送芯片中,將輸入之并行RGB數(shù)據(jù)轉換成串行數(shù)據(jù)時要使用移位寄存器)。像素時鐘信號是傳輸數(shù)據(jù)和對數(shù)據(jù)信號進行讀取之基準。

待機控制信號(POWER DOWN):當此信號有效時(一般為低電平時),將關閉LVDS發(fā)送芯片中時鐘PLL鎖相環(huán)電路之供電,停止IC之輸出。

數(shù)據(jù)取樣點選擇信號:用來選擇使用時鐘脈沖之上升沿還是下降沿讀取所輸入之RGB數(shù)據(jù)。有之LVDS發(fā)送芯片可能并不設置待機控制信號和數(shù)據(jù)取樣點選擇信號,但也有之除了上述兩個控制信號還設置有其他一些控制信號。

1.1.3.2LVDS發(fā)送芯片之輸出信號

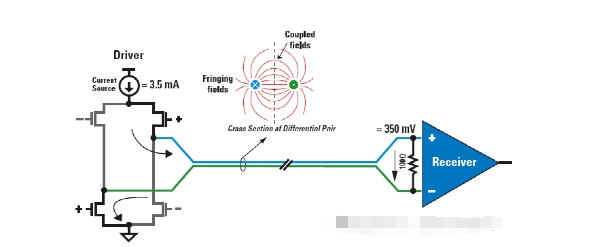

LVDS發(fā)送芯片將以并行方式輸入的TTL電平RGB數(shù)據(jù)信號轉換成串行之LVDS信號后,直接送往液晶面板側之LVDS接收芯片。

LVDS發(fā)送芯片的輸出是低擺幅差分對信號,一般包含一個通道的時鐘信號和幾個通道的串行數(shù)據(jù)信號。由于LVDS發(fā)送芯片是以差分信號的形式進行輸出,因此,輸出信號為兩條線,一條線輸出正信號,另一條線輸出負信號。

時鐘信號輸出:LVDS發(fā)送芯片輸出之時鐘信號頻率與輸入時鐘信號(像素時鐘信號)頻率相同。時鐘信號的輸出常表示為:TXCLK+和TXCLK-,時鐘信號占用LVDS發(fā)送芯片的一個通道。

LVDS串行數(shù)據(jù)信號輸出:對于四通道LVDS發(fā)送芯片,串行數(shù)據(jù)占用三個通道,其數(shù)據(jù)輸出信號常表示為TXOUT0+、TXOUT0-,TXOUT1+、TXOUT1-,TXOUT2+、TXOUT2-。

對于五通道LYDS發(fā)送芯片,串行數(shù)據(jù)占用四個通道,其數(shù)據(jù)輸出信號常表示為TXOUT0+、TXOUT0-,TXOUT1+、TXOUTI-,TXOUT2+、TXOUT2-,TXOUT3+、TXOUT3-。

對于十通道LVDS發(fā)送芯片,串行數(shù)據(jù)占用八個通道,其數(shù)據(jù)輸出信號常表示為TXOUT0+、TXOUT0-,TXOUT1+、TXOUT1-,TXOUT2+、TXOUT2-,TXOUT3+、TXOUT3-,TXOUT4+、TXOUT4-,TXOUT5+、TXOUT5-,TXOUT6+、TXOUT6-,TXOUT7+、TXOLT7-。

注意:

如果只看電路圖,是不能從LVDS發(fā)送芯片的輸出信號TXOUT-、TXOUT0+中看出其內(nèi)部到底包含哪些信號數(shù)據(jù),以及這些數(shù)據(jù)是怎樣排列的(或者說這些數(shù)據(jù)的格式是怎樣額)。事實上,不同廠家生產(chǎn)的LVDS發(fā)送芯片,其輸出數(shù)據(jù)排列方式可能是不同的。因此,液晶顯示器驅動板上的LVDS發(fā)送芯片的輸出數(shù)據(jù)格式必須與液晶面板LVDS接收芯片要求的數(shù)據(jù)格式相同,否則,驅動板與液晶面板不匹配。這也是更換液晶面板時必須考慮的一個問題。

如果表示明白,你就數(shù)帶 “+-”的這種信號線一共有幾對,

有10對的減掉2對(時鐘信號)就是雙8。

有8對的減掉2對 (時鐘信號)就是雙6。

有5對的減掉1對(時鐘信號)對是單8。

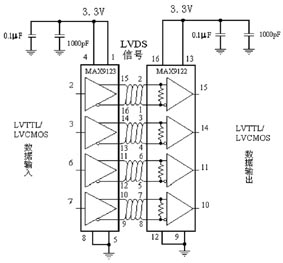

有4對的減掉1對 (時鐘信號)是單6。

如果既無資料,也看不清標識,最簡單的辦法就是看看里面的電路,一般每對數(shù)據(jù)線之間都有一個100歐姆的電阻,數(shù)電阻的個數(shù),看到4個的話就是單口6位顏色的屏,看到8個的話就是雙口六位,5個的話一般是單口8位,有10個一般就是雙口8位。

1.1.4LVDS數(shù)據(jù)輸出格式

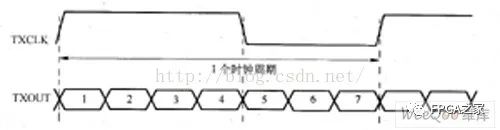

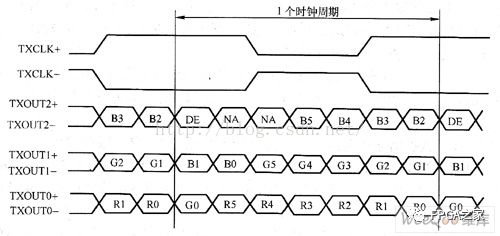

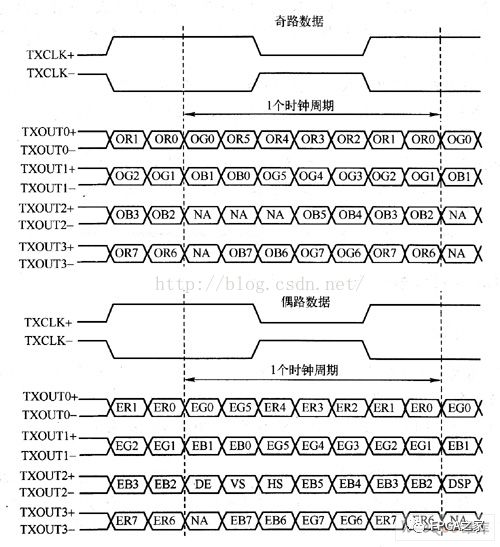

LVDS發(fā)送芯片在一個時鐘脈沖周期內(nèi),每個數(shù)據(jù)通道都輸出7bit的串行數(shù)據(jù)信號,而不是常見的8bit數(shù)據(jù),如圖5所示

在LCD液晶屏中,需要輸出到顯示屏的信號是并行的圖像信號和控制信號,而LVDS信號是串行傳輸?shù)模栽诎l(fā)送端需要將并行數(shù)據(jù)轉換為串行數(shù)據(jù)。以8bit RGB顯示屏接口為例,每個顯示周期需要傳輸8bit的R信號,8bit的G 信號,8bit 的B信號,及VS,HS,DE信號,總共為27 BIT。而每對LVDS信號線在一個TX周期里只能傳輸7BIT數(shù)據(jù),所以需要4 對數(shù)據(jù)線,外加一對時鐘線。LVDS并串轉換如下圖所示:

上圖中的每一組對線稱為一個Pair,4組數(shù)據(jù)線加一對時鐘線稱為一個Channel,LVDS發(fā)送器總是將一個像素數(shù)據(jù)映射到(remapping)一個Channel的一個發(fā)送周期(TX CLK)中。

如果是6BIT 顯示屏,則并行數(shù)據(jù)有21位(18位RGB加3位控制信號),因此LVDS 接口每個Channel只需要 3對數(shù)據(jù)線和一對時鐘線。

如果是10BIT 顯示屏,則并行數(shù)據(jù)有33位(30位RGB 加3位控制信號),因此LVDS 接口每個Channel需要 5對數(shù)據(jù)線和一對時鐘線。

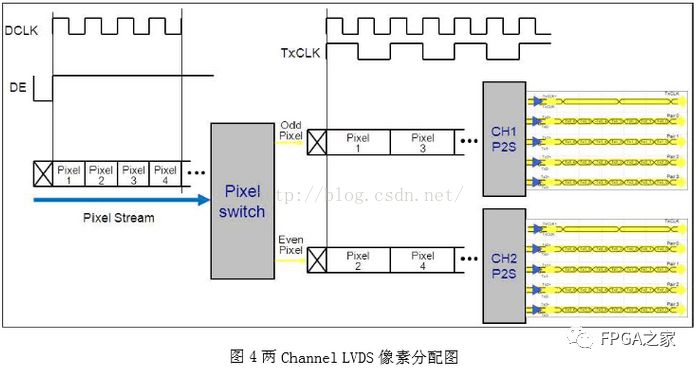

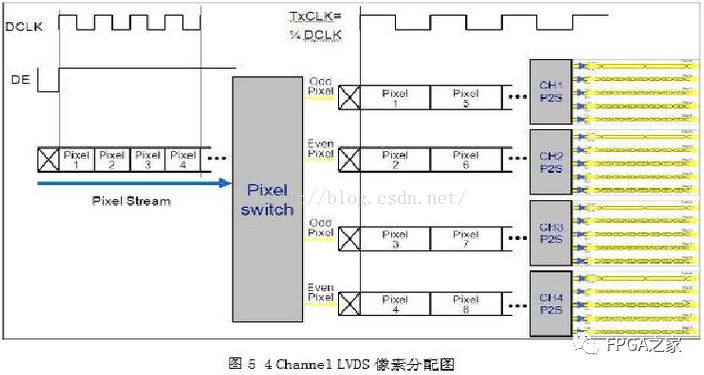

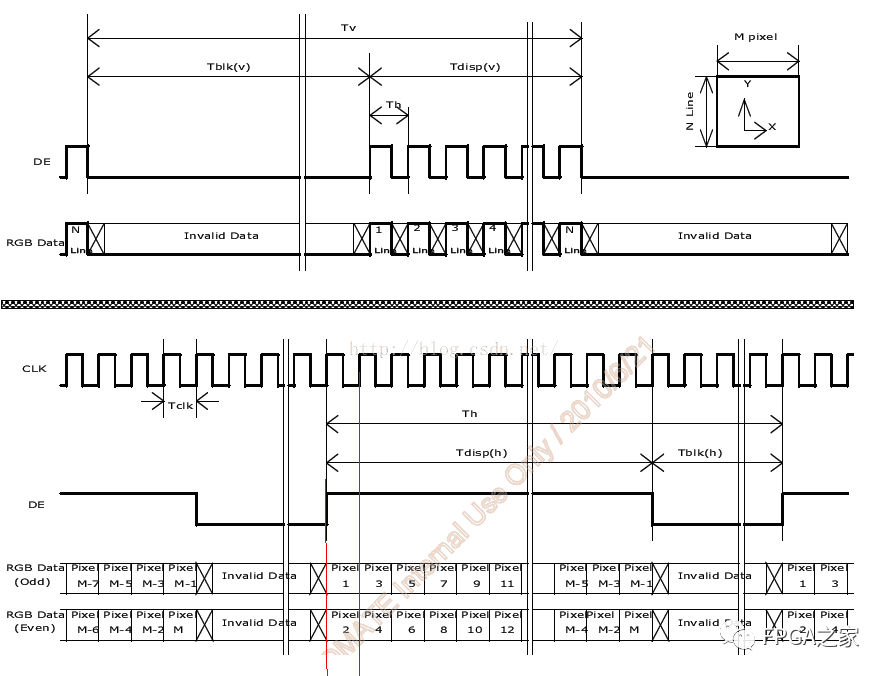

通常,LVDS接口的時鐘為20MHz 到85MHz,因此對于輸出像素時鐘低于85MHz的信號,只需一個Channel就可以;而對于輸出像素時鐘高于85MHZ的信號,比如1080P/60HZ的輸出,像素顯示時鐘為148.5MHz,就不能直接用一個Channel傳輸,而是將輸出的像素按順序分為奇像素和偶像素,將所有的奇像素用一組LVDS 傳輸,所有的偶像素用另外一組LVDS 傳輸。也就是說,需要兩個Channel來傳輸1080P/60HZ 的信號。對于像素顯示時鐘更高的信號,比如1080P/120HZ顯示,則需要4個Channel來傳輸。兩Channel、4Channel的像素分配分別如圖4、圖5所示:

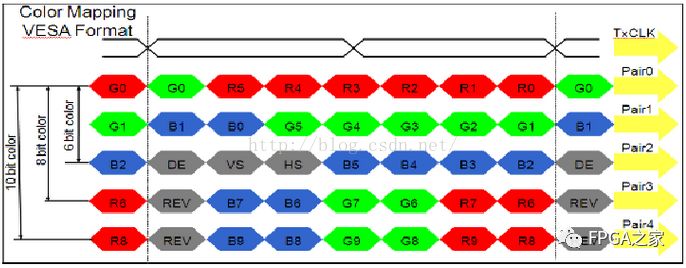

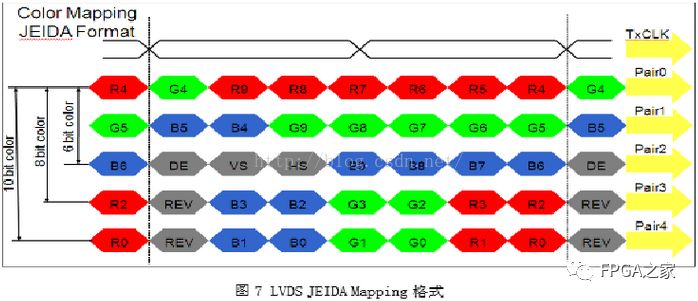

1.1.5 LVDS 數(shù)據(jù)映射標準

LVDS數(shù)據(jù)映射(MappingMapping)標準

LVDS接口電路中,將像素的并行數(shù)據(jù)轉換為串行數(shù)據(jù)的格式主要有兩種標準:VESA和JEIDA

VSEA標準如下圖所示:

JEIDA標準是由日本電子行業(yè)開發(fā)協(xié)會(JAPANELECTRONIC INDUSTRY DEVELOPMENT ASSOCIATION)制定的標準,其格式如下

對于JEIDA格式,需要注意的是,如果像素為6bit RGB,則每個通道只需要最上面的3對數(shù)據(jù)線,其中的R9…R4, G9…G4, B9…B4 對應實際的R5…R0, G5…G0, B5…B0;同樣,如果像素是 8 bit RGB,則每個通道只需要靠上面的4對數(shù)據(jù)線,其中的R9…R2, G9…G2, B9…B2 對應實際的R7…R0, G7…G0, B7…B0。

另外,COLOR MAPPING 也可以采用自定義格式,只要LVDS 發(fā)送端和接受端采用相同的映射順序,就可以顯示正確的色彩

1.1.6 LVDS 數(shù)據(jù)傳輸模式

LVDS信號傳輸分為DE MODE和SYNC MODE,DE mode需連接DE信號(data enable有效數(shù)據(jù)選通),SYNC mode還需連接HS(HSYNC行同步)、VS(VSYNC場同步)。

SYNC mode在現(xiàn)在的panel中已很少使用。下面是DE mode的數(shù)據(jù)形式。

1.1.7LVDS 數(shù)據(jù)格式詳解

LVDS發(fā)送芯片輸出信號的格式:即LVDS發(fā)送芯片輸入的RGB數(shù)據(jù),以及行同步信號HS、場同步信號VS、有效顯示數(shù)據(jù)使能信號DE在各個輸出通道中數(shù)據(jù)位的排列順序。

由于幾個大的LYDS芯片生產(chǎn)廠家制定了不同的標準,因此,存在著幾種不同的LVDS發(fā)送芯片數(shù)據(jù)輸出格式;

1.1.7.1單路 6BIT LVDS輸出

單路6bit LVDS發(fā)送芯片數(shù)據(jù)輸出格式:單路6bit LVDS發(fā)送電路使用四通道LVDS發(fā)送芯片,輸出信號格式如圖6所示。

圖中NA的意思是未使用。此例為控制信號僅使用DE的模式,未使用行同步信號HS和場同步信號VS。關于DE、IIS、VS信號的使用問題。當控制信號為DE+行場同步信號模式時,圖中的兩個NA更換為場同步信號VS和行同步信號HS。

1.1.7.2雙路6BIT LVDS輸出

雙路6bit LVDS發(fā)送芯片數(shù)據(jù)輸出格式:雙路6bit LVDS發(fā)送電路使用兩片四通道LVDS發(fā)送芯片,輸出信號格式如圖7所示。

從圖中可以看出,雙路6bit LVDS發(fā)送芯片數(shù)據(jù)輸出格式與單路6bit LVDS發(fā)送芯片數(shù)據(jù)輸出格式是相同的,只不過一路傳送奇數(shù)像素RGB數(shù)據(jù),另工路傳送偶數(shù)像素RGB數(shù)據(jù)。OR0、OR1、…中的“O”代表奇數(shù)像素,ER0、ER1、…中的“E”代表偶數(shù)像素。

1.1.7.3單路 6BIT LVDS輸出

單路8bit LVDS發(fā)送芯片數(shù)據(jù)輸出格式:單路8bit LVDS發(fā)送電路使用五通道LVDS發(fā)送芯片,輸出信號格式有多種,下面只介紹其中的兩種。

下圖所示為單路8bitLVDS發(fā)送芯片的另一種數(shù)據(jù)輸出格式。

所示格式中的控制信號僅使用DE模式,當控制信號為DE+行場同步信號模式時,第二數(shù)據(jù)通道TXOUT2中的兩個NA應更換為場同步信號VS和行同步信號HS(通過對驅動板編程可改寫)。

從以上兩種輸出格式中可以看出,數(shù)據(jù)信號的排列順序差別很大,不過,要想讓其排列一致,完全可以通過對驅動板編程來完成。

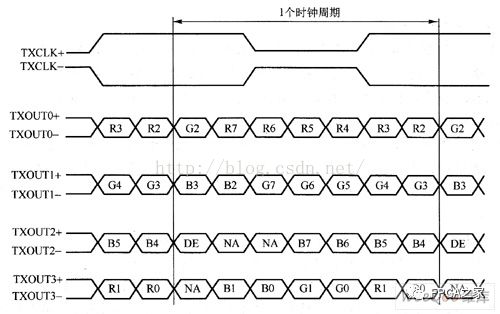

1.1.7.4雙路8BIT LVDS輸出

雙路8bit LVDS發(fā)送芯片數(shù)據(jù)輸出格式:雙路8bit LVDS發(fā)送電路使用兩片五通道LVDS發(fā)送芯片或一片十通道LVDS發(fā)送芯片,雙路8bit LVDS發(fā)送芯片數(shù)據(jù)輸出格式也有多種形式,所示是其中的一種。

審核編輯:湯梓紅

-

芯片

+關注

關注

459文章

52323瀏覽量

438226 -

接口

+關注

關注

33文章

8970瀏覽量

153397 -

RGB

+關注

關注

4文章

805瀏覽量

59716 -

lvds

+關注

關注

2文章

1121瀏覽量

67246 -

時序

+關注

關注

5文章

397瀏覽量

37846

原文標題:LVDS,接口,時序講解,非常好的文章

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

如何調(diào)整LVDS時鐘頻率和時序?

基于LVDS 技術的傳輸接口設計

lvds接口定義

LVDS接口電路及設計

基于FPGA的LVDS接口應用

LVDS接口有哪些分類

高速ADC與FPGA的LVDS數(shù)據(jù)接口中避免時序誤差的設計考慮

評論