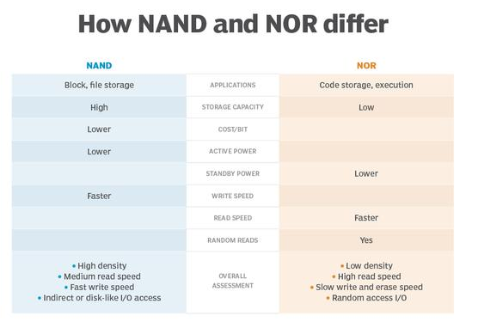

內存和NOR型閃存的基本存儲單元是bit,用戶可以隨機訪問任何一個bit的信息。而NAND型閃存的基本存儲單元是頁(Page)(可以看到,NAND型閃存的頁就類似硬盤的扇區,硬盤的一個扇區也為512字節)。每一頁的有效容量是512字節的倍數。所謂的有效容量是指用于數據存儲的部分,實際上還要加上16字節的校驗信息,因此我們可以在閃存廠商的技術資料當中看到“(512+16)Byte”的表示方式。目前2Gb以下容量的 NAND型閃存絕大多數是(512+16)字節的頁面容量,2Gb以上容量的NAND型閃存則將頁容量擴大到(2048+64)字節。

NAND型閃存以塊為單位進行擦除操作。閃存的寫入操作必須在空白區域進行,如果目標區域已經有數據,必須先擦除后寫入,因此擦除操作是閃存的基本操作。一般每個塊包含32個512字節的頁,容量16KB;而大容量閃存采用2KB頁時,則每個塊包含64個頁,容量128KB。

每顆NAND型閃存的I/O接口一般是8條,每條數據線每次傳輸(512+16)bit信息,8條就是(512+16)×8bit,也就是前面說的512 字節。但較大容量的NAND型閃存也越來越多地采用16條I/O線的設計,如三星編號K9K1G16U0A的芯片就是64M×16bit的NAND型閃存,容量1Gb,基本數據單位是(256+8)×16bit,還是512字節。

尋址時,NAND型閃存通過8條I/O接口數據線傳輸地址信息包,每包傳送8位地址信息。由于閃存芯片容量比較大,一組8位地址只夠尋址256個頁,顯然是不夠的,因此通常一次地址傳送需要分若干組,占用若干個時鐘周期。NAND的地址信息包括列地址(頁面中的起始操作地址)、塊地址和相應的頁面地址,傳送時分別分組,至少需要三次,占用三個周期。隨著容量的增大,地址信息會更多,需要占用更多的時鐘周期傳輸,因此NAND型閃存的一個重要特點就是容量越大,尋址時間越長。而且,由于傳送地址周期比其他存儲介質長,因此NAND型閃存比其他存儲介質更不適合大量的小容量讀寫請求。

決定NAND型閃存的因素有哪些?

1.頁數量

前面已經提到,越大容量閃存的頁越多、頁越大,尋址時間越長。但這個時間的延長不是線性關系,而是一個一個的臺階變化的。譬如128、256Mb的芯片需要3個周期傳送地址信號,512Mb、1Gb的需要4個周期,而2、4Gb的需要5個周期。

2.頁容量

每一頁的容量決定了一次可以傳輸的數據量,因此大容量的頁有更好的性能。前面提到大容量閃存(4Gb)提高了頁的容量,從512字節提高到2KB。頁容量的提高不但易于提高容量,更可以提高傳輸性能。我們可以舉例子說明。以三星K9K1G08U0M和K9K4G08U0M為例,前者為1Gb,512字節頁容量,隨機讀(穩定)時間12μs,寫時間為200μs;后者為4Gb,2KB頁容量,隨機讀(穩定)時間25μs,寫時間為300μs。假設它們工作在 20MHz。

讀取性能:NAND型閃存的讀取步驟分為:發送命令和尋址信息→將數據傳向頁面寄存器(隨機讀穩定時間)→數據傳出(每周期8bit,需要傳送512+16或2K+64次)。

K9K1G08U0M讀一個頁需要:5個命令、尋址周期×50ns+12μs+(512+16)×50ns=38.7μs;K9K1G08U0M實際讀傳輸率:512字節÷38.7μs=13.2MB/s;K9K4G08U0M讀一個頁需要:6個命令、尋址周期×50ns+25μs+(2K+64)× 50ns=131.1μs;K9K4G08U0M實際讀傳輸率:2KB字節÷131.1μs=15.6MB/s。因此,采用2KB頁容量比512字節也容量約提高讀性能20%。

寫入性能:NAND型閃存的寫步驟分為:發送尋址信息→將數據傳向頁面寄存器→發送命令信息→數據從寄存器寫入頁面。其中命令周期也是一個,我們下面將其和尋址周期合并,但這兩個部分并非連續的。

K9K1G08U0M寫一個頁需要:5個命令、尋址周期×50ns+(512+16)×50ns+200μs=226.7μs。K9K1G08U0M實際寫傳輸率:512字節÷226.7μs=2.2MB/s。K9K4G08U0M寫一個頁需要:6個命令、尋址周期×50ns+(2K+64)×50ns+ 300μs=405.9μs。K9K4G08U0M實際寫傳輸率:2112字節/405.9μs=5MB/s。因此,采用2KB頁容量比512字節頁容量提高寫性能兩倍以上。

3.塊容量

塊是擦除操作的基本單位,由于每個塊的擦除時間幾乎相同(擦除操作一般需要2ms,而之前若干周期的命令和地址信息占用的時間可以忽略不計),塊的容量將直接決定擦除性能。大容量NAND型閃存的頁容量提高,而每個塊的頁數量也有所提高,一般4Gb芯片的塊容量為2KB×64個頁=128KB,1Gb芯片的為512字節×32個頁=16KB。可以看出,在相同時間之內,前者的擦速度為后者8倍!

4.I/O位寬

以往NAND型閃存的數據線一般為8條,不過從256Mb產品開始,就有16條數據線的產品出現了。但由于控制器等方面的原因,x16芯片實際應用的相對比較少,但將來數量上還是會呈上升趨勢的。雖然x16的芯片在傳送數據和地址信息時仍采用8位一組,占用的周期也不變,但傳送數據時就以16位為一組,帶寬增加一倍。K9K4G16U0M就是典型的64M×16芯片,它每頁仍為2KB,但結構為(1K+32)×16bit。

模仿上面的計算,我們得到如下。K9K4G16U0M讀一個頁需要:6個命令、尋址周期×50ns+25μs+(1K+32)×50ns=78.1μs。

K9K4G16U0M實際讀傳輸率:2KB字節÷78.1μs=26.2MB/s。K9K4G16U0M寫一個頁需要:6個命令、尋址周期×50ns+ (1K+32)×50ns+300μs=353.1μs。K9K4G16U0M實際寫傳輸率:2KB字節÷353.1μs=5.8MB/s 可以看到,相同容量的芯片,將數據線增加到16條后,讀性能提高近70%,寫性能也提高16%。

5.頻率工作頻率的影響

NAND型閃存的工作頻率在20~33MHz,頻率越高性能越好。前面以K9K4G08U0M為例時,我們假設頻率為20MHz,如果我們將頻率提高一倍,達到40MHz,則K9K4G08U0M讀一個頁需要:6個命令、尋址周期×25ns+25μs+(2K+64)×25ns=78μs。K9K4G08U0M實際讀傳輸率: 2KB字節÷78μs=26.3MB/s。可以看到,如果K9K4G08U0M的工作頻率從20MHz提高到40MHz,讀性能可以提高近70%!當然,上面的例子只是為了方便計算而已。在三星實際的產品線中,可工作在較高頻率下的應是K9XXG08UXM,而不是K9XXG08U0M,前者的頻率目前可達33MHz。

6.制造工藝

制造工藝可以影響晶體管的密度,也對一些操作的時間有影響。譬如前面提到的寫穩定和讀穩定時間,它們在我們的計算當中占去了時間的重要部分,尤其是寫入時。如果能夠降低這些時間,就可以進一步提高性能。90nm的制造工藝能夠改進性能嗎?答案恐怕是否!目前的實際情況是,隨著存儲密度的提高,需要的讀、寫穩定時間是呈現上升趨勢的。前面的計算所舉的例子中就體現了這種趨勢,否則4Gb芯片的性能提升更加明顯。

綜合來看,大容量的NAND型閃存芯片雖然尋址、操作時間會略長,但隨著頁容量的提高,有效傳輸率還是會大一些,大容量的芯片符合市場對容量、成本和性能的需求趨勢。而增加數據線和提高頻率,則是提高性能的最有效途徑,但由于命令、地址信息占用操作周期,以及一些固定操作時間(如信號穩定時間等)等工藝、物理因素的影響,它們不會帶來同比的性能提升。

1Page=(2K+64)Bytes;1Block=(2K+64)B×64Pages=(128K+4K)Bytes;1Device=(2K+64)B×64Pages×4096Blocks=4224Mbits

其中:A0~11對頁內進行尋址,可以被理解為“列地址”。

A12~29對頁進行尋址,可以被理解為“行地址”。為了方便,“列地址”和“行地址”分為兩組傳輸,而不是將它們直接組合起來一個大組。因此每組在最后一個周期會有若干數據線無信息傳輸。沒有利用的數據線保持低電平。NAND型閃存所謂的“行地址”和“列地址”不是我們在DRAM、SRAM中所熟悉的定義,只是一種相對方便的表達方式而已。為了便于理解,我們可以將上面三維的NAND型閃存芯片架構圖在垂直方向做一個剖面,在這個剖面中套用二維的 “行”、“列”概念就比較直觀了。

-

閃存

+關注

關注

16文章

1782瀏覽量

114895 -

NAND

+關注

關注

16文章

1681瀏覽量

136119

發布評論請先 登錄

相關推薦

研究人員采用電子健康(EHR)系統來收集健康的社會決定因素的信息

解析NAND閃存和NOR閃存

閃存芯片分類及決定因素

研華工控機價格的決定因素,影響工控機價格的因素有哪些?

自感系數和互感系數的決定因素是什么?

14芯M16母頭使用壽命長短決定因素有哪些

NAND閃存特點及決定因素

NAND閃存特點及決定因素

評論