1.1 前言

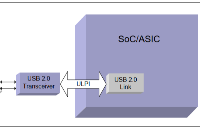

ULPI的同步模式是最主要的模式,內容也比較多,所以單獨一篇介紹。

1.2 ULPI命令字節

ULPI修改原始的UTMI數據流,使其能夠適應更多的數據類型。

傳輸期間PID字節中的冗余信息被ULPI傳輸命令(TX CMD)重載。

接收流中未使用的數據字節被接收命令(RX CMD)重載。

ULPI定義了由LINK發送的發送命令字節Transmit Command 和由PHY發送的接收命令字節 **Receive Command ** 。

以上的發送接收是以LINK的角度來看的。

1.2.1 發送命令字節(TX CMD)

LINK通過發送下表發送命令字節來啟動到PHY的傳輸。TX CMD字節由2位命令代碼和6位有效載荷組成。

2位命令代碼可以定義4種命令類型。

1.2.2 接收命令字節(RX CMD)

PHY發送下表的接收命令字節,以更新線路狀態、USB接收、斷開連接和OTG狀態信息給LINK。

RX CMD中的VbusValid指示來自內部VbusValid比較器或外部Vbus指示輸入。

Hostdisconnect 主機斷開連接狀態必須僅在主機模式下指示給LINK(DpPulldown和DmPullddown均設置為1b。

當處于設備模式時,必須忽略Hostdisconnect,并且不能屏蔽RxActive或RxError上的事件。

1.2.3 發送RX CMD的時機

RX CMD僅在同步模式下發送,并將兩種類型的信息傳輸到LINK。第一個是USB接收信息。第二個是中斷事件。所有信息被編碼到單個RX CMD字節中。

USB接收信息包括線路狀態LineState、RxActive和RxError。

在USB傳輸之后,PHY必須向LINK發送具有指示EOP的LineState的RX CMD。

對于高速,EOP就是LineState 的!squelch到squelch 。

對于全速和低速,EOP是LineState從SE0到J的轉換。

中斷事件包括Hostdisconnect、Vbus、IdGnd和其他源,如Carkit中斷。

只要檢測到這些事件,相應的USB中斷啟用上升沿USB Interrupt

Enable Rising 或USB中斷啟用下降沿寄存器USB Interrupt Enable Falling

配置了,就會向LINK發送RX CMD。

如圖說明了PHY如何向LINK發送RX CMD信息。第一個數據包顯示單個RX CMD。如果檢測到連續的更改,PHY將保持dir拉高并驅動連續的RX CMD,如第二個數據包所示。LINK必須能夠接受任何數量的連續的RX CMD。

RX CMD的優先級低于USB接收和傳輸數據,但優先級高于寄存器讀取和寫入命令。

如果ULPI總線忙于傳輸USB數據,則RX CMD將在PHY中排隊,并在ULPI總線可用時發送。

當發送到LINK時,排隊的RX CMD必須始終傳達當前RX CMD值,而不是以前或舊的值。

當在USB接收數據包期間nxt被拉低,PHY也必須向LINK發送RX CMD。

1.3 USB包

本節介紹如何通過ULPI總線傳輸和接收USB數據包。給出了PHY和LINK處理延遲的限制,以便可以滿足USB數據包間延遲。

1.3.1 NOPID數據包

如圖所示,為了發送不包含數據包標識符(PID)的USB數據,LINK發送NOPID類型的TX CMD字節。

PHY可以拉低nxt以限制來自LINK的數據。PHY在TX CMD的第一個時鐘周期中不能拉低nxt,并且必須在檢測到stp高時去拉低nxt。

由于該命令不包含PID數據,PHY必須等待下一個數據字節,然后才能開始在USB上傳輸。

當最后一個字節已經被PHY接收時,LINK拉高stp1個周期,并且如果沒有發生傳輸錯誤,則將數據驅動到00h空閑狀態。在第一個字節被PHY接收之前,鏈路不得拉高stp。

該命令必須用于啁啾chirp 和恢復resume 信號,對于這種信號,必須首先將功能控制寄存器中Function Control 的OpMode位設置為10b。對于啁啾和恢復信號,PHY不需要插入填充比特,因此必須保持nxt為高,直到它看到stp脈沖為止。

當LINK用NOPID數據包驅動ULPI總線時,PHY不應拉高dir,除非它想中止數據包。

所有USB數據包傳輸期間的RX CMD更改,必須用在USB傳輸結束時,ULPI總線可用時,發送的單個RX CMD更新來替換。即USB數據傳輸過程中狀態的變化不需要管了,最后發一個最終的狀態RX_CMD給LINK即可。RX CMD更新必須始終傳達當前RX CMD值,而不是以前或舊的值。

1.3.2 PID數據包

如圖所示,為了傳輸USB數據包,Link首先驅動一個TX CMD字節。命令字節類型設置為01b(傳輸),并將USB數據包標識符(PID)放置在數據上(3:0)。

PHY使用nxt控制數據接收,LINK在檢測到nxt為高之后提供下一個字節,這與UTMI的DataIn和TxReady相同。當最后一個字節已經被PHY接收時,LINK拉高stp 1個時鐘周期,并且如果沒有發生傳輸錯誤,則將數據驅動到00h空閑狀態。

在第一個字節被PHY接收之前,LINK不得拉高stp。

對于所有PID數據包,PHY必須自動準備SYNC域并附加EOP域。當TX CMD的PID字段為5h時,PHY必須識別出這是幀開始(SOF)包,并且自動附加長EOP。

在拉高stp之后,LINK不能發送另一個數據包,直到第一個數據包在USB上完成。

如果在給定定時之前接收到RX CMD表示有EOP,LINK可以開始傳輸下一個數據包。PHY必須始終發送指示EOP的RX CMD。

當LINK用PID數據包驅動ULPI總線時,PHY不應拉高dir,除非它想中止數據包。

所有USB數據包傳輸期間的RX CMD更改,必須用在USB傳輸結束時,ULPI總線可用時,發送的單個RX CMD更新來替換。即USB數據傳輸過程中狀態的變化不需要管了,最后發一個最終的狀態RX_CMD給LINK即可。RX CMD更新必須始終傳達當前RX CMD值,而不是以前或舊的值。

UTMI+規格書所述,PHY必須在傳輸期間內部阻塞USB接收路徑。

USB data transmit (PID)

PHY drives an RX CMD to indicate EOP (FS/LS LineState timing not to scale)

1.3.3 USB發送錯誤

如果LINK在全速或低速USB數據包傳輸過程中遇到緩沖區運行不足,則必須在數據包結束前在數據包中插入一個位填充錯誤。為了強制表示傳輸錯誤,LINK在數據包結束時,在它拉高stp的同一時鐘周期中,將FFh驅動到數據上。LINK只能驅動一個字節的FFh,PHY將通過在USB總線上發送至少8個連續的1來自動生成全速傳輸錯誤。在發送另一個數據包之前,LINK必須等待指示SE0-to-J轉換的RX CMD。在第一個字節被PHY接收之前,LINK不得拉高stp。該序列取代了UTMI在傳輸的最后一個字節期間將OpMode從00b更改為10b的方法。為了強制表示高速傳輸錯誤,LINK必須在數據包末尾傳輸值翻轉的CRC。

1.3.4 USB包接收

如圖所示,當PHY接收到USB數據時,它首先通過拉高dir獲得數據總線的所有權。

PHY在與UTMI的RxActive有效相同的周期中拉高dir。

如果dir先前為低,則PHY將拉高dir和nxt,LINK立即接收RXCMD知道這是USB接收數據包。

如果dir先前為高,PHY將拉低nxt并驅動RX CMD,RxEvent字段設置為01b(RxActive狀態),以便LINK接收RX CMD直到狀態。

PHY可以在下一個周期中開始驅動數據,或者輸出RX CMD,直到USB數據可用。

PHY拉高nxt并在總線上發送一個字節,將有效的USB數據包數據發送給LINK。

當nxt為低電平時,PHY驅動RX CMD字節。

USB包接收過程中的狀態變化即RX CMD變化,必須在nxt為低時,發出。

如果nxt在數據包接收期間從不為低,則必須在USB數據包接收結束時ULPI 總線可用時發送單個RX CMD更新來替換所有RX CMD改變,即最后只發送一次RX CMD狀態,中間的就不管了。RX CMD更新必須始終傳達當前RX CMD值,而不是以前或舊的值。

雖然數據流已從UTMI的DataOut修改,但nxt與RxValid相同。

當RX CMD字節顯示RxActive被設置為0b或dir被拉低(以先發生者為準)時,LINK認為數據包已完成。

1.3.5 USB接收錯誤

如果PHY檢測到USB數據包接收錯誤,它將忽略任何當前接收的數據字節,拉低nxt,并在RxEvent字段設置為11b的情況下驅動RX CMD字節(RxError狀態)。

當RxActive被設置為0時,PHY拉低dir。RxError狀態與UTMI的RxError信號相同。

當檢測到全速位填充錯誤時,所有PHY實現都必須設置RxError。

PHY可以選擇性地為未與字節邊界對齊的高速EOP、數據溢出、數據下溢或其他有效接收錯誤條件設置RxError。

PHY在EOP之前不對單個全速dribble bit 位設置RxError。

LINK必須忽略出現接收錯誤的數據包。

如圖顯示了在數據包中間檢測到比特填充錯誤時ULPI接口的行為。

如圖顯示了在最后一個CRC字節中發生位填充錯誤時的行為。

1.3.6 USB包時序

USB規范定義了數據包間時間。ULPI規范通過指定PHY和LINK可用的時鐘周期的預算,將這些定時關聯回ULPI接口。

PHY必須在給定的定時范圍內處理數據。

類似地,LINK必須在給定的決策時間內做出響應,或者如果在給定的時間范圍內沒有收到響應,則超時。以下詳細說明所有要求的ULPI數據包間定時,并源自USB規范和UTMI PHY處理和同步延遲(來自UTMI規范)。

1. USB數據包間延遲和數據包超時

全速數據包間延遲是從第一個數據包的SE0到J轉換到第二個數據包上的SYNC域開始測量的。

高速包間延遲是從總線在第一包結束時進入空閑狀態開始測量的,直到總線在第二個數據包開始時離開空閑狀態時計算。

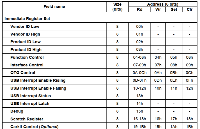

一個時鐘周期有8個HS位時間,一個FS位時間有5個時鐘周期,一個LS位時間有40個時鐘周期。如圖所示

USB規格指定的包間時間

位寬和時鐘關系

Transmit-Receive時間:在USB規范中定義為,最大連接的USB系統,包括通過6根USB電纜、5個外部集線器和下游主機或外圍設備的來回程時間。

2.PHY****管道延遲

使用ULPI接口的任何PHY必須符合表中給出的時序。

USB總線事件是相對于D+和D-線上的轉換來測量的。

ULPI接口定時是相對于檢測到轉換的時鐘邊緣來測量的(例如,PHY在時鐘de 邊緣檢測stp).

RX CMD Delay:與UTMI的線路狀態延遲2-3個時鐘相同,但由于RX CMD期間ULPI總線周轉turn around,最大值增加了1個額外的時鐘周期。

3.LINK決策時間

下表給出了為各種包序列分配給ULPI LINK的時間。當LINK傳輸第二個數據包時,它必須滿足數據包間的延遲。當LINK期望對傳輸的數據包做出響應時,它必須對數據包間延遲進行計時,以檢測超時。對于連續接收數據包,LINK必須能夠在給定的時間內接收它們。

Transmit-Transmit,Receive-Transmit:與UTMI的FS SIE決策時間7-19時鐘相同,但由于ULPI PHY在RX CMD期間需要總線周轉turn around,因此從最大值減去1個時鐘周期.

Transmit-Receive,UTMI規范說明高速傳輸到接收時間不正確,應忽略。

4.內部包時序圖

如圖說明了各種包序列的PHY管道延遲和LINK決策時間。

高速發送-發送包時序

高速接收-發送包時序

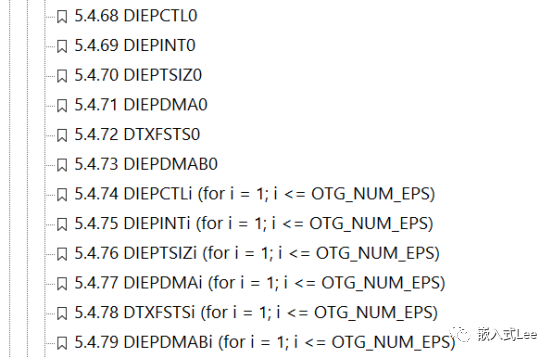

1.4寄存器操作

1.4.1 立即寄存器讀寫

寄存器寫

LINK發送寄存器寫入命令字節并等待nxt拉高。在nxt拉高之后的時鐘周期中,Link發送寫入寄存器的數據,并等待nxt再次拉高。當nxt第二次拉高時,Link在下一個時鐘周期中拉高stp以完成操作。PHY必須檢測stp拉高,然后才能接受另一個傳輸命令。如果PHY通過拉高dir中止RegWrite,則LINK必須在總線空閑時重試RegWrite。

寄存器讀

LINK發送寄存器讀取命令字節并等待nxt的拉高。在nxt拉高之后的時鐘周期中,PHY拉高dir以獲得對數據總線的控制。在dir拉高之后的時鐘周期中,PHY必須返回寄存器讀取數據。

當在寄存器讀取操作期間,即使是在寄存器內容返回的時鐘周期拉高dir,PHY也不拉高nxt。

這允許USB數據接收在任何時鐘周期內始終優先于寄存器讀取。如果PHY早于下圖中所示時刻拉高dir中止RegRead,則當總線空閑時,LINK必須重試RegRead

1.4.2 USB數據接收中止立即寄存器讀寫

寄存器讀取是ULPI不使用nxt來掐斷數據的唯一實例。nxt信號僅在USB接收期間被拉高,使得LINK能夠始終將USB數據接收與其他數據傳輸區分開來。

下顯示了在初始發送命令字節期間被USB接收中止的寄存器讀取或寫入。

下圖顯示了在寄存器讀取數據返回到LINK的同一時鐘周期內,USB接收中止了寄存器讀取。

在以上兩種情況下,PHY都拉高dir和nxt以指示RxActive。

寄存器讀取和寫入操作也會因PHY發送RX CMD而中止,除非是在寄存器讀取數據返回到LINK的時鐘周期內。

1.4.3 連續的寄存器讀寫和USB數據接收

下圖顯示了在寄存器讀取數據返回到LINK的同一周期中發生的USB數據接收。PHY必須首先返回寄存器讀取數據,而不是指示RxActive的RX CMD字節。PHY在下一個周期中指示RxActive,將USB接收數據與寄存器讀取連續放置

下圖顯示了在寄存器讀取完成后的時鐘中立即發生的USB數據接收。PHY將USB接收數據與寄存器讀取連續放置。

LINK必須能夠接受連續的數據包,其中dir不會在數據包之間拉低。

如下圖所示,如果dir在寄存器寫入操作結束時拉高stp的同一時鐘周期拉高,則PHY認為寄存器寫入已成功完成。PHY不會因為stp而拉低dir。

下圖顯示了在寄存器讀取數據返回到LINK后的時鐘周期中開始的USB數據接收。

注意,當dir在一個周期周期內拉低時,總線周轉turn around的兩個周期。

在所有情況下,PHY拉高dir和nxt以指示RxActive。

1.4.4 擴展寄存器讀寫

對立即寄存器地址2Fh的訪問表示對擴展寄存器集的訪問。在這種情況下,地址在下一個時鐘周期內可用。

寄存器寫

對于擴展寄存器寫入,如圖所示,Link發送一個地址設置為2Fh的寄存器寫入命令,并等待nxt拉高。在nxt拉高之后的時鐘周期中,Link發送擴展寄存器地址,并等待nxt再次拉高。

當 nxt 第二次拉高時,LINK發送寄存器寫入數據并等待 nxt 再次拉高。當nxt第三次拉高,LINK在接下來的時鐘周期拉高stp,以完成操作。如果PHY通過拉高dir中止RegWrite,則LINK必須在總線空閑時重試RegWrite。

寄存器讀

對于擴展寄存器讀取,如圖所示,Link發送一個地址設置為2Fh的寄存器讀取命令,并等待nxt拉高。在nxt拉高之后的周期中,Link發送擴展寄存器地址,并等待nxt再次拉高。當nxt第二次拉高時,PHY拉高dir以獲得對數據總線的控制。在dir拉高之后的周期中,PHY返回寄存器讀取數據。當在寄存器讀取操作期間拉高dir時,即使在返回寄存器讀取數據的時鐘周期期間,PHY也不拉高nxt。這允許USB接收在任何周期內優先于寄存器讀取。如果PHY在下圖所示之前通過拉高dir中止RegRead,則當總線空閑時,LINK必須重試RegRead

1.4.5 擴展寄存器讀寫被連續的USB數據接收中止

除了擴展地址字節周期外,擴展寄存器讀取與立即寄存器讀取相同。

有一個額外的情況,如圖所示,在擴展地址周期期間,USB接收中止了擴展寄存器讀取。

PHY發送RX CMD也會中止擴展寄存器讀取和寫入操作,但在寄存器讀取數據返回到LINK的周期期間除外。

1.5中止ULPI傳輸

1.5.1 LINK中止PHY

當LINK在ULPI總線上傳輸數據時,PHY可以通過拉高dir來中止LINK。ULPI沒有指定任何會導致這種情況發生的條件。

1.5.2 PHY中止LINK

當PHY在同步模式下拉高了dir時,LINK可以通過拉高stp來中止PHY,如圖所示。

在下一個周期中,PHY必須拉低dir,并保持拉低dir直到Link事務完成。如果LINK如圖所示執行寄存器寫入或USB傳輸,則PHY必須等待序列末尾的stp脈沖,然后才能重新拉高dir。如果LINK執行寄存器讀取,PHY必須返回寄存器讀取數據,如圖所示,并且如果需要進行USB接收數據或RX CMD,則允許繼續拉高dir。

LINK不能在拉高dir的同一周期中中止PHY,并且PHY必須在其首次拉高dir的相同周期中忽略stp。

如果LINK在與拉低dir相同的周期中拉高stp,則PHY必須仍然保證LINK事務。

當PHY中止時,LINK必須在周轉turn around周期后立即驅動TX CMD。如果LINK沒有立即驅動TX CMD,則允許PHY重新拉高dir,如圖所示。

所有ULPI PHY實現必須支持被拉高stp的LINK中止。雖然該功能可以在任何時候使用,但它主要用于LINK通過禁用PHY來關閉babbling端口。如果LINK在USB接收數據包期間拉高stp,則PHY不能保證當前包和下一包期間USB數據的有效性。

1.6 USB操作

以下部分描述了LINK和PHY必須如何在ULPI總線上進行通信,以執行特定的USB操作序列。

圖表是在時間軸上水平壓縮的,而不是按比例壓縮的。

1.6.1 高速檢測握手(Chirp)

高速檢測握手,或稱Chirp,如圖所示,注意,圖中的時間不是按比例排列的,也沒有顯示所有RX CMD更新。總線周轉周期turn around也沒有顯示,并且必須在dir的每次拉高和拉低后發生一個周期。

必須遵循以下事件順序

1.FS/LS檢測–如果D-為高,主機檢測外圍設備連接為低速,如果D+為高,則檢測為全速。如果主機檢測到低速外圍設備,則不遵循此協議的其余部分。

2.主機驅動-如果主機檢測到全速外圍設備,它會通過寫入功能控制寄存器并設置XcvrSelect=00b(HS)和TermSelect=0b來重置外圍設備,從而驅動總線上的SE0(D+和D-通過45歐接地).主機還設置OpMode=10b用于正確的Chirp發射和接收,接收Chirp會使LineState以不同的方式進行編碼,并考慮高速差分接收器輸出,以免出現錯誤的總線活動。SE0的起點標記為T0。設備PHY拉高dir,并使用RX CMD向LINK通知線路狀態改變。

3.設備響應-在檢測到SE0不少于2.5us后,如果設備具有高速功能,則設備LINK將XcvrSelect設置為00b(HS),將OpMode設置為10b(chirp),并立即發送一個TX CMD(NOPID),發送一個chirp K不少于1ms。并且chirp K必須在復位時間T0之后不超過7ms結束。如果設備處于低功率模式,它必須在5.6ms內喚醒其時鐘,留下200us用于LINK開始傳輸chirp K信號,留下1.2ms用于chirp信號完成(最壞情況下,時鐘慢10%)

4.主機響應–如果主機未檢測到設備chirp,則必須繼續發送SE0,直到重置結束。如果主機在總線離開chirp K狀態后檢測到設chirp K不少于2.5us、然后不多于100us,主機發送具有交替的chirp K和J序列的TX CMD(NOPID)。每個單獨的chirp K或J必須持續不少于40us且不超過60us。

5.HS空閑–設備必須檢測到最小的chirp K-J-K-J-K-J。每個單獨的chirp K和J必須被檢測至少2.5us。在看到該最小序列之后,設備LINK設置TermSelect=0b和OpMode=00b。設備現在處于高速模式,看到LineState的!squelch。當設備在LineState上看到squelch(10b)時,它知道主機已經完成了chirp,并等待高速USB通信開始。發送chirp序列后,主機將OpMode更改為00b,并開始發送USB數據包.

1.6.2 前導

USB將前導數據包定義為低速數據包的報頭,低速數據包必須在主機和集線器之間通過全速總線傳輸。要進入前導碼模式,LINK在功能控制寄存器中設置XcvrSelect=11b。當處于前導碼模式時,PHY的操作與全速模式相同,并以全速上升和下降時間發送所有數據。每當LINK以前導碼模式發送USB數據包時,PHY必須在以低速比特率發送LINK數據包之前以全速比特率自動發送前導碼報頭。PHY必須確保全速PRE-PID的最后一位和低速包SYNC的第一位之間的最小間隙為4個全速位時間。在發送PRE PID之后,PHY必須驅動J至少1 FS位時間,之后上拉電阻器可以在總線上保持J狀態。

在前導碼模式中,PHY還可以從全速總線接收低速包。

1.6.3 Usb掛起和恢復

掛起和恢復由HOST或者HUB啟動

1. 低速掛起和恢復

下圖說明了主機或集線器如何進入低速掛起狀態,然后啟動恢復信號以喚醒下游低速設備。圖計中時不是按比例進行的,也沒有顯示所有RX CMD線路狀態更新。總線周轉周期也沒有顯示,并且必須在dir的每次拉高和拉低后發生一個時鐘周期。以下描述了事件的過程。

1.LS通訊-最初,主機和設備通過USB總線發送低速流量(XcvrSelect設置為10b)。主機有其15k? 下拉已啟用(DpPulldown和DmPullddown設置為1b)和45? 終端已禁用(TermSelect設置為1b)。設備具有1.5k? 上拉連接到D-(TermSelect設置為1b)。

2.LS掛起–當設備在3ms內沒有看到總線活動時,它進入掛起狀態。設備的LINK通過設置SuspendM位將PHY置于低功率模式,從而使PHY僅汲取掛起電流。主機可能斷電,也可能未斷電。

3.恢復K–當主機想要喚醒設備時,它將OpMode設置為10b,并傳輸LS K至少20ms。設備的LINK看到線路狀態上的恢復K(01b),并拉高stp以喚醒PHY

4.EOP–當stp被拉高時,主機PHY自動附加一個LS EOP(2位LS SE0,后跟1位LS J)。主機PHY知道添加LS EOP,因為主機的DpPulldown和DmPulldown被設置為1b。LS EOP完成后,主機LINK將OpMode設置為00b以進行正常LS操作。設備的LINK看到LS EOP并恢復正常LS操作

2. 全速掛起和恢復

下圖說明了主機或集線器如何進入全速掛起,然后啟動恢復信號以喚醒下游全速設備。

圖中計時不是按比例進行的,也沒有顯示所有RX CMD線路狀態更新。總線周轉周期也沒有顯示,并且必須在dir的每次拉高和拉低后發生一個周期。以下描述了事件的過程。

1.FS通訊-最初,主機和設備通過USB總線進行全速數據傳輸(XcvrSelect設置為01b)。主機其15k? 下拉已啟用(DpPulldown和DmPullddown設置為1b)和45? 終端已禁用(TermSelect設置為1b)。設備的1.5k? 上拉連接到D+(TermSelect設置為1b)。

2.FS掛起–當設備在3ms內沒有看到總線活動時,它進入掛起狀態。設備的LINK通過設置SuspendM位將PHY置于低功率模式,從而使PHY僅汲取掛起電流。主機可能斷電,也可能未斷電。

3.Resume K–當主機想要喚醒設備時,它將OpMode設置為10b,并傳輸FSK至少20ms。設備的LINK看到線路狀態上的恢復K(10b),并拉高stp以喚醒PHY

4.EOP–當stp被拉高時,主機PHY自動附加一個LS EOP(2位LS SE0,后跟1位FS J)。主機PHY知道添加LS EOP,因為主機的DpPulldown和DmPulldown被設置為1b。LS EOP完成后,主機LINK將OpMode設置為00b以進行正常FS操作。設備的LINK看到LS EOP并恢復正常的FS操作。

3. 高速掛起和恢復

下圖說明了高速主機或集線器如何進入全速掛起狀態,然后啟動恢復信號以喚醒下游高速設備。圖中計時不是按比例進行的,也沒有顯示所有RX CMD線路狀態更新。總線周轉周期也沒有顯示,并且必須在dir的每次拉高和拉低后發生一個周期。以下描述了事件的過程。

1.HS通訊-最初,主機和外圍設備通過USB總線進行高速數據傳輸(XcvrSelect設置為00b)。主機的15k? 下拉電阻已啟用(DpPulldown和DmPullddown設置為1b)和45? 終端電阻已啟用(TermSelect設置為0b)。設備的45? 終端電阻已啟用(TermSelect設置為0b)。

2.FS掛起–當設備在3ms內沒有看到總線活動時,它進入掛起狀態。設備的LINK將PHY置于全速模式(XcvrSelect設置為01b),刪除45? 終止并啟用1.5k? D+上拉(TermSelect設置為1b)。然后,設備的LINK設置SuspendM將PHY置于低功率模式,從而使PHY僅汲取掛起電流。主機也更改為全速(XcvrSelect設置為01b),刪除45? 終端電阻(TermSelect設置為1b),然后可能斷電也可能不斷電

3.Resume K–當主機想要喚醒設備時,它將OpMode設置為10b,并傳輸FSK至少20ms。設備的LINK看到線路狀態上的恢復K(10b),并拉高stp以喚醒PHY。

4.HS通訊-主機LINK設置高速(XcvrSelect設置為00b),并啟用其45? 終端(TermSelect設置為0b)。設備的LINK在USB總線上看到SE0,并設置高速(XcvrSelect設置為00b),并啟用其45? 終端(TermSelect設置為0b)。主機的LINK將OpMode設置為00b以進行正常HS操作

1.6.4 遠程喚醒

設備啟動遠程喚醒(恢復)。當置于USB掛起狀態時,Link會記住它最初的操作速度。根據原始速度,LINK遵循以下詳細說明的協議之一。下圖中,計時不是按比例進行的,并且沒有顯示所有RX CMD線路狀態更新。總線周轉周期也沒有顯示,并且必須在dir的每次拉高和拉低后發生一個周期。

1. 低速遠程喚醒

A)主機和設備都以低功耗模式啟動。

B) 外設通過重新啟用其時鐘并設置其SuspendM位來開始遠程喚醒。

C) 設備開始驅動總線上的K以發出恢復信號。設備的LINK在傳輸時應假設線路狀態為K(01b)

D) 主機識別恢復,重新啟用其時鐘并設置其SuspendM位

E) 主機在檢測到遠程喚醒后1毫秒內接管恢復驅動程序。如果時鐘不能在1ms內重新啟動,PHY必須實現自動恢復功能。

F) 設備停止驅動恢復

G) 設備看到主機繼續驅動恢復。

H) 主機停止驅動恢復,PHY將LS EOP添加到低速恢復的末尾。設備將LS EOP識別為恢復的結束。T1為LS EOP間隔。

J) 主機和設備都通過將OpMode寫入正常來恢復正常操作。

2. 全速遠程喚醒

A)主機和設備都以低功耗模式啟動

B)外設通過重新啟用其時鐘并設置其SuspendM位來開始遠程喚醒。

C)設備開始驅動總線上的K以發出恢復信號。設備的LINK在發送時應假定線路狀態為K(10b)。

D)主機識別恢復,重新啟用其時鐘并設置其SuspendM位

E)主機在檢測到遠程喚醒后1毫秒內接管恢復驅動程序。如果時鐘不能在1ms內重新啟動,PHY必須實現自動恢復功能。

F)設備停止驅動恢復

G)設備看到主機繼續驅動恢復

H)主機停止驅動恢復,PHY將LS EOP添加到全速恢復的末尾。設備將LS EOP識別為恢復的結束。(T1是LS EOP間隔。)

I)主機和設備都通過寫入OpMode和XcvrSelect恢復到正常操作。

3. 高速遠程恢復

A)主機和設備都以低功耗模式啟動

B)設備通過重新啟用其時鐘并設置其SuspendM位(1)開始遠程喚醒

C)設備開始驅動總線上的K以發出恢復信號。設備的LINK在發送時應假定線路狀態為K(10b)。

D)主機識別恢復,重新啟用其時鐘并設置其SuspendM位(2)

E)主機在檢測到遠程喚醒后1毫秒內接管恢復驅動程序。如果時鐘不能在1ms內重新啟動,PHY必須實現自動恢復功能。

F)設備停止驅動恢復。

G)設備看到主機繼續驅動恢復

H)主機停止驅動恢復,總線返回高速空閑狀態。設備將高速空閑識別為恢復結束。(T1是LS EOP間隔。

I)主機和設備都通過寫入OpMode、XcvrSelect和TermSelect恢復到正常操作

4. 自動恢復

當USB主機檢測到來自下游設備或集線器的遠程喚醒信號(resume-K)時,主機必須在1ms內接管resume-K信號的驅動。

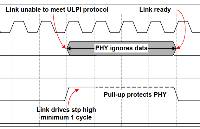

如果PHY處于主機模式,時鐘斷電,并且PHY檢測到遠程喚醒信號,則LINK必須喚醒時鐘并接管resume-K信號的驅動。如果時鐘無法在1ms內重新啟動,PHY必須提供自動恢復功能。如圖所示,PHY必須在內部驅動resume-K,直到時鐘恢復并接收到NOPID類型的TXCMD。

當時鐘恢復時,LINK通過發送NOPID類型的TXCMD來接管resume-K的驅動。當在自動恢復和由NOPID命令中的LINK驅動的恢復-K之間轉換時,PHY必須確保在恢復序列期間沒有故障。PHY還必須確保在退出低功率模式之前將SuspendM寄存器位自動設置為1b。

實現由PHY供應商確定,但是PHY供應商必須指定時鐘喚醒時間TSTART_HOST。

如果時鐘可以在1ms內重新啟動,則PHY不需要提供自動恢復功能。

接口控制寄存器中的自動恢復位控制自動恢復功能。

1.6.5 設備連接和斷開連接檢測

USB 中斷狀態寄存器中的主機斷開位指示設備何時連接或斷開,并且僅在 PHY 用作主機時才有效(DpPulldown 和 DmPulldown 均設置為 1b)。當用作主機PHY時,未屏蔽的HostDisconnect中的更改會導致PHY生成中斷事件通知。

當用作設備(DpPulldown設置為0b)時,PHY決不能生成指示主機斷開連接事件的中斷事件通知。

1.6.6無SYNC和EOP產生(Opmode11b)可選

此模式會影響數據包的傳輸方式,并且只能用于高速。

當OpMode設置為11b時,PHY在發送包時不會自動添加SYNC和EOP。PHY必須仍然對數據進行NRZI編碼并執行比特填充。當LINK想要傳輸USB數據包時,它必須發送NOPID類型的TX CMD。在NOPID命令之后,LINK在ULPI總線上發送一個4字節的SYNC模式(00h,00h,0h,80h),然后是PID、數據有效載荷,最后是一個1字節的EOP(FEh),如圖所示。不支持UTMI+的TxBitstuffEnable信號。PHY在啟動數據包時自動啟用位填充,在拉高STP時禁用位填充。LINK在其驅動EOP字節的同一周期中拉高stp。如果在stp被拉高時數據被設置為00h,則PHY將不會在USB總線上傳輸任何EOP。PHY必須檢測PID字節是否為A5h(SOF數據包),并在stp被拉高時自動發送長EOP。為了傳輸chirp和恢復信號,LINK必須將OpMode設置為10b。

當OpMode設置為11b時發送PID類型的TX CMD將導致未定義的行為。當OpMode為11b時接收RX CMD和USB接收數據包的操作與OpMode 00b相同

1.7Vbus電源控制(內部和外部)

LINK通過設置OTG控制寄存器中的DrvVbus位來打開Vbus。如果Vbus電源在PHY外部,則LINK在OTG控制寄存器中設置DrvVbus和可選的DrvVbusExternal位。VBUS控制設置如下表:

1.8 OTG操作

1.8.1 會話請求協議(SRP)

ULPI提供完整的SRP支持。LINK使用OTG控制寄存器中的ChrgVbus和DischrgVbus位來開始和結束會話。

1.8.2 主機協商協議(HNP)(可選)

ULPI未定義HNP支持。假設HNP是在LINK硬件和/或軟件中實現的。這并不妨礙PHY實現者向任何ULPI PHY添加HNP支持,只要其不干擾或違反本規范中定義的ULPI協議即可。

1.8.3 VBUS比較器閾值

雖然OTG規范提供了單獨的A設備和B設備可用的比較器,但具有0.8V至2.0V閾值(VA_SESS_VLD)的A設備比較器也可用于需要0.8V至4.0V閾值(VB_SESS_VLD)的B設備比較器,從而消除了對單獨的B設備比較器的需要。具有單獨的A設備和B設備比較器的實現可以映射到單個定義(VSESS_VLD)中。ULPI Vbus比較器閾值如表所示。

VA_VBUS_VLD閾值的目的是允許A設備確定其是否能夠在VBUS上輸出有效電壓。因此,ULPI未指定VA_VBUS_VLD閾值的上限,然而,該閾值的上限通常取決于A設備電源的特性。因此如果A器件電源通過將VBUS驅動到VA_VBUS_REF的基準來操作,并且當其目標設備列表上的B設備沒有汲取太多電流時,輸出電壓不會下降到x%以下,則閾值電壓將是:

4.4V

如果VBUS電源在PHY外部并且外部電源提供指示VBUS何時有效的信號,

建議該信號是可選引腳ExternalVbusIndicator上PHY的輸入,并且該引腳的狀態通過RX CMD字節中的VA_VBUS_VLD≤VBUS指示反映到LINK。OTG控制寄存器中的可選UseExternalVbusIndicator位在內部和外部VbusValid指示器之間進行選擇

為了支持行業標準的USB電源控制設備,PHY可以可選地支持接口控制寄存器中的兩個附加位,IndicatorPassThru和IndicatorComplement。這兩個位允許可選的ExternalVbusIndicator引腳與來自功率控制設備的功率有效信號或過電流故障輸出互操作,并適應來自功率控制裝置的有效高信號或有效低信號。當ExternalVbusIndicator引腳上提供電源故障信號時,PHY必須使用內部VbusValid比較器的輸出和外部電源故障信號的邏輯組合來生成VA_VBUS_VLD≤VBUS指示。

下表定義了UseExternalVbusIndicator、IndicatorPassThru和IndicatorComplement寄存器位的使用,以控制ExternalVbusIndicator輸入引腳和內部VbusValid比較器輸出的使用,從而在RX CMD字節中生成VA_VBUS_VLD≤VBUS指示。表中還列出了每種設置的典型應用。

RX CMD Vbus有效過電流條件

標準外圍設備不應使用Vbus Valid來開始操作。內部VbusValid可能不表示Vbus在第五集線器層上有效,允許低至4.375V。因此設備應使用Session valid。

下圖提供了內部和外部VbusValid源的邏輯組合的圖形表示,以及控制寄存器位如何影響RX CMD字節中的VA_VBUS_VLD≤VBUS指示。UseExternalVbusIndicator、IndicatorPassThru 和 IndicatorComplement 控制寄存器位是單獨可選的。PHY可以實現可選控制位的任何組合,然而,如果實現控制位,則它們必須提供表中定義的功能。如果未實現任何控制位,則PHY有責任定義可選ExternalVbusIndicator引腳如何影響RX CMD字節中VA_VBUS_VLD≤VBUS指示的狀態

RX CMD VA_VBUS_VLD≤VBUS指示源

根據應用程序的不同,LINK應啟用或禁用適當的VBUS中斷。下表中給出了典型應用的示例設置,RXCMD中的VbusValid指示來自內部VbusValid比較器或外部Vbus指示輸入。

典型應用所需的RX CMD中的VBus指示器

1.9總結

同步模式是ULPI必須支持的且主要的模式,內容比較多,對于軟件開發人員來說重點關注下總線時序,即數據是如何交互的,這樣必要的的時候可以使用邏輯分析儀進行抓包分析。另外重點關注下各個狀態是如何反應在ULPI的寄存器中的,可能底層分析時需要通過寄存器值分析當前狀態。

-

寄存器

+關注

關注

31文章

5437瀏覽量

124686 -

usb

+關注

關注

60文章

8204瀏覽量

273449 -

PHY

+關注

關注

2文章

325瀏覽量

52886 -

USB驅動

+關注

關注

1文章

138瀏覽量

20781 -

CMD5

+關注

關注

0文章

2瀏覽量

7213 -

DWC2

+關注

關注

0文章

35瀏覽量

256

發布評論請先 登錄

基于DWC2的USB驅動開發-0x02 DWC2 USB2.0 IP功能特征介紹

基于DWC2的USB驅動開發-0x09 ULPI接口協議其他工作模式介紹

基于DWC2的USB驅動開發-0x0B ULPI接口寄存器介紹

基于DWC2的USB驅動開發-0x0D PHY寄存器讀寫代碼編寫與測試

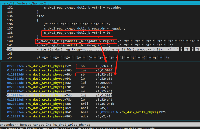

基于DWC2的USB驅動開發-0x0E 使用邏輯分析儀分析ULPI數據

基于DWC2的USB驅動開發-發送相關的寄存器DMA寄存器詳解

基于DWC2的USB驅動開發-0x0A ULPI接口同步模式介紹

基于DWC2的USB驅動開發-0x0A ULPI接口同步模式介紹

評論