前言

00

一般來說,面積是一個設計所消耗的目標器件的硬件資源數(shù)量或者ASIC芯片的面積。速度是指設計在芯片上穩(wěn)定運行時所能夠達到的最高頻率,這個頻率由設計的時序狀況決定。

面積和速度是對立統(tǒng)一的矛盾體 ,既想要設計面積最小,又想運行頻率最高,這是不現(xiàn)實的。科學的設計目標應該是在滿足設計時序要求(包含對設計最高頻率的要求)的前提下,占用最小的芯片面積,或者在所規(guī)定的面積下,使設計的時序余量更大,頻率更高。

一個設計如果時序余量較大,所能跑的頻率遠遠高于設計要求,能通過功能模塊復用減少整個設計所消耗的芯片面積,用速度的優(yōu)勢對換面積的節(jié)約。

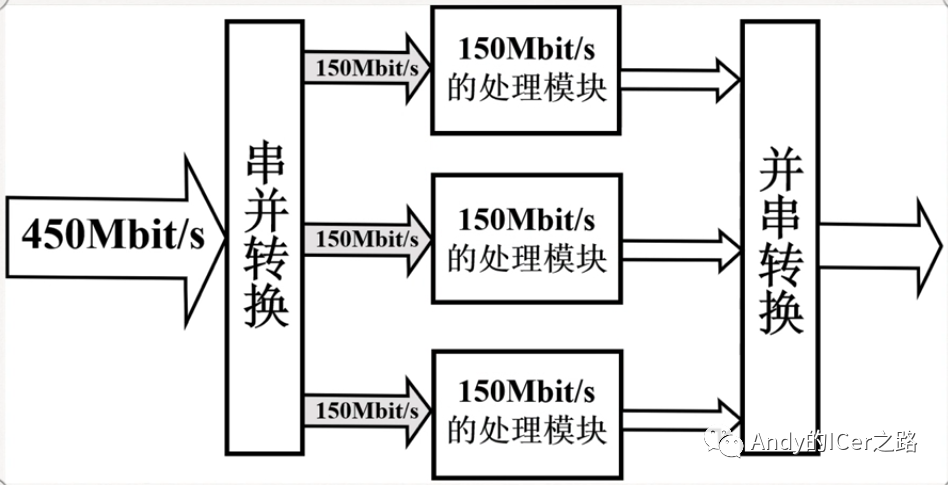

一個設計的時序要求很高,普通方法達不到設計頻率,可以通過將數(shù)據(jù)流串并轉換,并行復制多個操作模塊,對整個設計采取“乒乓操作”和“串并轉換”的思想進行處理,在芯片輸出模塊處再對數(shù)據(jù)進行“并串轉換”。

串并轉換 并串轉換

01

例如輸入數(shù)據(jù)流的速率是450Mbit/s,而在FPGA上設計的數(shù)據(jù)處理模塊的處理速度最大為150Mbit/s,在這種情況就應該利用“面積換速度”的思想,至少復制3個處理模塊。首先將輸入數(shù)據(jù)進行串并轉換,然后利用這3個模塊并行處理分配的數(shù)據(jù),最后將處理結果并串轉換以滿足數(shù)據(jù)速度的要求。

乒乓操作

02

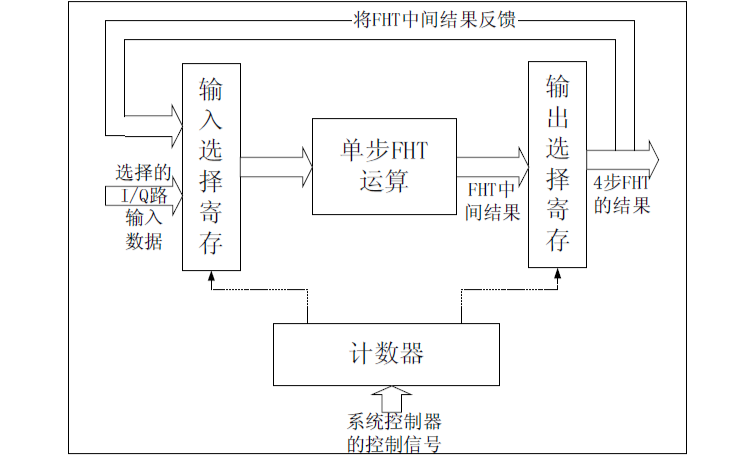

“乒乓操作”是一個常常應用于數(shù)據(jù)流控制的處理技巧,乒乓操作的結構如下圖所示:

數(shù)據(jù)緩沖模塊一般是常用的存儲單元,例如雙口RAM(DPRAM)、單口RAM(SPRAM)、FIFO等。

第一個緩沖周期:將輸入的數(shù)據(jù)流緩存到數(shù)據(jù)緩沖模塊1;

第二個緩沖周期:通過輸入數(shù)據(jù)選擇單元的切換,將輸入數(shù)據(jù)緩存到數(shù)據(jù)緩沖模塊2,同時數(shù)據(jù)緩沖模塊1通過輸出數(shù)據(jù)選擇單元輸出數(shù)據(jù);

第三個緩沖周期:通過輸入數(shù)據(jù)選擇單元的切換,將輸入數(shù)據(jù)緩存到數(shù)據(jù)緩沖模塊1,同時數(shù)據(jù)緩沖模塊2通過輸出數(shù)據(jù)選擇單元的切換輸出數(shù)據(jù);

如此循環(huán),直到輸入結束。

乒乓操作有兩個優(yōu)點:1、完成數(shù)據(jù)的無縫緩沖與處理;2、節(jié)約緩沖區(qū)空間。

完成數(shù)據(jù)的無縫緩沖與處理 :從上面乒乓操作的描述中可以看出,數(shù)據(jù)基本上是源源不斷地輸入輸出,只不過是中間的過程用了流水線式的設計來處理。根據(jù)這個優(yōu)點可以 用低速模塊處理高速數(shù)據(jù)流 ,其核心思想還是通過串并轉換實現(xiàn)面 積換速度 。

節(jié)約緩沖區(qū)空間 :例如需要將一幀的數(shù)據(jù)延時一個時隙后處理,最直接的辦法就是將這幀數(shù)據(jù)緩存起來,然后延時一個時隙進行處理,這時緩沖區(qū)的長度是一幀數(shù)據(jù)的長度。如果使用乒乓操作,用8個時隙完成一幀數(shù)據(jù)的傳輸,只需要兩個小的緩沖區(qū)即可,一個緩沖區(qū)是1/8幀數(shù)據(jù)的大小,其核心思想是 速度換面積 。

流水線設計

03

流水線設計大家應該都不陌生,福特發(fā)明了流水線提高了工人的效率,硬件電路也因為流水線而元氣滿滿。

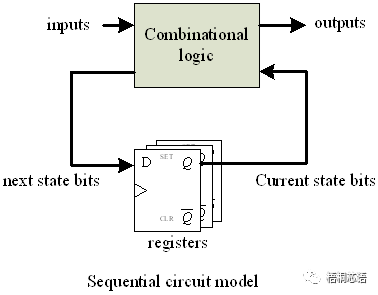

流水線特點: 通過插入寄存器,將長的串行邏輯鏈分成較小的部分;當系統(tǒng)運算是串行的時候,利用時鐘控制,使運算依照順序接續(xù)進行;在任何給定時刻,大部分電路都在工作。

流水線好處: 每一部分延時較小,可以使用更快的時鐘;大部分電路同時進行運算,可以提高數(shù)據(jù)通過量。

電路的最高頻率取決于最長組合邏輯鏈路的延遲值,所以減少最長組合邏輯鏈的延遲值,有利于提高電路速度。我們先來看一下不使用流水線的電路有什么問題:

可以從上面的圖看出,組合邏輯鏈會有很大部分的閑置電路,根據(jù)這個基礎我們來分析一下計算log(|a+b|)的硬件電路:

計算最小周期,即計算出電路最大頻率,對照電路的最小周期主要是加法器延時+求絕對值延時+求對數(shù)延時,因為一個部分電路在工作時,另一個部分的電路在閑置;

而流水線電路的最小周期主要是取(加法器延時,求絕對值延時,求對數(shù)延時)的最大值,可以看出流水線電路比原來的電路頻率大約快3倍左右,因為流水線是每一個部分的電路都在工作,效率大大提高。

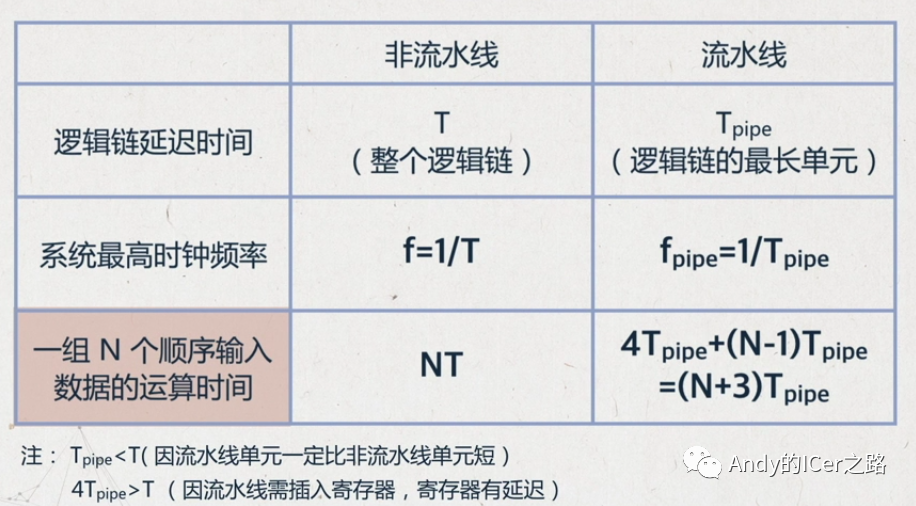

接下來我們來看一下流水線與非流水線電路的比較,以4級流水線為例。

以上是4級流水線的結構圖, 要注意的是流水線是按照延遲劃分的,不是按照功能劃分的 。具體流水線與非流水線電路的性能比較如下:

根據(jù)上面的性能比較表格,可以得知,具體使用流水線好還是非流水線好,還是要根據(jù)實際情況計算比較,一般來說流水線會較好。

另外, 流水線分割點及級數(shù)的確定要考慮的因素:

①單元延遲時間及時鐘頻率的大小決定了數(shù)據(jù)通過速率;

②過多的級數(shù)不一定能產生最快的結果;

③太多寄存器的插入會導致芯片面積增加,布線困難,時鐘偏差增加;

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26552 -

加法器

+關注

關注

6文章

183瀏覽量

30157 -

RTL

+關注

關注

1文章

385瀏覽量

59849 -

DPRAM

+關注

關注

0文章

2瀏覽量

10947 -

ASIC芯片

+關注

關注

2文章

92瀏覽量

23807

發(fā)布評論請先 登錄

相關推薦

速度面積互換設計原則簡析

FPGA設計思想,速度和面積互換原則不可忽視

Labview 之面向對象編程。 里面有個例子 和視頻教程地址

FPGA設計的指導原則

設計復用的RTL指導原則

FPGA設計的指導原則

FPGA設計的十五條原則詳細解析

FPGA的指導性原則詳細資料說明

PyTorch教程3.2之面向對象的設計實現(xiàn)

RTL設計指導原則之面積和速度互換

RTL設計指導原則之面積和速度互換

評論