任務就是一段封裝在“task-endtask”之間的程序。任務是通過調用來執行的,而且只有在調用時才執行,如果定義了任務,但是在整個過程中都沒有調用它,那么這個任務是不會執行的。調用某個任務時可能需要它處理某些數據并返回操作結果,所以任務應當有接收數據的輸入端和返回數據的輸出端。另外,任務可以彼此調用,而且任務內還可以調用函數。

**1.任務定義 **

任務定義的形式如下:

task task_id;

[declaration]

procedural_statement

endtask

其中,關鍵詞 task 和 endtask 將它們之間的內容標志成一個任務定義, task 標志著一個任務定義結構的開始;task_id 是任務名;可選項 declaration 是端口聲明語句和變量聲明語句,任務接收輸入值和返回輸出值就是通過此處聲明的端口進行的;procedural_statement是一段用來完成這個任務操作的過程語句,如果過程語句多于一條,應將其放在語句塊內;endtask 為任務定義結構體結束標志。下面給出一個任務定義的實例。

:定義一個任務。

task task_demo; //任務定義結構開頭,命名為 task_demo

input [7:0] x,y; //輸入端口說明

output [7:0] tmp; //輸出端口說明

if(x >y) //給出任務定義的描述語句

tmp = x;

else

tmp = y;

endtask

上述代碼

定義了一個名為“task_demo”的任務,求取兩個數的最大值。在定義任務時,有下列六點需要注意:

(1)在第一行“task”語句中不能列出端口名稱;

(2)任務的輸入、輸出端口和雙向端口數量不受限制,甚至可以沒有輸入、輸出以及雙向端口。

(3)在任務定義的描述語句中,可以使用出現不可綜合操作符合語句(使用最為頻繁的就是延遲控制語句) ,但這樣會造成該任務不可綜合。

(4)在任務中可以調用其他的任務或函數,也可以調用自身。

(5)在任務定義結構內不能出現 initial和 always過程塊。

(6)在任務定義中可以出現“disable 中止語句” ,將中斷正在執行的任務,但其是不可綜合的。當任務被中斷后,程序流程將返回到調用任務的地方繼續向下執行。

**2.任務調用 **

雖然任務中不能出現 initial 語句和 always 語句語句, 但任務調用語句可以在 initial 語句和 always 語句中使用,其語法形式如下:task_id[(端口1, 端口 2, ........, 端口 N)];

其中 task_id是要調用的任務名,端口 1、端口 2,…是參數列表。參數列表給出傳入任務的數據(進入任務的輸入端)和接收返回結果的變量(從任務的輸出端接收返回結果) 。任務調用語句中,參數列表的順序必須與任務定義中的端口聲明順序相同。任務調用語句是過程性語句,所以任務調用中接收返回數據的變量必須是寄存器類型。下面給出一個任務調用實例。

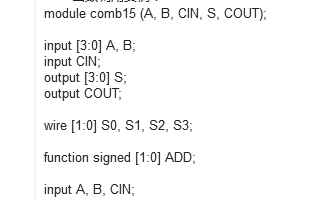

例:通過 Verilog HDL 的任務調用實現一個 4 bit全加器。

module EXAMPLE (A, B, CIN, S, COUT);

input [3:0] A, B;

input CIN;

output [3:0] S;

output COUT;

reg [3:0] S;

reg COUT;

reg [1:0] S0, S1, S2, S3;

task ADD;

input A, B, CIN;

output [1:0] C;

reg [1:0] C;

reg S, COUT;

begin

S = A ^ B ^ CIN;

COUT = (A&B) | (A&CIN) | (B&CIN);

C = {COUT, S};

end

endtask

always @(A or B or CIN) begin

ADD (A[0], B[0], CIN, S0);

ADD (A[1], B[1], S0[1], S1);

ADD (A[2], B[2], S1[1], S2);

ADD (A[3], B[3], S2[1], S3);

S = {S3[0], S2[0], S1[0], S0[0]};

COUT = S3[1];

end

endmodule

在調用任務時,需要注意以下幾點:

(1)任務調用語句只能出現在過程塊內;

(2)任務調用語句和一條普通的行為描述語句的處理方法一致;

(3)當被調用輸入、輸出或雙向端口時,任務調用語句必須包含端口名列表,且信號端口順序和類型必須和任務定義結構中的順序和類型一致。需要說明的是,任務的輸出端口必須和寄存器類型的數據變量對應。

(4)可綜合任務只能實現組合邏輯,也就是說調用可綜合任務的時間為“0” 。而在面向仿真的任務中可以帶有時序控制,如時延,因此面向仿真的任務的調用時間不為“0” 。

-

寄存器

+關注

關注

31文章

5336瀏覽量

120232 -

Verilog

+關注

關注

28文章

1351瀏覽量

110077 -

全加器

+關注

關注

10文章

62瀏覽量

28496 -

VerilogHDL

+關注

關注

2文章

39瀏覽量

19095 -

ADD

+關注

關注

1文章

20瀏覽量

9422

發布評論請先 登錄

相關推薦

verilog中關于task的調用問題

轉載---verilog中task和function的區別

verilog中generate語句的用法分享

簡談FPGA verilog中的task用法

簡談FPGA verilog中的function用法與例子

verilog中的task用法介紹

verilog中的task用法介紹

評論