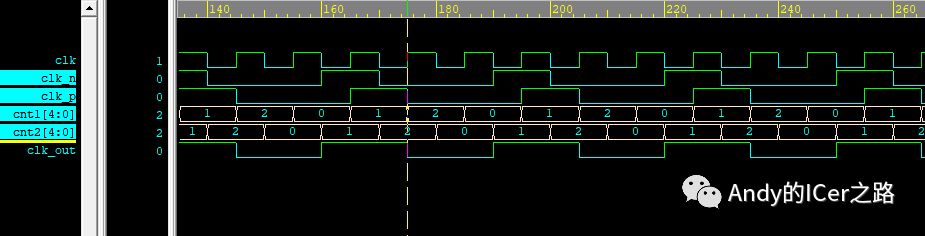

入門從簡單開始,先來個三分頻分析一下。三分頻其實就是把輸入時鐘的三個周期當作一個周期,具體波形如圖所示。(本文只針對于占空比為50%的分析)

此處還是用計數器的方式完成設計,但是與偶分頻有所區別。因為奇數分頻的頻率與輸入的時鐘頻率有相位差,因此需要增加一些信號完成設計。

clk_n是下降沿觸發的信號,clk_p是上升沿觸發的信號,通過計數并且因為不同的邊沿觸發而形成一定的相位差,并將兩個信號進行或門處理,最后輸出的就是奇數分頻結果了。

缺點分析:奇數分頻需要在兩個觸發器之后再加一個組合邏輯門,這個組合邏輯門不僅會增加時鐘的延時,而且在設計當中可能出現毛刺。

具體的占空比為50%的任意奇數分頻的代碼如下所示。

`timescale 1ns/1ps

module CLK_DIV #(parameter DIV_NUM=3)(

input clk,

input rst_n,

output clk_out

);

//all odd div

reg [4:0] cnt1,cnt2;

reg clk_p,clk_n;

always @(posedge clk,negedge rst_n)

if(!rst_n) begin

cnt1 <= 0;

clk_p <= 1'b0;

end

else begin

if(cnt1 == DIV_NUM-1) begin

cnt1 <= 0;

clk_p <= clk_p;

end

else begin

cnt1 <= cnt1 + 1'b1;

if(cnt1 == ((DIV_NUM-1)/2)-1 || cnt1 == DIV_NUM-2)

clk_p <= ~clk_p;

end

end

always @(negedge clk,negedge rst_n)

if(!rst_n) begin

cnt2 <= 0;

clk_n <= 1'b0;

end

else begin

if(cnt2 == DIV_NUM-1) begin

cnt2 <= 0;

clk_n <= clk_n;

end

else begin

cnt2 <= cnt2 + 1'b1;

if(cnt2 == ((DIV_NUM-1)/2)-1 || cnt2 == DIV_NUM-2)

clk_n <= ~clk_n;

end

end

assign clk_out = clk_p | clk_n;

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

分頻器

+關注

關注

43文章

447瀏覽量

49876 -

計數器

+關注

關注

32文章

2256瀏覽量

94478 -

觸發器

+關注

關注

14文章

2000瀏覽量

61132 -

輸入時鐘

+關注

關注

0文章

3瀏覽量

7255 -

CLK

+關注

關注

0文章

127瀏覽量

17158

發布評論請先 登錄

相關推薦

奇數分頻如何得到呢? 解讀奇數分頻和邏輯分析儀(ILA)的使用

前言: 偶數分頻容易得到:N倍偶數分頻,可以通過由待分頻的時鐘觸發計數器計數,當計數器從0計數到N/2-1時,輸出時鐘進行翻轉,并給計數

需要講解一個占空比50%的奇數分頻器的原理

本帖最后由 haozix521 于 2013-10-4 20:42 編輯

想做一個占空比50%的奇數分頻器,但是不是很了解這其中的意思。網上的資料都是這樣講的“對于實現占空比為50%的N倍奇數分頻

發表于 10-04 20:35

基于FPGA 的等占空比任意整數分頻器的設計

基于FPGA 的等占空比任意整數分頻器的設計

給出了一種基于FPGA 的等占空比任意整數分頻電路的設計方法。首先簡要介紹了FPGA 器件的特點和應用范圍, 接著討論了

發表于 02-22 14:22

?39次下載

分頻器的作用是什么 半整數分頻器原理圖分析

分頻器主要分為偶數分頻、奇數分頻、半整數分頻和小數分頻,如果在設計過程中采用參數化設計,就可以隨時改變參量以得到不同的

發表于 02-01 01:28

?1.7w次閱讀

偶數分頻、奇數分頻、半整數分頻和小數分頻詳解

初學 Verilog 時許多模塊都是通過計數與分頻完成設計,例如 PWM 脈寬調制、頻率計等。而分頻邏輯往往通過計數邏輯完成。本節主要對偶數分頻、奇數分頻、半整

介紹一下奇數分頻器的設計

介紹一下奇數分頻器的設計

評論