FIR設計過程中,不可避免使用到reg/wire的二維數組;在仿真的過程中,這些二維數組卻帶來不少麻煩,因為根據之前的內容,我們根本看不到這些二維數組的值。

而且,Verilog的端口定義是不支持二維數組這樣的定義,所以也無法把數組傳到頂層觀察。

而實現過程中,這些二維數組卻是流水線操作中的一部分,如果不知道它們的值,找BUG的過程肯定會十分艱難。

好在搜集各方資料后,經過一番實踐,總算是得出了如何觀察這些二維數組的值的方法。

首先,在testbench里面修改一下:

原來的版本:

initial begin$fsdbDumpfile("tb.fsdb");$fsdbDumpvars;end

第一個語句是產生一個fsdb文件,文件名為tb.fsdb,第二句是保存所有變量的波形。這里是為了產生fsdb文件,這樣Verdi才能看到根據fsdb文件顯示波形

修改后的版本:

initial begin$fsdbDumpfile("tb.fsdb");$fsdbDumpvars;$fsdbDumpMDA();end

第三行加了$fsdbDumpMDA(),這樣就可以Dump所有的Memeory值,不管什么信號都可以保存到Memory。

VCS編譯命令使用參數如下:

vcs \\*.v -LDFLAGS -Wl,--no-as-needed -timescale=1ns/1ps \\-fsdb -full64 -R +vc +v2k -sverilog -debug_all

仿真結束后,想使用Verdi查看二維數組的值,啟動Verdi。

命令行如下:

verdi -nologo \\+v2k -sverilog *.v -ssf tb.fsdb &

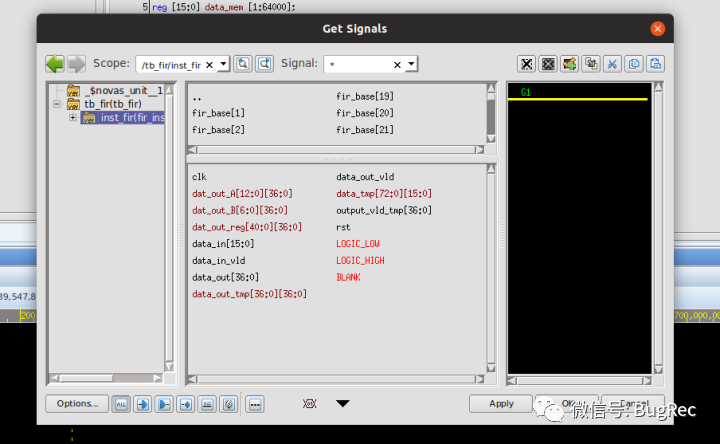

可以在Verdi添加信號時看到二維數組,如下圖:

Verdi查看可以看到二維數組

添加之后:

可以從圖中看到,很不直觀,不能直接看出有什么問題。

換個思路,按照下圖操作,選擇Memory里的Memory/MDA工具

按照序號操作

按照圖中1,2的順序,然后按照下圖選擇想查看的信號

點擊后選擇想觀察的信號

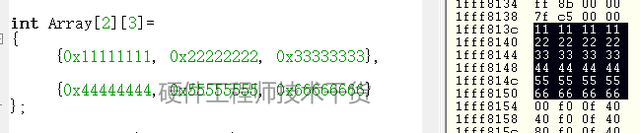

顯示信號結果

這里需要說明,查看二維數組內部存儲的值,可以使用框1里面的鍵,左右可以控制仿真時間,信號的值會跟隨仿真時間改變而改變。框1的時間跨度可以更改。

默認顯示的信號都是十六進制,如果想改變進制顯示,在2的位置右鍵可以改變進制顯示,并選擇有符號或無符號顯示。

地址數據也是十六進制顯示,可以在3的位置右鍵改變為十進制顯示。

有了這些工具的幫助,便可以從出錯的結果一步步往上查,追查BUG的效率提高不少。

總結,操作順序:

- Testbench加入$fsdbDumpMDA();

- 使用Verdi的Memory/MDA工具查看

-

FIR

+關注

關注

4文章

146瀏覽量

33172 -

Verilog

+關注

關注

28文章

1351瀏覽量

110091 -

VCS

+關注

關注

0文章

79瀏覽量

9605 -

MDA

+關注

關注

0文章

13瀏覽量

12223

發布評論請先 登錄

相關推薦

使用VCS觀察Verilog二維數組仿真值的方法

使用VCS觀察Verilog二維數組仿真值的方法

評論