可編程邏輯器件 (Programmable Loeie Device,PLD)是一種用戶編程實現某種邏輯功能的邏輯器件,主要由可編程的與陣列、或陣列、門陣列等組成,可通過編程來實現一定的邏輯功能。PLD 按集成度高低可分為簡單 PLD 和復雜PLD,簡單 PLD包括可編程只讀存儲器 ( Proerammable Read Onlv Memory,PROM)、可編程邏輯陣列 (Prograrmable Logie Array, PIA)器件、可編程陣列邏輯(Prograrmable Array Logie, PAL)器件、通用陣列邏輯 ( Generic ArrayLogic, CAL)器件;復雜 PLD 包括可擦可編程邏輯 (Erasable PLD, EPLD) 器件、復雜的可編程邏輯 (Complex Programmable Logie Device, CPLD)器件、場可編程門陣列 ( Field Programmable Gate Array, FPGA)器件等。隨著可編程器件的發展,可以將 CPU、DSP、ADC/DAC、存儲器等集成到一個可編程器件上,從而構成可編程系統芯片 (System On Programmable Chip, SoPC),如圖所示。

對PLD進行測試時,需要對其內部包含的資源進行結構分析,經過測試配置(TC)將其編程配置為具有特定功能的電路,再通過向量實施(TS) 過程對電路進行功能及參數測試。

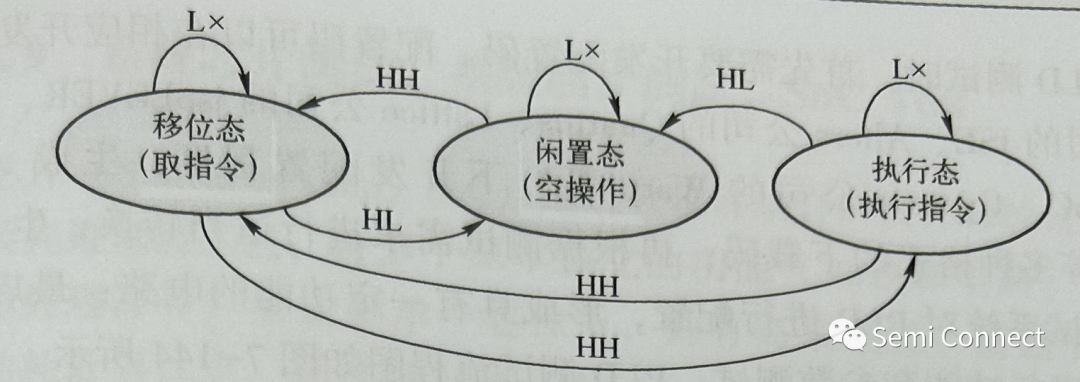

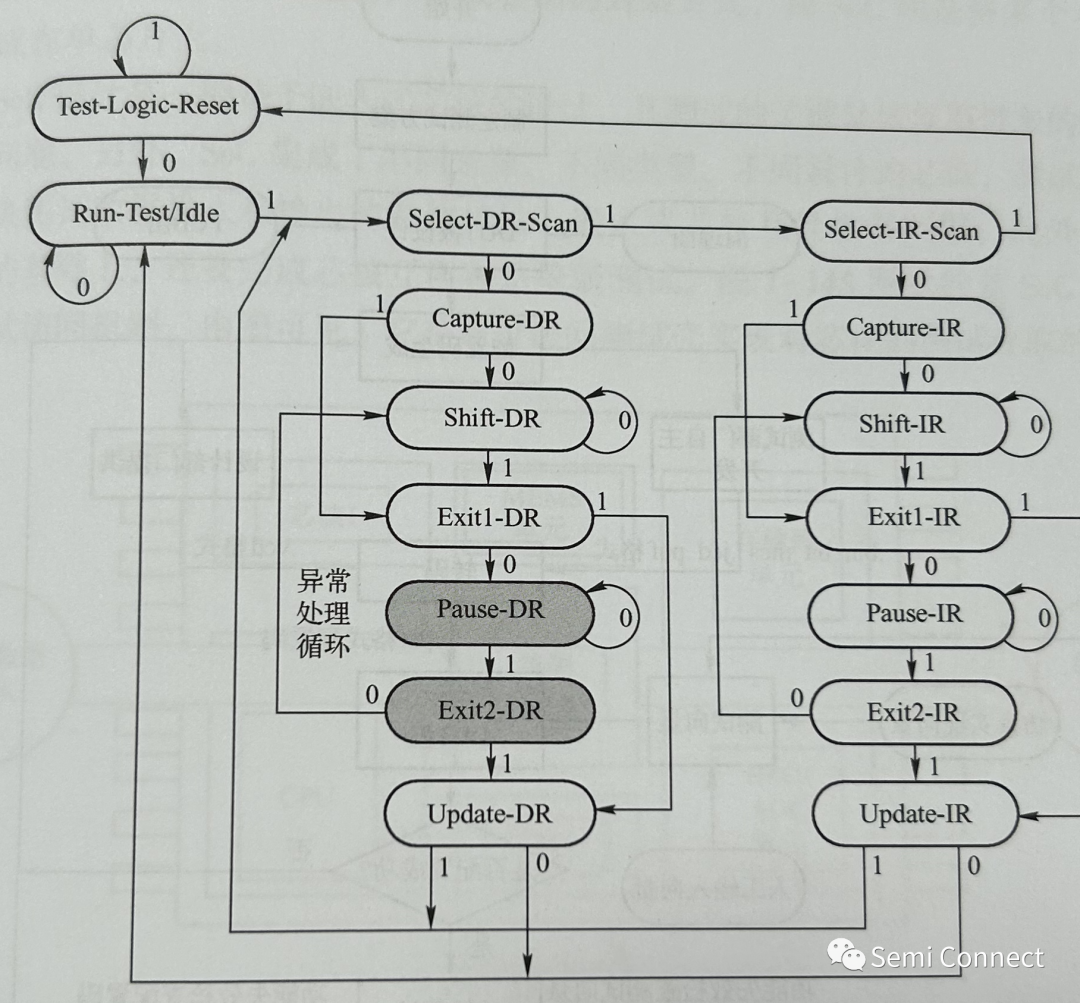

因可編程邏輯單元工藝不同,PLD 的編程工藝也不相同,主要有熔絲(Fuse)、反熔絲(Ani-fuse)、可擦可編程只讀存儲器 (Erasable ProgrammableRead Only Memory,EPROM)、電可擦可編程只讀存儲器 (Electrically ErasableProgrammable Read Only Memory, E2PROM)、靜態隨機存取存儲器 (StaticRandom Aecess Memory, SRAM)和閃速存儲器(Flash Memory)等。常用的測試編程方法有在系統可編程 (In-System Programmable, ISP)、聯合測試工作組(Joint Test Action Group, JTAG)協議編程、串行外設接口 ( Serial PeripheralInterface. SPI)編程、主模式/從模式編程等在系統可編程 (ISP)技術是萊迪思公司在 20 世紀 80 年代提出的一種先進的編程技術,廣泛用于 PROM、CPLD 和 FPGA 等的在系統編程。ISP 狀態機有兩種,即三狀態 ISP 狀態機和 IEEE1149.1 標準的 JTAG 狀態機(見圖)。

FPCA 的編程模式有多種,包括主串模式、從串模式、主并模式、從并模式、外設模式等,可以通過設置模式控制 腳的狀態水選擇不同的模式。為了提高測試效率,用自動測試系統對 FPGA 進行測試配置時,通常選擇主并模式或從并模式。

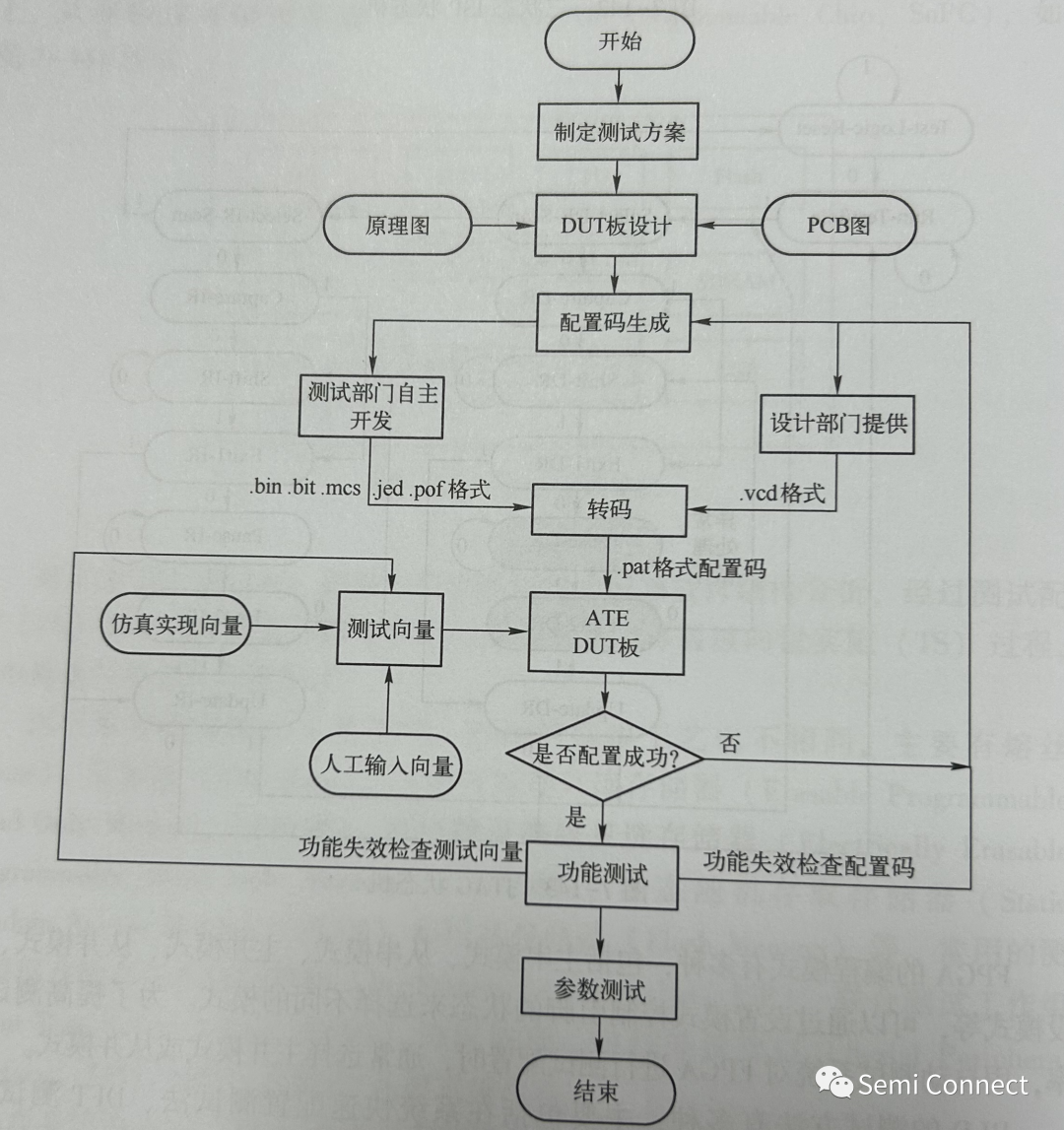

PLD 的測試方法有多種,主要包括在系統快速配置測試法、DFT測試法、內建自測試法(BIST)、掃描測試法(SCAN)、功能級聯測試法、基于黑盒的測試法,動態可重構測試法、定制軟件測試法、白適應測試法和基于板級應用的測試法等。隨著測試技術的發歷,一些新的測試方法不斷涌現,要達到較高的湖試覆蓋率,需果用多和方法相結合的方式進行測試,進行 PLD 測試時,首先需要開發配置碼。配置碼可以在相應開發環境(如XILINX公司的ISE、Altera 公司的 Quartus、Lattice 公司的 ispLEVER、Actel 公司的 Libero SoC、Cypress 公司的 Warp 等)下開發配置程序,生成.bit、.rbt、.bin、.svt 等多種格式的 下載碼;再根據測試需求進行適當轉換,生成配置碼;然后利用測試系統對 PLD 進行配置,形成具有一定功能的電路;最后加載測試碼,對電路進行功能和參數測試。PLD 測試流程圖如圖所示。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1643文章

21975瀏覽量

614404 -

存儲器

+關注

關注

38文章

7637瀏覽量

166480 -

PLD

+關注

關注

6文章

230瀏覽量

60018 -

可編程邏輯器件

+關注

關注

5文章

145瀏覽量

30574 -

邏輯單元

+關注

關注

0文章

25瀏覽量

5216

發布評論請先 登錄

可編程邏輯器件

PLD可編程邏輯器件

可編程邏輯器件基礎及應用實驗指導書

基于單片機的復雜可編程邏輯器件快速配置方法

什么是PLD(可編程邏輯器件)

可編程邏輯器件的分類有哪些

FPGA CPLD可編程邏輯器件的在系統配置方法

評論