在寫Verilog TestBench,為了更方便更抽象地對底層模塊內部的信號進行控制,經常會使用到跨模塊調用的方式,這個就叫做Cross Module Reference,縮寫為XMR。

本文就XMR的兩種方式做介紹,涉及部分基礎的Verilog 知識。

在TB當中,直接對DUT(Design under Test)的信號進行讀寫是很常見的操作。以一個簡單的計數器例子為例:

定義一個模塊名為a(取名比較隨意),功能是帶使能和異步復位的計數器,描述如下:

reg [31:0] cnt_r;

assign count = cnt_r;

always @ (posedge clk or posedge rst)

begin

if (rst)

cnt_r <= 'd0;

else if (en)

cnt_r <= count + 32'd1;

end

同時定義一個模塊名為b,功能是帶使能、置位和異步復位的計數器,描述如下:

reg [31:0] cnt_r;

assign count = cnt_r;

always @ (posedge clk or posedge rst)

begin

if (rst)

cnt_r <= 'd0;

else if (set)

cnt_r <= load_val;

else if (en)

cnt_r <= count + 32'd1;

end

同時創建一個wrapper將模塊b例化,并在TB中完成簡單的測試工作:

`include "macros.v"

module tb;

reg clk ;

reg rst ;

reg en ;

reg set ;

wire [31:0] a_cnt;

wire [31:0] b_cnt;

wire [31:0] b_cnt1;

initial begin

clk = 0;

rst = 1;

en = 0;

set = 0;

#100

rst = 0;

#100

en = 1;

#100

set = 1;

#20

set = 0;

#100

$finish;

end

always #10 clk = ~clk;

initial

forever begin

#20

$display("Time: %t A_CNT: %d B_CNT:%d", $time, `A_MODULE_INST.count, `B_MODULE_NAME.count);

end

a a_inst(

.clk(clk) ,

.rst(rst) ,

.en (en) ,

.count (a_cnt)

);

b_wrapper b_inst(

.clk(clk) ,

.rst(rst) ,

.set(set) ,

.load_val(32'd20),

.en(en) ,

.count (b_cnt)

);

`ifdef B_MULT

b_wrapper b_inst_1(

.clk(clk) ,

.rst(rst) ,

.set(set) ,

.load_val(32'd40),

.en(en) ,

.count (b_cnt1)

);

`endif

endmodule

a和b模塊的XMR調用通過宏定義控制,在tb的display函數中使用。宏定義內容如下:

`define A_MODULE_INST tb.a_inst

`define B_MODULE_NAME b

//`define B_MULT

所以整體的層次結構如下:

- tb

- a_inst (module a)

- b_inst (module b_wrapper)

- b_inst (module b)

- b_inst_1 (module b_wrapper if define B_MULT)

- b_inst (module b)

Hierarchical Reference

可以看到,a模塊的XMR方式是從頂層的tb開始,根據Instance name找到的例化的a模塊;這種根據結構和Instance Name跨模塊調用的方式叫做Hierarchical Reference, 這也是最常見的方式。

優缺點如下:

- 在Verilog的一個module中,Instance Name是唯一的,所以該種方式指向性很明確,支持精細化地控制同一個module例化的不同模塊信號。

- 但如果層次結構發生變化,或者Instance Name改變,會爆出Cross Module Reference Error。

Upwards Name Referencing

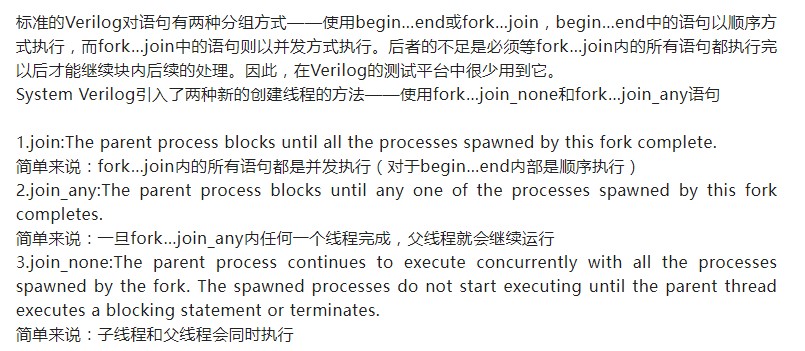

b模塊的XMR方式則是直接定義了b模塊的模塊名,然后verilog開始從定義的頂層開始查找,沒找到就進入下一層繼續尋找,直到找到唯一的那個模塊名匹配的為止:

它的優缺點與Hierarchical Reference正好相反:

- 不用擔心層次結構和Instance Name的變化會影響跨模塊調用。

- 使用該方式需要保證唯一性,不然也會爆出Cross Module Reference Error。

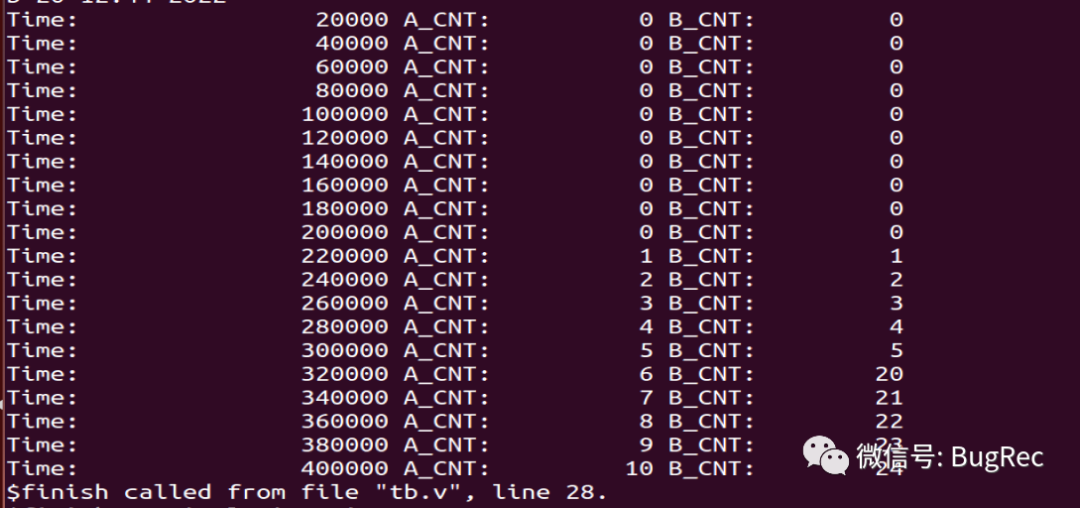

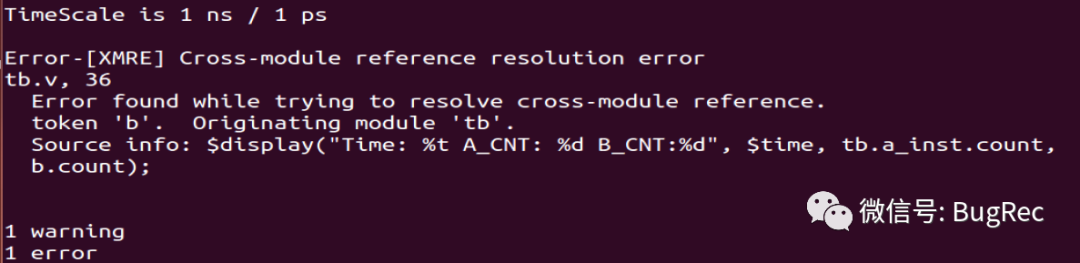

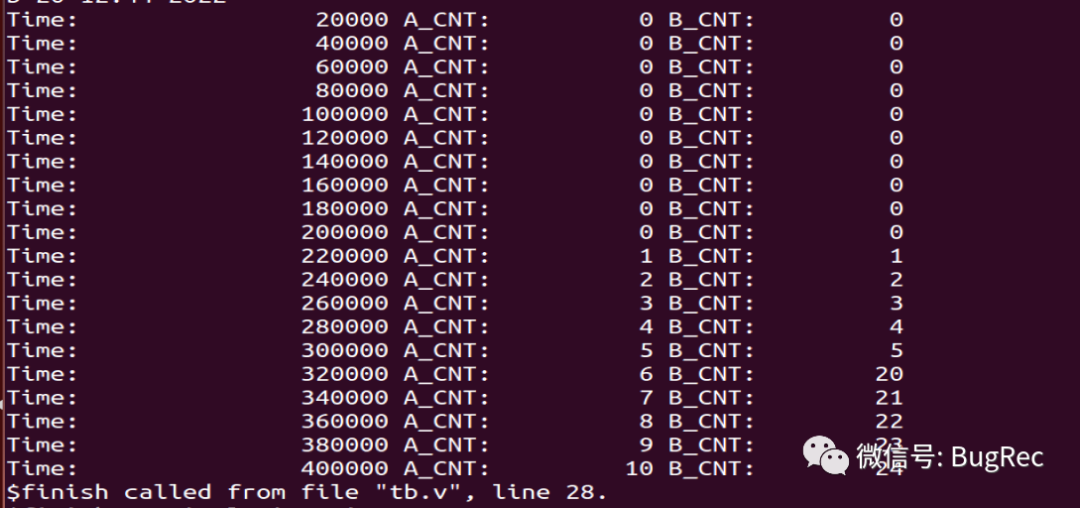

實驗結果如下:

在未定義B_MULT時:

定義B_MULT時:

總結:

Hierarchical Reference方式嚴謹但無靈活性,操作上可實現精細化控制,支持多模塊;Upwards Name Referencing方式靈活,但只支持單模塊,應用場景限制高。

所以,這也是Hierarchical Reference應用廣泛的原因吧,如果不是最近犯錯,我可能都不會注意到另一種XMR方式。

-

Verilog

+關注

關注

29文章

1367瀏覽量

112353 -

DUT

+關注

關注

0文章

191瀏覽量

12977

發布評論請先 登錄

請問C6748下的兩種DSP開發方式有什么區別

Net模塊中的通信傳輸協議有何優缺點

對兩種左右手傳輸線實現方式的研究現狀進行了深入分析以及優缺點對比

在MATLAB/simulink中建模時的兩種不同實現方式

MATLAB/simulink中兩種實現建模方式的優勢

兩種用于汽車PCB組件的連接器端子組件的優缺點

評論