大俠好,歡迎來到FPGA技術(shù)江湖。本系列將帶來FPGA的系統(tǒng)性學(xué)習(xí),從最基本的數(shù)字電路基礎(chǔ)開始,最詳細(xì)操作步驟,最直白的言語(yǔ)描述,手把手的“傻瓜式”講解,讓電子、信息、通信類專業(yè)學(xué)生、初入職場(chǎng)小白及打算進(jìn)階提升的職業(yè)開發(fā)者都可以有系統(tǒng)性學(xué)習(xí)的機(jī)會(huì)。

系統(tǒng)性的掌握技術(shù)開發(fā)以及相關(guān)要求,對(duì)個(gè)人就業(yè)以及職業(yè)發(fā)展都有著潛在的幫助,希望對(duì)大家有所幫助。后續(xù)會(huì)陸續(xù)更新 Xilinx 的 Vivado、ISE 及相關(guān)操作軟件的開發(fā)的相關(guān)內(nèi)容,學(xué)習(xí)FPGA設(shè)計(jì)方法及設(shè)計(jì)思想的同時(shí),實(shí)操結(jié)合各類操作軟件,會(huì)讓你在技術(shù)學(xué)習(xí)道路上無比的順暢,告別技術(shù)學(xué)習(xí)小BUG卡破腦殼,告別目前忽悠性的培訓(xùn)誘導(dǎo),真正的去學(xué)習(xí)去實(shí)戰(zhàn)應(yīng)用,這種快樂試試你就會(huì)懂的。話不多說,上貨。

多路選擇器設(shè)計(jì)

多路選擇器是數(shù)據(jù)選擇器的別稱。在多路數(shù)據(jù)傳送過程中,能夠根據(jù)需要將其中任意一路選出來的電路,叫做數(shù)據(jù)選擇器,也稱多路選擇器或多路開關(guān)。

二選一多路選擇器

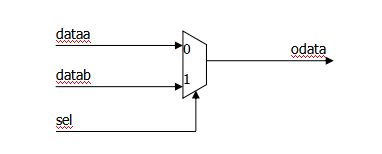

二選一多路選擇器的數(shù)據(jù)輸入有兩個(gè),分別為dataa和datab。為了能夠確定選擇那一路數(shù)據(jù)能夠通過,還需要一個(gè)選擇端(sel)。因?yàn)檩斎胫挥袃陕窋?shù)據(jù),選擇端只要能夠表現(xiàn)出兩種狀態(tài)即可,因而選擇端位寬為1即可。

假設(shè)dataa和datab都是位寬為1的數(shù)據(jù),當(dāng)sel為0時(shí),選擇dataa通過;當(dāng)sel為1時(shí),選擇datab通過;odata表示通過后的數(shù)據(jù)。

圖1 :二選一多路選擇器模型

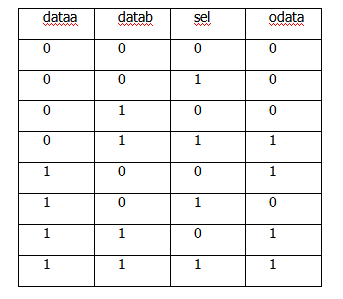

根據(jù)上述功能,列出真值表。

圖2 :二選一多路選擇器真值表

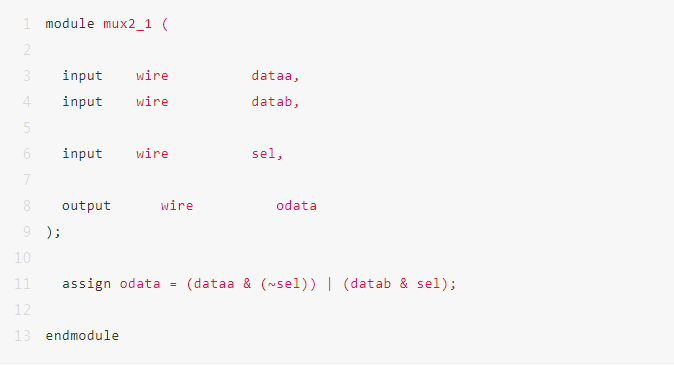

根據(jù)真值表,化簡(jiǎn)得出布爾表達(dá)式:

odata = (dataa &(~sel)) | (datab & sel);

在verilog中,算術(shù)運(yùn)算中,“&”表示算術(shù)(按位)與,“|”表示算術(shù)(按位)或,“~”表示算術(shù)(按位)取反。

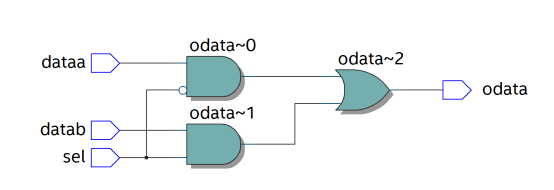

在數(shù)字電路基礎(chǔ)中,根據(jù)表達(dá)式,就可以得到電路圖。

現(xiàn)在我們要在FPGA中實(shí)現(xiàn),二選一多路選擇命名為“mux2_1”,不要命名為mux21,mux21是quartus中默認(rèn)器件庫(kù)中的名字,命名相同會(huì)出現(xiàn)錯(cuò)誤。

建立工程后,輸入如下設(shè)計(jì)代碼:(mux2_1代碼)

圖4 :mux2_1的RTL視圖

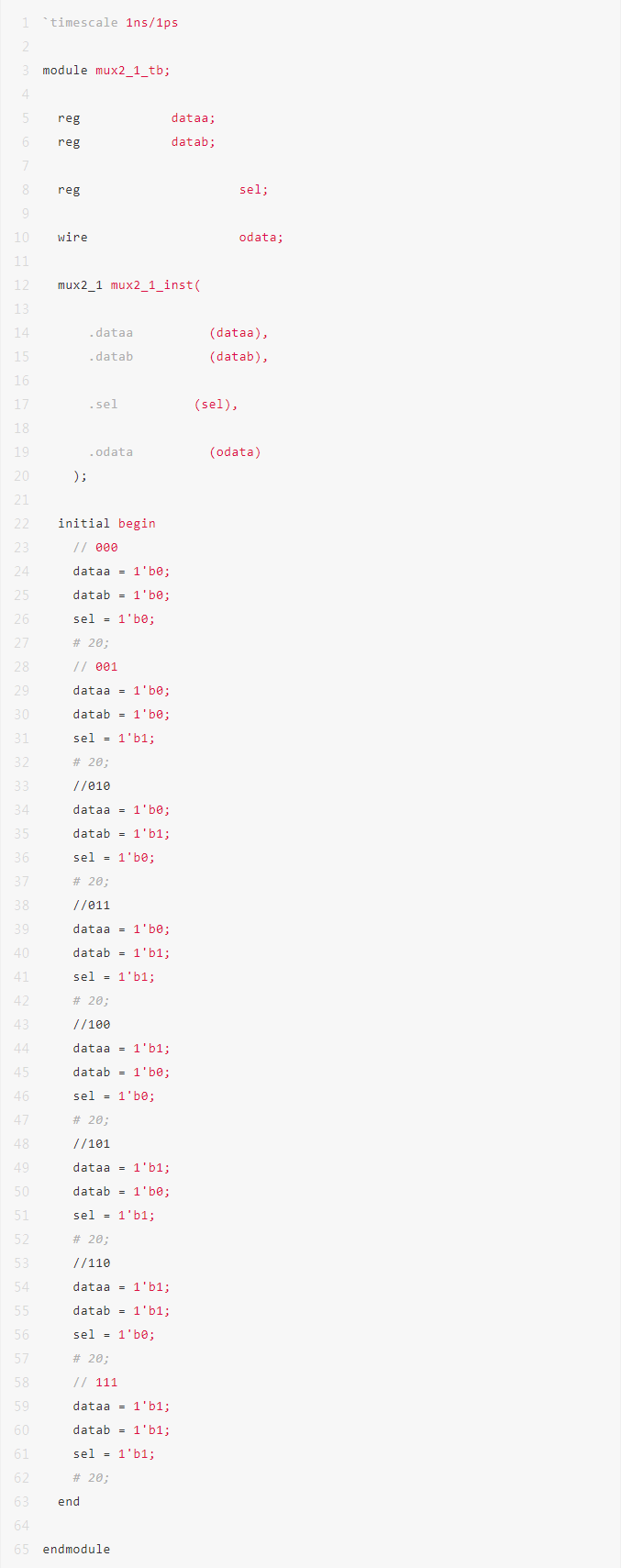

設(shè)計(jì)完成后,輸入如下testbench代碼:(mux2_1_tb代碼)

在verilog中,“//”表示本行被注釋,綜合器綜合時(shí),自動(dòng)略過。

在testbench中,連接線的名字可以隨意定義,建議和端口相同。

設(shè)置好testbench后,運(yùn)行RTL 仿真。

圖6 :RTL仿真波形

對(duì)比波形和真值表,設(shè)計(jì)正確。

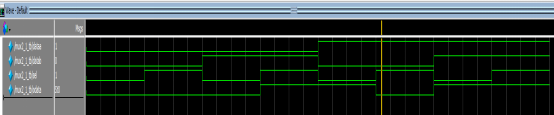

四選一多路選擇器

四選一多路選擇器的數(shù)據(jù)輸入有四個(gè),分別為dataa、datab、datac和datad。為了能夠確定選擇那一路數(shù)據(jù)能夠通過,還需要一個(gè)選擇端(sel)。因?yàn)檩斎胨穆窋?shù)據(jù),選擇端要求能夠表現(xiàn)出四種狀態(tài),因而選擇端位寬為2。

假設(shè)dataa、 datab、datac和datad都是位寬為8的數(shù)據(jù),當(dāng)sel為00時(shí),選擇dataa通過;當(dāng)sel為01時(shí),選擇datab通過;當(dāng)sel為10時(shí),選擇datac通過;當(dāng)sel為11時(shí),選擇datad通過;odata表示通過后的數(shù)據(jù)。

圖7 :四選一多路選擇器模型

根據(jù)組合邏輯設(shè)計(jì)規(guī)則,我們將所有的情況全部列出,得出真值表,進(jìn)而得到布爾表達(dá)式。但是現(xiàn)在輸入的組合排列太多了(2的34次冪),不能夠直接得出真值表。

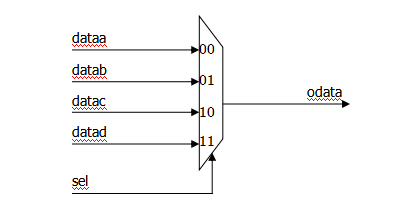

此時(shí)的設(shè)計(jì)有兩種方法。

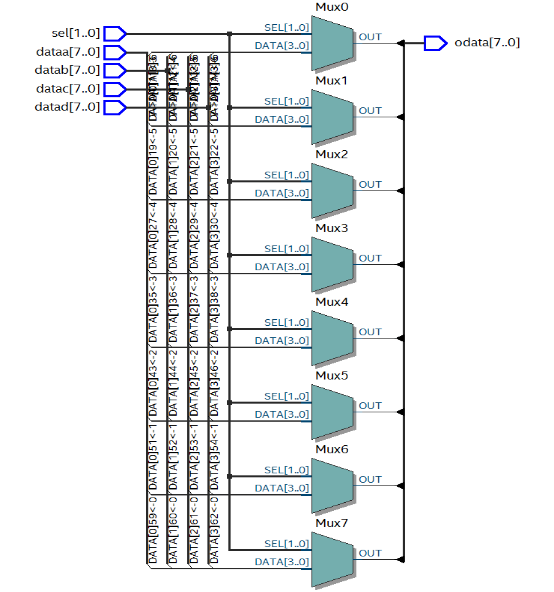

第一種方法,根據(jù)功能拆分邏輯。將輸入為8的四選一多路選擇器,拆分為8個(gè)位寬為1的四選一多路選擇器,首先列出位寬為1真值表,得出位寬為1的四選一多路選擇器。然后并接八個(gè)即可。

圖8 :8個(gè)位寬1多路選擇器構(gòu)成位寬8的多路選擇器

這種設(shè)計(jì)方法,不在提供設(shè)計(jì)源碼,讀者可以自行討論設(shè)計(jì)。

第二種方法,根據(jù)verilog的設(shè)計(jì)規(guī)則,可以直接描述邏輯功能,而不用描述門電路。這種設(shè)計(jì)規(guī)則有利于將設(shè)計(jì)做的比較大。

位寬為8的四選一多路選擇器命名為“mux4_1”。

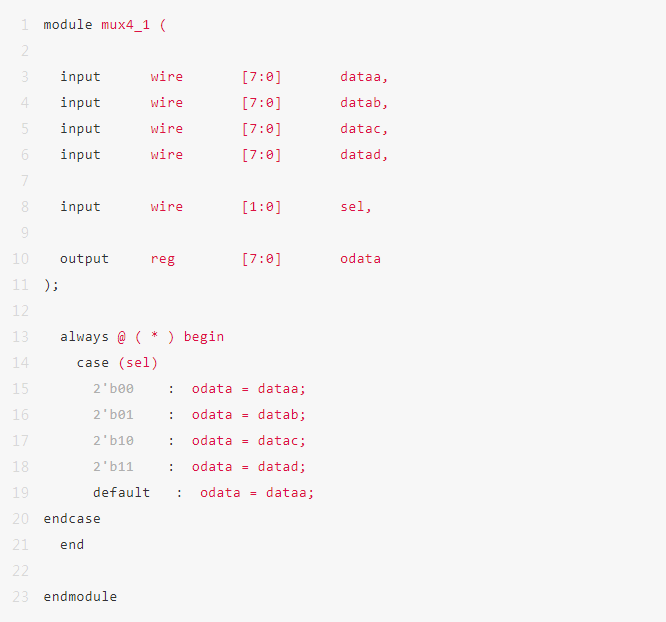

建立工程后,輸入設(shè)計(jì)代碼如下:(mux4_1代碼)

always 語(yǔ)句用來表示組合邏輯時(shí),即可以采用門電路的描述方法,也可以采用功能性的描述語(yǔ)句。

“always @()”中()是信號(hào)敏感列表。中間可以寫入本模塊的所有的敏感信號(hào),“*”可以表示所有的敏感信號(hào)。建議利用always語(yǔ)句描述組合邏輯時(shí),用“*”表示所有信號(hào)。用“*”時(shí),“()”可以省略。即:always@(*) 等效 always@*。

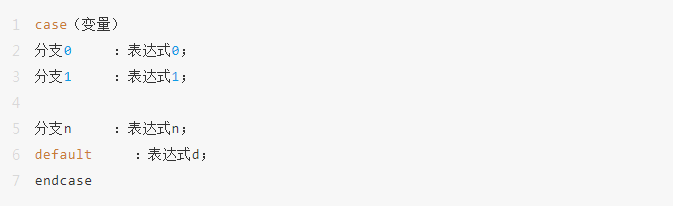

在case語(yǔ)句中,首先會(huì)判斷變量和那個(gè)分支相同,并且執(zhí)行對(duì)應(yīng)的表達(dá)式。當(dāng)和所有的分支都不相同時(shí),執(zhí)行default后的表達(dá)式。

verilog規(guī)定,在always語(yǔ)句中被賦值的變量,應(yīng)該定義為“reg”類型。

圖11 :mux4_1的RTL視圖

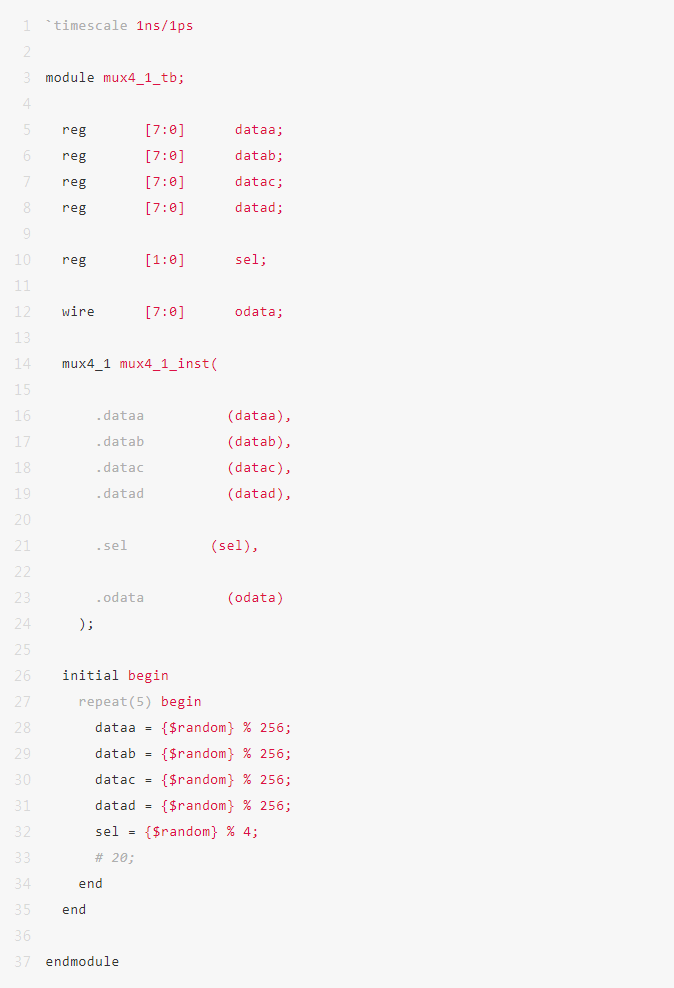

設(shè)計(jì)完成后,輸入testbench代碼。mux4_1_tb 代碼如下:

由于本次輸入的的組合太多,不能全覆蓋測(cè)試。故采用隨機(jī)數(shù)來進(jìn)行測(cè)試。

$random是一個(gè)系統(tǒng)函數(shù),調(diào)用時(shí),可以返回一個(gè)隨機(jī)值。注意:這個(gè)系統(tǒng)函數(shù)只能出現(xiàn)testbench中,在設(shè)計(jì)中出現(xiàn)是不可綜合的。

“$random函數(shù)調(diào)用時(shí)返回一個(gè)32位的隨機(jī)數(shù),它是一個(gè)帶符號(hào)的整形數(shù)...”。例:

reg[23:0] rand;

rand=$random % 60; //產(chǎn)生一個(gè)在 -59—59范圍的隨機(jī)數(shù)

產(chǎn)生0~59之間的隨機(jī)數(shù),例:

reg[23:0] rand;

rand={$random} % 60; //通過{}產(chǎn)生0—59范圍的隨機(jī)數(shù)

產(chǎn)生在min, max之間隨機(jī)數(shù),例:

reg[23:0] rand;

rand = min+{$random}%(max-min+1);

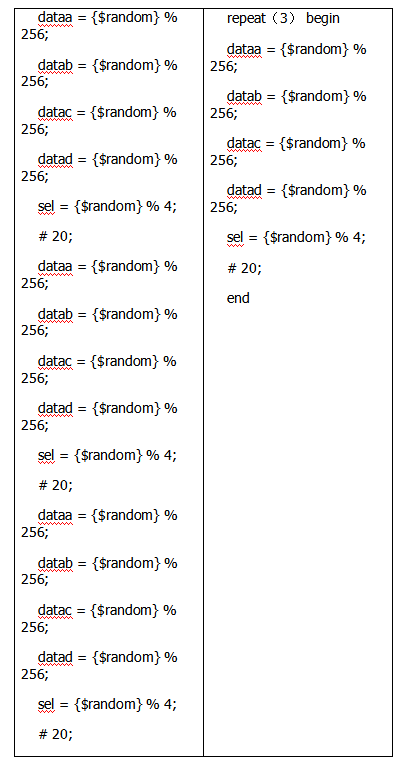

在testbench中,需要按照一定順序給輸入線賦值。在mux4_1_tb中,我們可以通過延遲賦值,然后再次延遲賦值,來完成賦值。因?yàn)橘x值時(shí)采用隨機(jī)數(shù),所以每次編寫的語(yǔ)句是相同的。verilog中提供了repeat語(yǔ)句,用來減少人工輸入。

圖13 :兩種等效的賦值方式

輸入testbench后,進(jìn)行綜合分析。

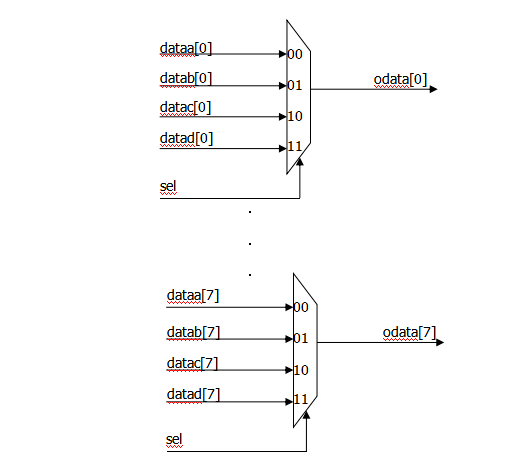

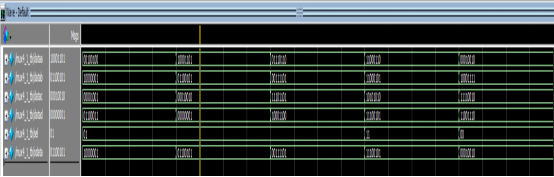

設(shè)置testbench,運(yùn)行RTL仿真。

圖14:RTL仿真圖

經(jīng)過分析,符合四選一多路選擇器的設(shè)計(jì)。

更多熱點(diǎn)文章閱讀

-

電子技術(shù)

+關(guān)注

關(guān)注

18文章

890瀏覽量

55979 -

電子發(fā)燒友論壇

+關(guān)注

關(guān)注

4文章

197瀏覽量

1085

原文標(biāo)題:【教程分享】零基礎(chǔ)學(xué)習(xí):基于FPGA的多路選擇器設(shè)計(jì)(附代碼)

文章出處:【微信號(hào):gh_9b9470648b3c,微信公眾號(hào):電子發(fā)燒友論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

零基礎(chǔ)嵌入式開發(fā)學(xué)習(xí)路線

為MCU擴(kuò)展選擇正確的多路復(fù)用器

請(qǐng)問模擬開關(guān)跟多路復(fù)用器有什么區(qū)別?

數(shù)據(jù)選擇器是時(shí)序邏輯電路嗎

數(shù)據(jù)選擇器是組合邏輯電路嗎

基于FPGA的“俄羅斯方塊”設(shè)計(jì)(附代碼)

FPGA基礎(chǔ)知識(shí)學(xué)習(xí)

邏輯器件多路轉(zhuǎn)換器是什么?

具有N通道功率MOSFET選擇器的1-4節(jié)鋰離子電池SMBus充電控制器bq24735數(shù)據(jù)表

FPGA零基礎(chǔ)學(xué)習(xí)系列精選:半導(dǎo)體存儲(chǔ)器和可編程邏輯器件簡(jiǎn)介

fpga學(xué)習(xí)需要具備哪些課程

DA1453x閃存選擇器指南應(yīng)用說明

從入門到放棄……為什么你會(huì)覺得FPGA難學(xué)?如何學(xué)習(xí)FPGA?

【教程分享】零基礎(chǔ)學(xué)習(xí):基于FPGA的多路選擇器設(shè)計(jì)(附代碼)

【教程分享】零基礎(chǔ)學(xué)習(xí):基于FPGA的多路選擇器設(shè)計(jì)(附代碼)

評(píng)論