大俠好,歡迎來到FPGA技術江湖。本系列將帶來FPGA的系統性學習,從最基本的數字電路基礎開始,最詳細操作步驟,最直白的言語描述,手把手的“傻瓜式”講解,讓電子、信息、通信類專業學生、初入職場小白及打算進階提升的職業開發者都可以有系統性學習的機會。

系統性的掌握技術開發以及相關要求,對個人就業以及職業發展都有著潛在的幫助,希望對大家有所幫助。本次帶來Vivado系列,ROM使用教程。話不多說,上貨。

ROM使用教程

作者:李西銳校對:陸輝

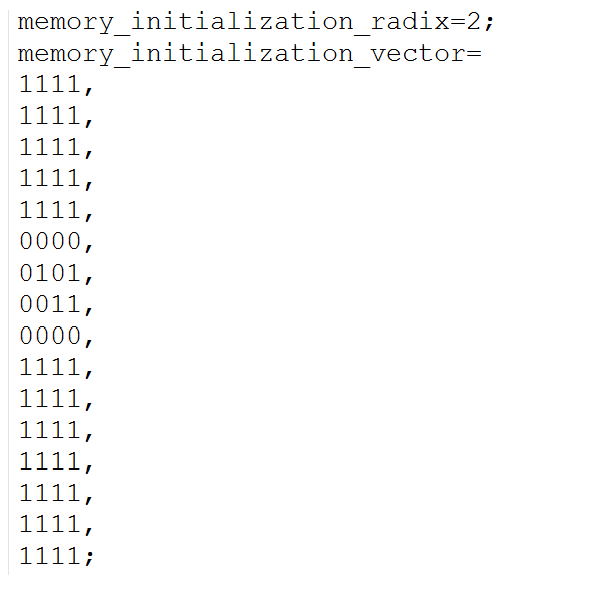

ROM的英文全稱為Read-Only Memory,即只讀存儲器。可以從任意地址上讀取數據,但是不能寫入。那么我們ROM中的數據,就需要我們提前存放進去,在IP核中,我們可以通過.coe文件進行數據存放,文件格式我們可以參考Xilinx官方標準。

數據文件的格式是固定的,我們在填充數據時,需要嚴格按照官方的格式進行書寫。

在示例文件中,第一行規定了數據的格式,此處規定的是二進制,那么下面的數據,我們必須用二進制的形式。大家在寫的時候,規定什么進制就用什么進制。數據與數據之間用逗號隔開,最后一個數據用分號結尾。

了解了數據文件格式之后,接下來我們提前準備一個數據文件,以便于后續我們調用IP核去使用。寫數據文件的方法有很多,在此給大家介紹一種:MATLAB。

我們打開MATLAB之后,首先先選擇一下工作路徑,以便于我們去找到我們生成的文件以及保存我們的代碼。如圖:

打開如圖所示的圖標之后,選擇好工程路徑。

選擇好之后,我們新建腳本文件,然后寫入代碼。

1 data = 0255;

2 fid = fopen('sin_data.coe','w');

3 fprintf(fid,'memory_initialization_radix = 10;

');

4 fprintf(fid,'memory_initialization_vector =

');

5 for i = 11024

6 fprintf(fid,'%d',round(127*sin(2*pi/1024*i)+127));

7

8 if i == 1024

9 fprintf(fid,';');

10 else

11 fprintf(fid,',');

12 end

13

14 if mod(i,1) == 0

15 fprintf(fid,'

');

16 end

17 end

18 fclose(fid);

寫好代碼,點擊運行,即可生成我們想要的.coe文件。數據文件準備好之后,接下來我們就可以調用IP核了。

首先我們新建一個工程

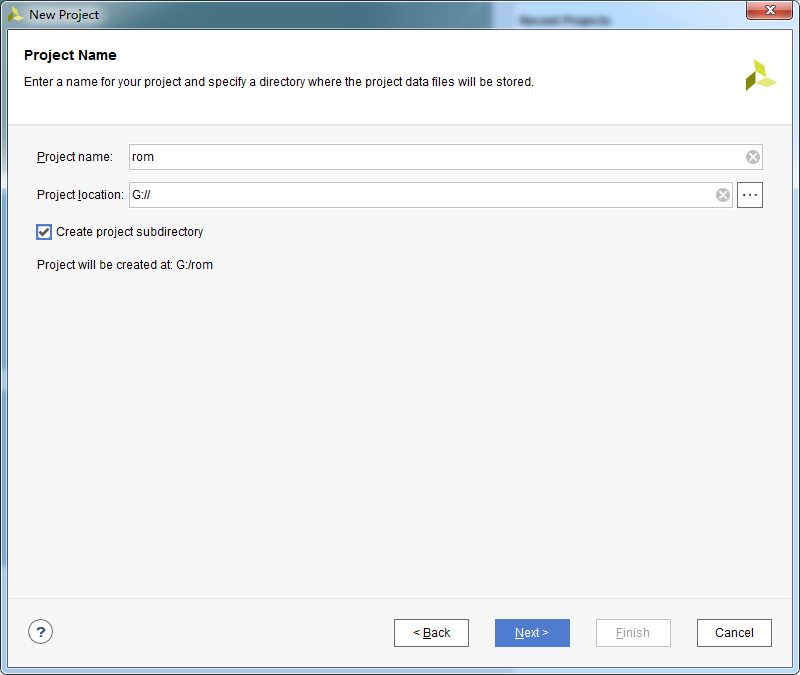

在第二步選擇路徑

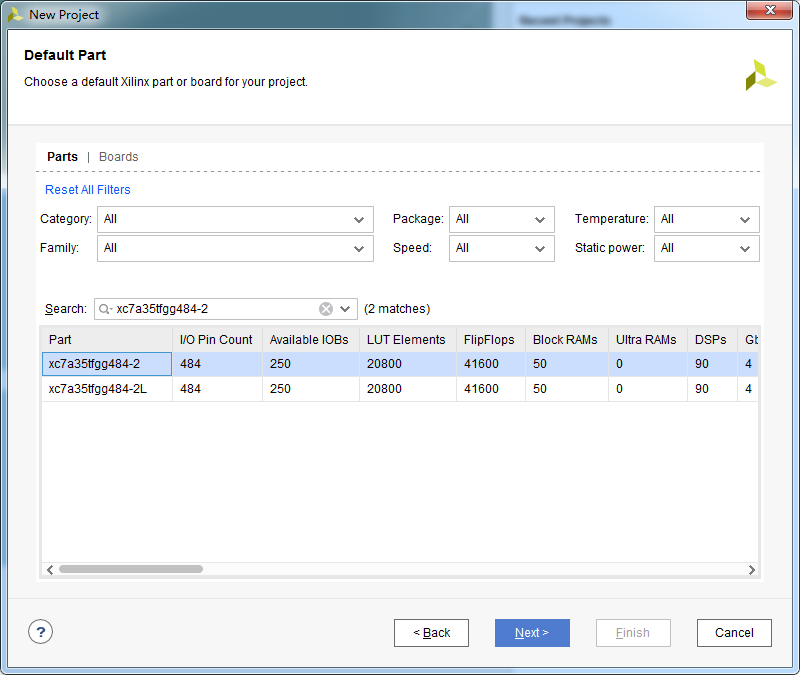

第三步直接跳過,第四步選擇我們的芯片,芯片型號為XC7A35TFGG484-2。

選中型號之后,點擊Next。

工程新建完成之后,開始新建文件。

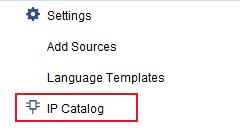

首先我們先新建IP核,打開IP Catalog,在窗口搜索block

找到如圖所示選項,然后雙擊打開。

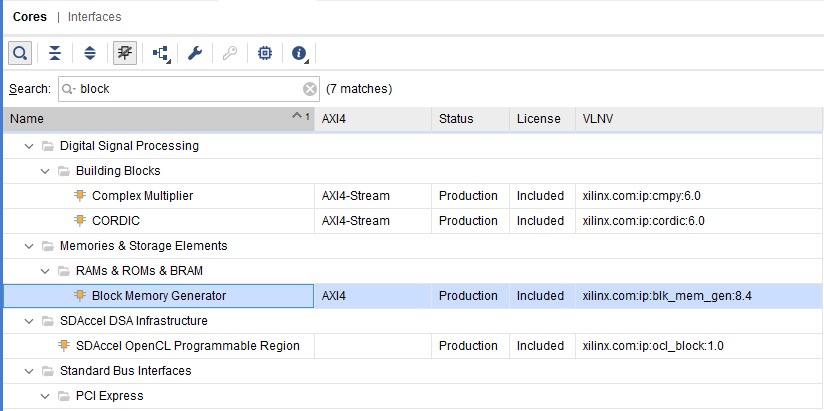

我們在框選的選項中,選擇Single Port ROM。這個選項中總共有五個選項。第一個為單端口RAM,第二個為偽雙端口RAM,第三個為真雙端口RAM,第四個為單端口ROM,第五個為真雙端口ROM。我們此次使用的是單端口ROM。

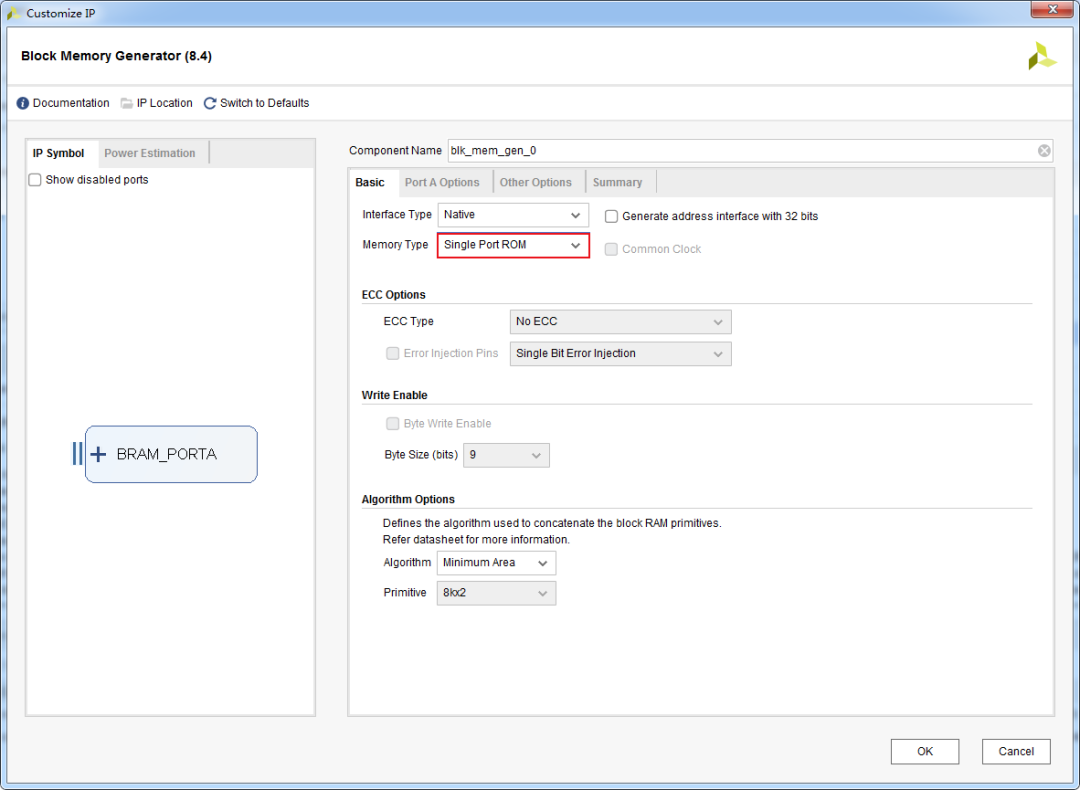

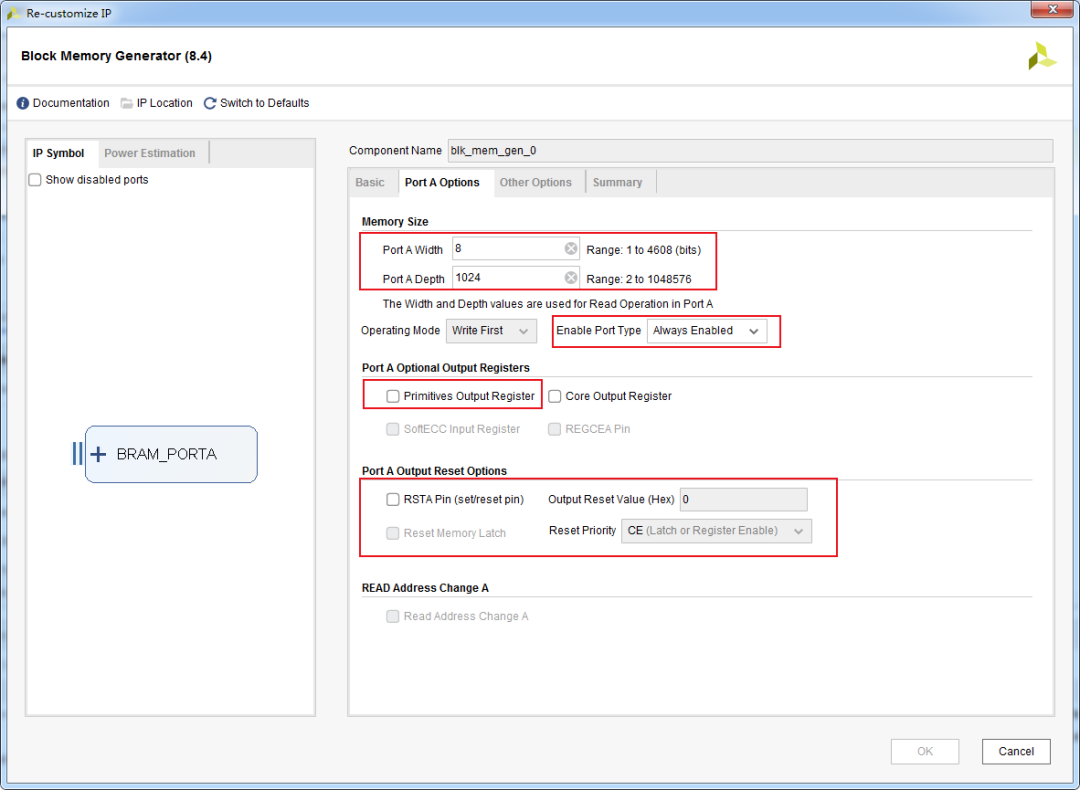

圖中框選出了四處,第一處需要我們修改一下數據的位寬以及深度,位寬我們默認使用8bit,深度為1024。因為我們在前面做了一個數據量為1024的.coe文件,所以這里深度改為1024。第二處為數據輸出使能,在此我們選擇為Always Enabled。使我們的輸出使能一直有效。第三處為輸出寄存器,輸出會在時鐘下輸出,導致結果會慢一拍,在此處我們不需要這個選項,因此取消勾選。第四處為ROM復位的設置,如果有需要,可以進行勾選,此處,我沒有使用復位信號,大家在使用時自行選擇。

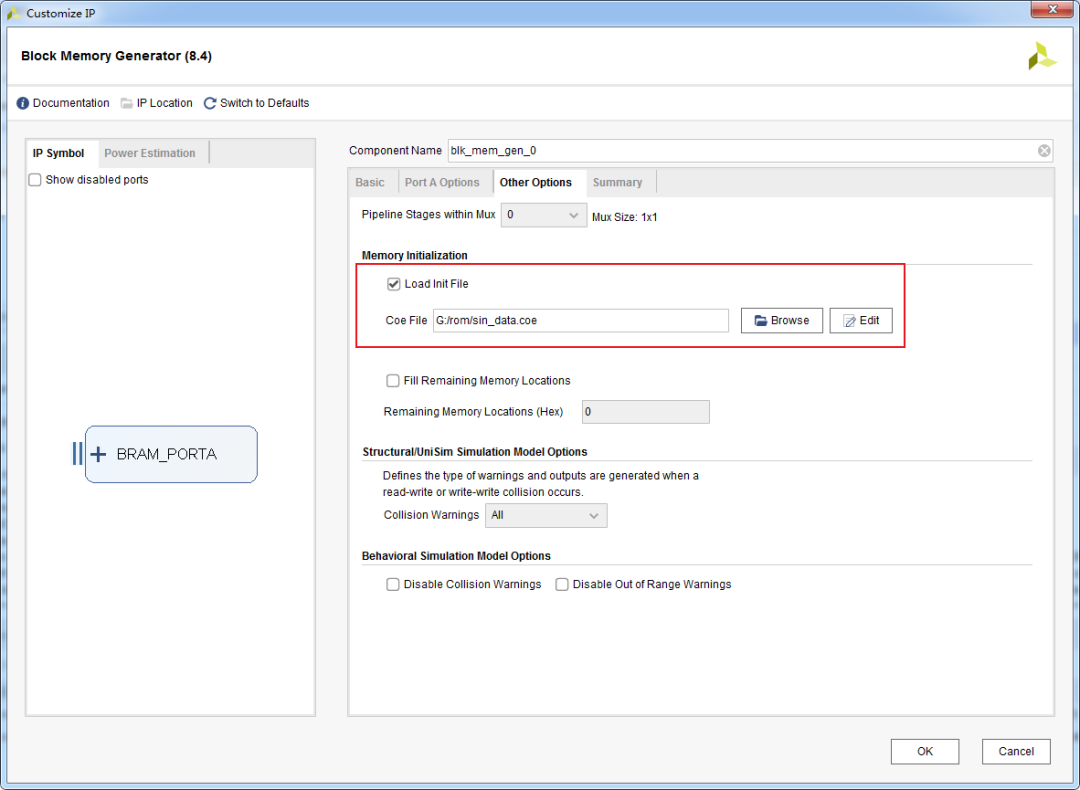

此處我們需要勾選中加載初始化文件的選項,然后點擊Browse找到我們提前生成好的數據文件。選擇好之后點擊OK,生成IP核。

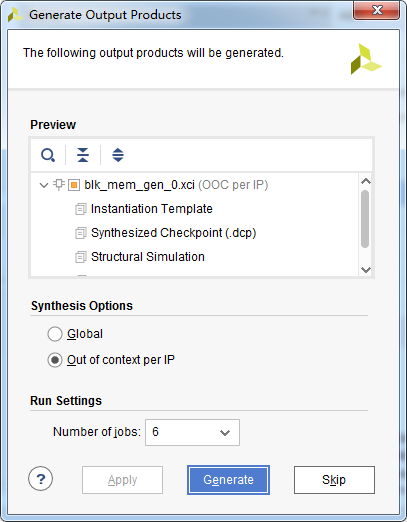

直接點擊Generate。

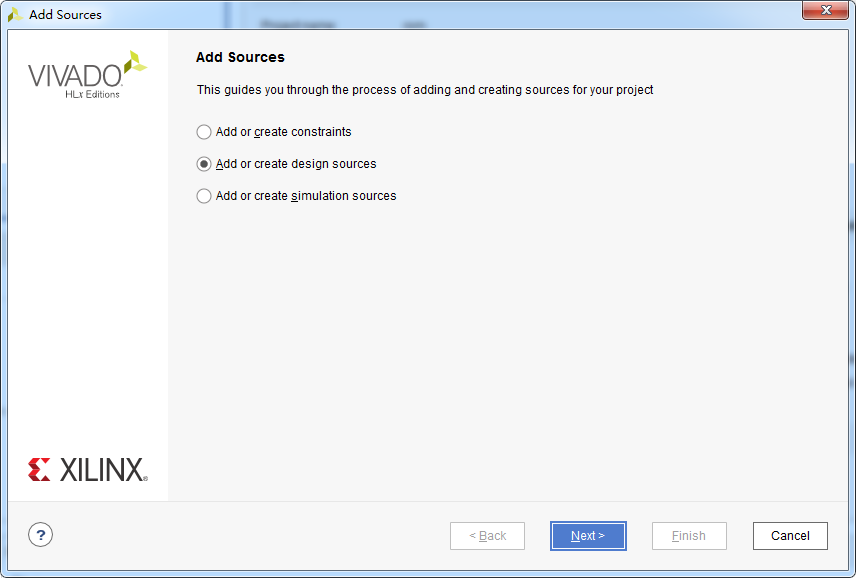

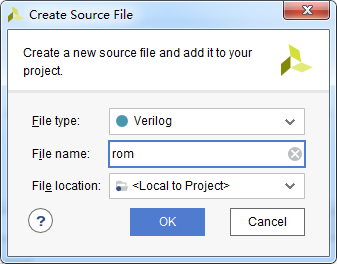

IP核生成好之后,我們新建文件,寫一下我們的地址控制模塊。代碼如下:

1 module addr_ctrl( 2 3 input wire clk, 4 input wire rst_n, 5 output reg [9:0] addr 6 ); 7 8 always @ (posedge clk, negedge rst_n) 9 begin 10 if(rst_n == 1'b0) 11 addr <= 10'd0; 12 else if(addr == 10'd1023) 13 addr <= 10'd0; 14 else 15 addr <= addr + 1'b1; 16 end 17 18 endmodule

然后我們新建頂層文件。寫好端口之后,我們將IP核與地址控制模塊例化到頂層當中。

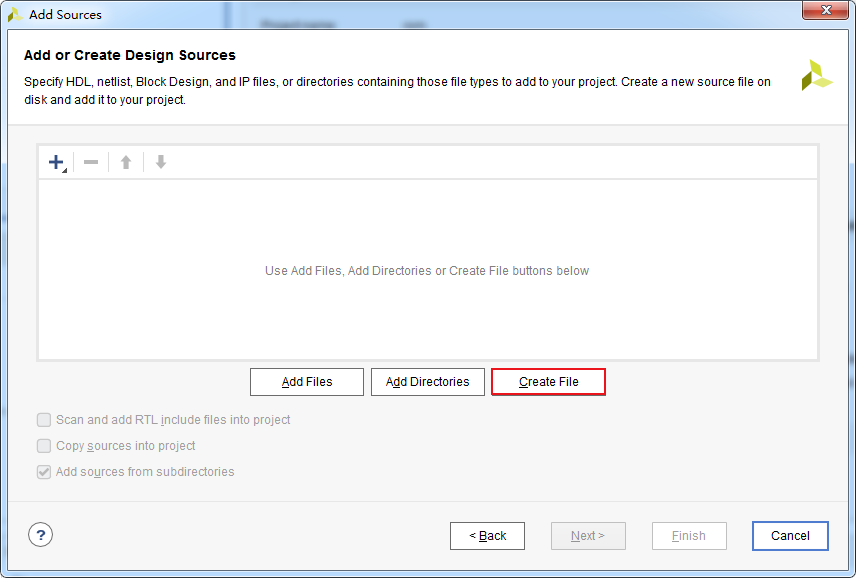

點擊Next,選擇Create File,新建頂層開始寫代碼。

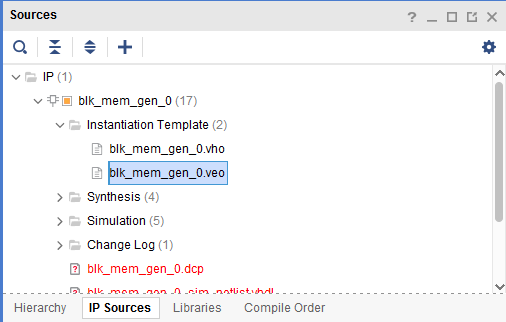

打開IP核例化的頭文件。

復制粘貼到頂層當中。地址控制模塊也同樣進行例化。頂層代碼如下:

1 module rom( 2 3 input wire clk, 4 input wire rst_n, 5 output wire [7:0] q 6 ); 7 8 wire [9:0] addr; 9 10 addr_ctrl addr_ctrl_inst( 11 12 .clk (clk), 13 .rst_n (rst_n), 14 .addr (addr) 15 ); 16 17 blk_mem_gen_0 blk_mem_gen_0_inst ( 18 .clka(clk), // input wire clka 19 .addra(addr), // input wire [9 : 0] addra 20 .douta(q) // output wire [7 : 0] douta 21 ); 22 23 endmodule

代碼寫好之后,保存編譯,沒有錯誤,那么我們寫一下仿真看一下仿真波形。

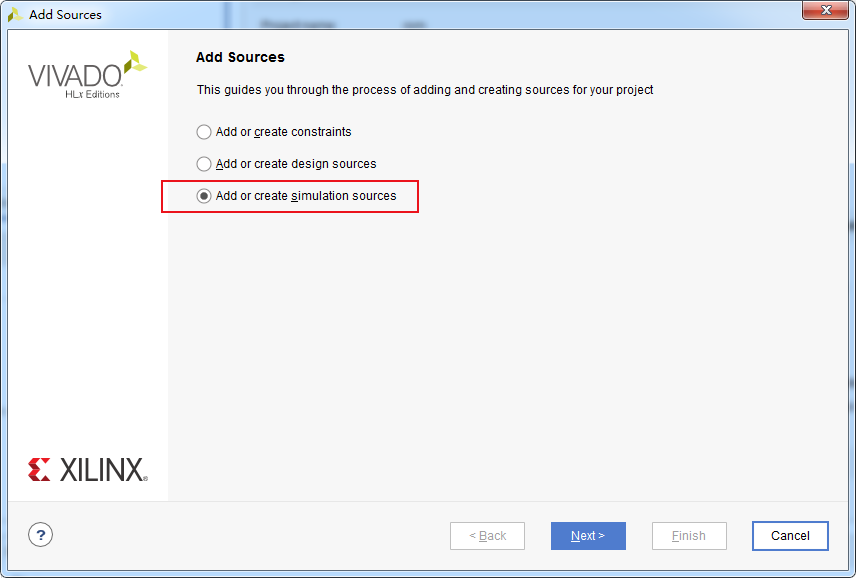

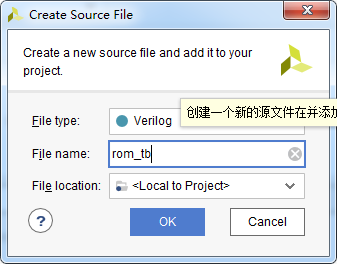

選中新建仿真文件,點擊Next輸入名字。

點擊OK,開始寫代碼。仿真代碼如下:

1 `timescale 1ns / 1ps 2 3 module rom_tb; 4 5 reg clk; 6 reg rst_n; 7 wire [7:0] q; 8 9 initial begin 10 clk = 0; 11 rst_n = 0; 12 #105; 13 rst_n = 1; 14 #10000; 15 $stop; 16 end 17 18 always #10 clk = ~clk; 19 20 rom rom_inst( 21 22 .clk (clk ), 23 .rst_n (rst_n ), 24 .q (q ) 25 ); 26 27 endmodule

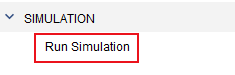

代碼寫好之后,打開仿真。

波形窗口打開后,點擊run all讓波形繼續運行

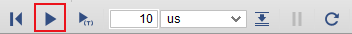

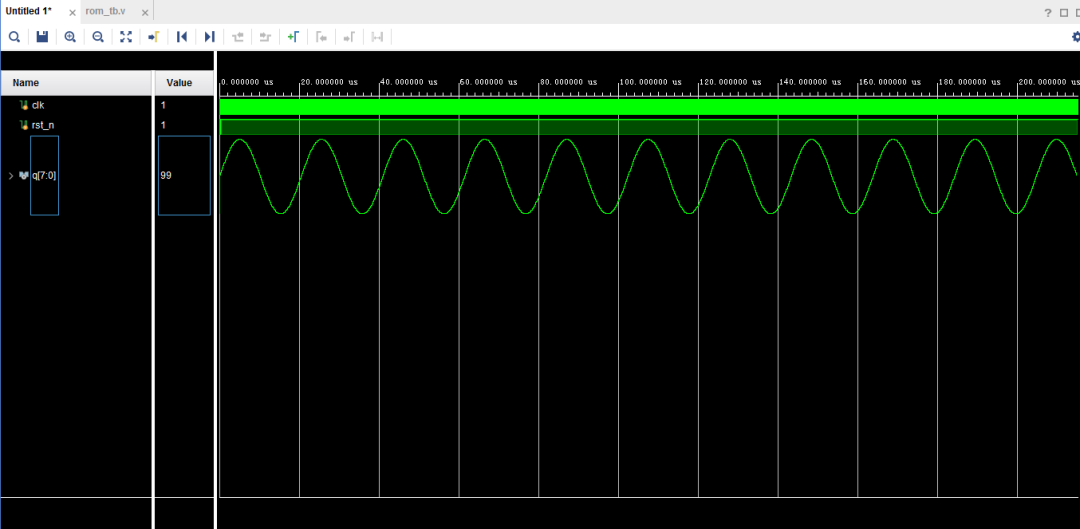

然后看到如圖所示波形。

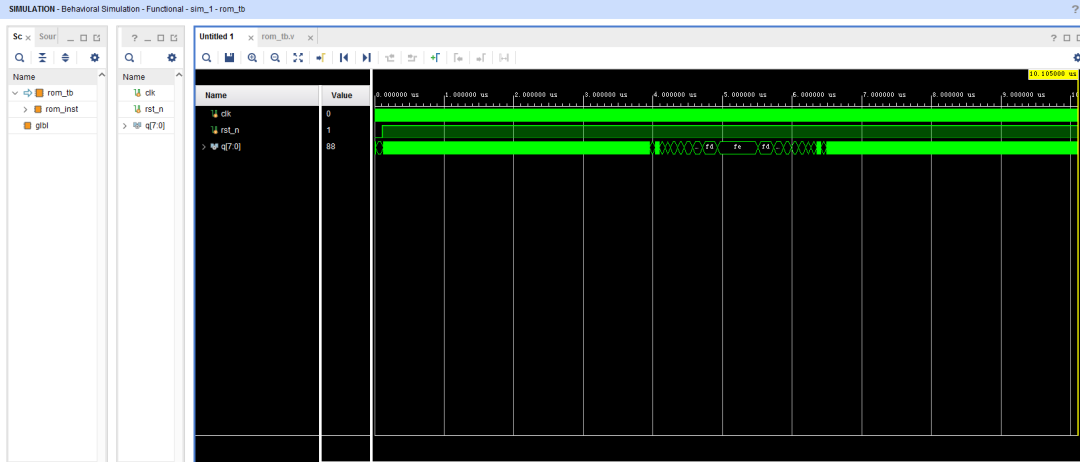

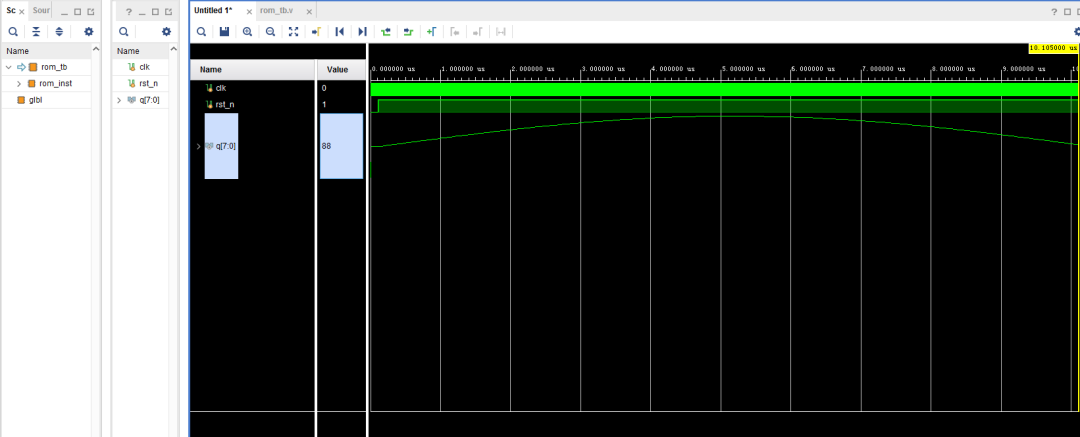

然后選中輸出q,右鍵選擇wavaform style,然后選擇analog就可以看到我們的數字信號就變成了模擬信號。

但是此時波形只有一部分,我們再次點擊run all ,然后點擊break

就可以看到完整的正弦波。

我們的數據文件就是做的正弦波,仿真顯示正確。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603013 -

ROM

+關注

關注

4文章

563瀏覽量

85733 -

Xilinx

+關注

關注

71文章

2167瀏覽量

121308 -

數據文件

+關注

關注

0文章

11瀏覽量

6564 -

Vivado

+關注

關注

19文章

812瀏覽量

66473

原文標題:FPGA零基礎學習之Vivado-ROM使用教程

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA高手的養成記:零基礎學FPGA 連載—小墨同學出品

零基礎入門FPGA,如何學習?精選資料分享

FPGA零基礎學習:IP CORE 之 ROM設計

FPGA零基礎學習之Vivado-LED流水燈實驗

FPGA零基礎學習之Vivado-數碼管驅動設計實驗

FPGA零基礎學習之Vivado-按鍵使用教程

FPGA零基礎學習之Vivado-ROM使用教程

FPGA零基礎學習之Vivado-TLC549驅動設計

FPGA零基礎學習之Vivado-按鍵使用教程

FPGA零基礎學習之Vivado-ROM使用教程

FPGA零基礎學習之Vivado-ROM使用教程

評論