本文轉(zhuǎn)自公眾號(hào),歡迎關(guān)注

SPI NAND完全解讀-基于GD5F1GM7xExxG (qq.com)

前言

SPI NAND支持QSPI接口,具備高速,高可靠,低功耗的特點(diǎn),相較于傳統(tǒng)并行接口,具有封裝體積小,引腳少,易于使用的優(yōu)勢(shì),并且可以與SPI NOR Flash共用Layout設(shè)計(jì),易于切換,使得其越來越廣泛使用。

本文以具體型號(hào)為GD5F1GM7xExxG的GD的NAND為例,對(duì)SPI NAND Flash進(jìn)行介紹。不同廠家的不同型號(hào)都大同小異了解一款其他的也就都了解了。

GD的SPI NAND Flash介紹

參考官網(wǎng):

https://www.gigadevice.com.cn/product/flash/product-series/spi-nand-flash/

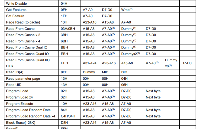

主要有1.8V和3.3V兩個(gè)電壓等級(jí),1Gb,2Gb,4Gb這幾個(gè)容量可選。

頻率133(x1,x2,x4),104(x1,x2,x4),80(x1,x2,x4)

都是2K頁(yè) 2048+64B用戶spare+64B硬件ECC

都帶硬件ECC

支持DTR

溫度:

-40℃~85℃,

-40℃~105℃

封裝:

WSON8 8x6mm,

WSON8 6x5mm,

TFBGA24 8x6mm (5x5 ball array)

下面以GD5F1GM7xExxG詳細(xì)介紹。

基本特征

l1Gb大小,塊擦除,塊含64個(gè) PAGE,PAGE編程(2KB+128B)。

l支持Standard, Dual, Quad SPI,DTR(只針對(duì)讀)

DTR即在Quad基礎(chǔ)上下邊沿都可以傳輸數(shù)據(jù),帶寬加倍,這個(gè)是一個(gè)高級(jí)功能。

l頻率

最大

Standard/Dual/Quad SPI 時(shí)133MHz

DTR Quad SPI 時(shí)104MHz 即104Mx4x2b/S, 最快104MB/S。

l軟硬件寫保護(hù),低電壓LOCK保護(hù)。

l20KB OTP區(qū)域

lPAGE編程時(shí)間320uS,塊擦除3mS,PAGE讀120uS。

lBLOCK0保證OK。

l帶ECC的P/E次數(shù)80K,符合SLC的一般水平。數(shù)據(jù)可保持10年以上。

l支持硬件ECC,默認(rèn)使能。

8位ECC編碼528B數(shù)據(jù)。

從FLASH中讀PAGE數(shù)據(jù)到CACHE中時(shí)可以自動(dòng)檢測(cè)和校正錯(cuò)誤,能夠校正的直接校正返回給用戶的就是正確的數(shù)據(jù),有狀態(tài)表示校正錯(cuò)誤狀態(tài)。額外空間有128字節(jié),64字節(jié)給用戶使用,64字節(jié)給ECC使用。

l內(nèi)部數(shù)據(jù)移動(dòng)和復(fù)制功能

這也是一個(gè)高級(jí)功能,針對(duì)FTL管理設(shè)計(jì)。

這在FTL中垃圾回收管理時(shí)非常有用,不需要再到用戶的memory里讀寫倒騰一次,就可以直接移動(dòng)和復(fù)制,并且是帶ECC操作的。

l上電自動(dòng)加載第一個(gè)塊的第一個(gè)PAGE到CACHE,并且是帶ECC校正和檢測(cè)的。

用戶可以直接讀CACHE,可以加快啟動(dòng)時(shí)間。

有兩個(gè)緩存data register 和 cache register,前者更接近于memory陣列,所以作為NAND Flash存儲(chǔ)陣列操作的緩存,后者更接近IO,所以作為IO操作的數(shù)據(jù)緩存。

cache register使得可以進(jìn)行頁(yè)內(nèi)的隨機(jī)讀寫,和copy back操作。

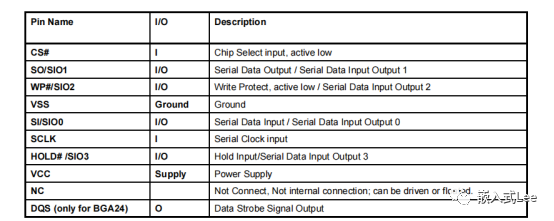

引腳

CS默認(rèn)必須拉高,DQS不使用必須浮空

WP和HOLD不用必須拉高。

框圖

其中cache memory包括data register 和 cache register兩個(gè)PAGE大小的緩存。

地址

CA:即列地址,頁(yè)內(nèi)地址, 雖然12位可以表示04095,但是實(shí)際范圍是02175. 即2K+128字節(jié)的頁(yè)空間。

列地址可以理解為矩陣幾行幾列的列。列地址即一行數(shù)據(jù)(頁(yè))里面的偏移。

RA:行地址, RA<5:0>表示頁(yè)地址,RA<15:6>表示塊地址。

存儲(chǔ)組織

頁(yè)大小是2K+128,一個(gè)塊有64個(gè)頁(yè),以鞏固1024個(gè)塊。

一個(gè)PAGE有128字節(jié)的額外存儲(chǔ)空間,其中前面的64字節(jié)是給用戶用的,FTL的管理使用。后面64字節(jié)是硬件ECC使用。

使能CECC時(shí)后面的64字節(jié)用戶不能寫但是可以讀。

硬件ECC不使能時(shí),整個(gè)128字節(jié)用戶都可以讀寫。

設(shè)備操作

SPI接口

支持兩種模式

模式0 CPOL = 0, CPHA = 0 CLK默認(rèn)低,第一個(gè)邊沿鎖存數(shù)據(jù)(第一個(gè)上升沿)

模式3 CPOL = 1, CPHA = 1 CLK默認(rèn)高,第二個(gè)邊沿多存數(shù)據(jù)(第一個(gè)上升沿)

兩種方式都是上升沿設(shè)備輸入數(shù)據(jù)鎖存SI,然后下降沿主機(jī)輸入數(shù)據(jù)鎖存SO。

如下圖所示

CS拉低是一次通訊的開始,

在SCLK的上升沿SI鎖存數(shù)據(jù)(設(shè)備鎖存數(shù)據(jù)):注意發(fā)送端實(shí)際在前一個(gè)下降沿就已經(jīng)開始輸出數(shù)據(jù),因?yàn)閿?shù)據(jù)需要有建立時(shí)間,然后上升沿設(shè)備對(duì)SI數(shù)據(jù)鎖存,在下一個(gè)下降沿主機(jī)結(jié)束數(shù)據(jù)輸出。

也就是SCLK為低時(shí)是SI的數(shù)據(jù)建立時(shí)間,SCLK為高時(shí)時(shí)SI的數(shù)據(jù)保持時(shí)間。

主機(jī)是在下降沿修改SI的數(shù)據(jù)的。

在SCLK的下降沿SO鎖存數(shù)據(jù)(主機(jī)鎖存數(shù)據(jù)):注意發(fā)送端實(shí)際在前一個(gè)上升降沿就已經(jīng)開始輸出數(shù)據(jù),因?yàn)閿?shù)據(jù)需要有建立時(shí)間,然后下降沿主機(jī)對(duì)SO數(shù)據(jù)鎖存,在下一個(gè)上升沿沿設(shè)備結(jié)束數(shù)據(jù)輸出。

也就是SCLK為高時(shí)是SO的數(shù)據(jù)建立時(shí)間,SCLK為低時(shí)是SO的數(shù)據(jù)保持時(shí)間。

設(shè)備是在上升沿修改SO的數(shù)據(jù)的。

所以理想狀態(tài)是SCLK的上升沿在SI數(shù)據(jù)的中間。

在SCLK的下降沿在SO數(shù)據(jù)的中間。

還有就是需要注意下是高位在前的發(fā)送順序。

還有就需要注意,CS是高時(shí)如果是模式0則SCLK要保持低,如果是模式3則需要保持高,不能翻轉(zhuǎn)。只有CS拉低之后SCLK才能產(chǎn)生時(shí)鐘。

默認(rèn)最好硬件上拉CS,即不使用SPI FLASH時(shí),設(shè)備處于idle狀態(tài)。

標(biāo)準(zhǔn)SPI

發(fā)送命令時(shí),和普通IO命令,都是用該模式

SCLK,CS,SI只做輸入,SO只做輸出

DualSPI

在使用x2 和 dual IO命令時(shí)的后面數(shù)據(jù)階段:

SI變?yōu)镾IO0 雙向

SO變?yōu)镾IO1 雙向

Quad SPI

在使用x4 和 Quad IO命令時(shí):的后面數(shù)據(jù)階段

SI變?yōu)镾IO0 雙向

SO變?yōu)镾IO1 雙向

WP變?yōu)镾IO2 雙向

HOLD變?yōu)镾IO3 雙向

DTR Quad SPI

在狀態(tài)寄存器的QE位置位,且使用DTR Quad I/O Fast Read命令時(shí)的數(shù)據(jù)階段

在Quad SPI基礎(chǔ)上,SCLK的上升沿和下降沿都鎖存數(shù)據(jù)

HOLD模式

只有在QE=0時(shí)才支持該功能,如果QE=1則是使用DTR Quad SPI,HOLD引腳變?yōu)榱薙IO3.

在CS保持低時(shí),HOLD拉低可以只暫停但是不停止正在進(jìn)行的讀,寫,擦除操作。

HOLD的下降沿之后到SCLK變?yōu)榭臻e電平開始HOLD開始,

HOLD的上升沿之后SCLK變?yōu)榭臻e電平開始HOLD結(jié)束。

在HOLD階段SO高阻態(tài),SI和SCLK被忽略掉。

如果HOLD時(shí)CS拉高,則會(huì)復(fù)位內(nèi)部狀態(tài)機(jī)邏輯結(jié)束操作,重新開始操作需要HOLD拉高CS拉低。

寫保護(hù)

WP用于硬件寫保護(hù), QE=0時(shí)才支持該模式.

WP為低時(shí)(BP0, BP1, BP2 和INV, CMP)不可寫。

BRWD= 1,WP=0時(shí) 上述塊保護(hù)位不能修改。

掉電時(shí)序

避免在寫和擦除時(shí)掉電,或者在電壓低時(shí)操作。寫操作或者擦除進(jìn)行中掉電會(huì)導(dǎo)致數(shù)據(jù)丟失或者損壞。問題:這里的丟失和損壞的影響域是什么,寫PAGE則指揮這一個(gè)PAGE損壞,擦除BLOCK只有這個(gè)BLOCK損壞嗎? 損壞只是數(shù)據(jù)不對(duì),后面擦除就可以重新使用還是變?yōu)閴膲K?

DQS信號(hào)

DQS信號(hào)用于表示READ時(shí)輸出數(shù)據(jù)是否有效。DQS只在BGA24封裝有,用于高速傳輸時(shí),相當(dāng)于流控。只在 EEh命令用到。

設(shè)備接收到EEH命令時(shí)拉低QDS,表示忙,此時(shí)輸出數(shù)據(jù)無效,因?yàn)樵O(shè)備還在進(jìn)行內(nèi)部處理,當(dāng)DTR模式輸出數(shù)據(jù)到IO引腳上時(shí)拉高DQS,表示數(shù)據(jù)就緒,主機(jī)就可以讀數(shù)據(jù)了,相當(dāng)于流控。

DQS的翻轉(zhuǎn)速度和CLK頻率是一樣的,DTR讀時(shí)數(shù)據(jù)必須在DQS的上升沿和下降沿鎖存數(shù)據(jù)。這個(gè)引腳不使用時(shí)必須浮空。

命令表

注意讀cache都需要有dummy,即需要等待一段時(shí)間讓設(shè)備準(zhǔn)備就緒。

FFH Reset命令會(huì)復(fù)位PAGE READ/PROGRAM/ERASE操作

復(fù)位狀態(tài)寄存器P_FAIL/E_FAIL/WEL/OIP/ECCS/ECCSE

上電時(shí)序

需要注意的就是Vcc(min)之后至少需要tVSL時(shí)間之后才能拉低CS,之前必須一致保持高。

還有就是要注意Vwi,低于該電壓不允許寫,所以在設(shè)計(jì)電壓看門狗,和掉電保護(hù)電路時(shí)需要考慮該值,留有一定裕度。

性能參數(shù)和時(shí)序

注意軟復(fù)位0xFF之后需要延遲500uS以上才能發(fā)送下一個(gè)命令。

注意兩個(gè)參數(shù)

輸入信號(hào)的高低電平門限

低電平需要低于0.2VCC,高電平需要高于0.8VCC,這個(gè)需要測(cè)試下,保證IO能拉低到足夠低,拉高到足夠高。很多硬件設(shè)計(jì)有保護(hù)電路,上下拉電阻,串電阻導(dǎo)致分壓,三極管二極管壓降等導(dǎo)致電壓不夠足夠低或者足夠高,就不是很保險(xiǎn)。

這里還有個(gè)參數(shù)需要注意下

正負(fù)過充不能超過2V,20nS,這個(gè)需要實(shí)際測(cè)試,理論上就不應(yīng)該有過充,有些環(huán)境或者設(shè)計(jì)可能無法消除,也要保證不超過該值,越小越好。

壞塊

保證壽命時(shí)間內(nèi),最多有20個(gè)壞塊,壞塊標(biāo)記是塊的spare區(qū)域的第一個(gè)字節(jié)0x800處為0x00,檢測(cè)的話非0xFF即認(rèn)為壞塊。

操作

讀比編程的指令更多,讀可以使用x1,x2,x4,x4 DTR,且命令之后的Dummy和地址頁(yè)也可以x2,x4,x4 DTR。

而編程只有x1,x4,沒有DTR,命令之后的Dummy和地址也只能x1。

寫禁止/使能(0x06/0x04)

寫使能 直接發(fā)送0x06命令即可

頁(yè)編程,OTP保護(hù)和OTP編程,塊擦除前都需要寫使能。

寫使能生效后0xC0的寄存器WEL位置位

所以一般發(fā)送寫使能命名后要查詢?cè)撐淮_認(rèn)是否使能。

注意以上編程操作之后WEL自動(dòng)清0進(jìn)入寫禁止?fàn)顟B(tài),這樣做是為了安全避免誤觸發(fā)寫。

寫禁止 直接發(fā)送0x04命令即可

該命令幾乎用不到,因?yàn)槟J(rèn)上電WEL就是0寫禁止的,每次編程操作之后硬件也會(huì)自動(dòng)清零WEL進(jìn)入寫禁止?fàn)顟B(tài)。

讀

讀需要先通過0x13從FLASH中讀出數(shù)據(jù)到緩存中,然后通過0x03/0x0B,0x3B,0x6B等指令從緩沖區(qū)中隨機(jī)地址開始讀出數(shù)據(jù)。

0x03/0x0B,0x3B,0x6B除了數(shù)據(jù)階段前面的時(shí)序都是一樣的,數(shù)據(jù)階段分別使用x1,x2,

X4位。

讀到2048+128后繞回從0開始繼續(xù)。

使用4個(gè)引腳的指令需要先使能0xB0寄存器的QE 位。

讀ID(0x9F)

先發(fā)命令再9=8個(gè)Dummy Cycles,然后連續(xù)讀2個(gè)字節(jié)的數(shù)據(jù)。

返回MID和DID可以用于區(qū)分具體的型號(hào),具體值可以參考手冊(cè)。

以下是一個(gè)實(shí)測(cè)波形

讀PAGE(0x13)

0x13命令將FLASH中的頁(yè)讀到緩存中,需要提供24位的PAGE地址。設(shè)備收到地址后tRD時(shí)間內(nèi)將FLASH讀到緩沖中, 主機(jī)需要讀寄存器0xC0的OIP位,等待OIP為0表示完成。

整個(gè)流程如下

拉低CS,發(fā)0x13H的命令,然后發(fā)24位地址,再釋放CS,命令發(fā)送階段完成。

然后是狀態(tài)查詢階段,即讀0xC0寄存器的OIP位,詳見讀寄存器章節(jié)的說明。

從緩沖區(qū)讀數(shù)據(jù)(0x03/0x0B)

上述的PAGE讀到緩沖區(qū)后,主機(jī)就可以從緩沖區(qū)隨機(jī)讀數(shù)據(jù)了。

需要注意的是發(fā)送完命令后需要等4個(gè)Dummy cycles。然后發(fā)送12位的PAGE內(nèi)開始地址,然后再等待8個(gè)Dummy Cycles,然后就連續(xù)讀數(shù)據(jù)。

注意如果時(shí)鐘不停,CS不拉高則設(shè)備會(huì)一直吐數(shù)據(jù),地址繞到2048+128的頁(yè)邊界后又從0開始繞回繼續(xù)。注意這里的邊界是2048+128而不是2048+64.

X2模式從緩沖區(qū)讀數(shù)據(jù)(0x3B)

前面和0x03/0xB都是一樣的,先發(fā)8位命令,接下來4位Dummy cycles,然后12位頁(yè)內(nèi)偏移地址,然后8個(gè)dummy cycles。

后面數(shù)據(jù)階段則不一樣,使用了IO0和IO1,IO0和IO1表示兩位IO1表示高位,然后從高位開始輸出,即4個(gè)Cycles吐出一個(gè)字節(jié)的數(shù)據(jù)。

X4模式從緩沖區(qū)讀數(shù)據(jù)(0x6B)

該模式前面和0x03/0xB的時(shí)序都是一樣的,從數(shù)據(jù)階段開始不一樣

使用了IO0和IO1,IO2,IO3,表示4位IO3表示高位,然后從高位開始輸出,即2個(gè)Cycles吐出一個(gè)字節(jié)的數(shù)據(jù)。

Dual IO****模式從緩沖區(qū)讀數(shù)據(jù)(0xBB)

與0x3B的區(qū)別是,0xBB只有命令字使用單IO,其他所有數(shù)據(jù)都是使用雙IO。

Quad IO****模式從緩沖區(qū)讀數(shù)據(jù)(0xEB)

與0x6B的區(qū)別是,0xEB只有命令字使用單IO,其他所有數(shù)據(jù)都是使用4IO。

Quad I/O DTR****模式從緩沖區(qū)讀數(shù)據(jù)(0xEE)

除了命令字節(jié),其他的上升沿和下降沿都可以傳輸數(shù)據(jù),使用4個(gè)IO。

不使用DQS

使用DQS

在Dummy和地址階段DQS為低,在數(shù)據(jù)階段DQS的雙邊沿鎖存數(shù)據(jù)。其他時(shí)候高阻態(tài)。

讀UID

UID是設(shè)備獨(dú)特碼,可以用于認(rèn)證,設(shè)備編碼等場(chǎng)景。

共32字節(jié),前面16字節(jié)和后面16字節(jié)是取反的關(guān)系,所以異或前后16字節(jié)應(yīng)該全部是0xFF。

為了可靠,避免bit錯(cuò)誤導(dǎo)致讀出錯(cuò)誤,UID總共存了16份,如果前面的校驗(yàn)錯(cuò)誤(前后16字節(jié)異或不為0xFF),則可以繼續(xù)偏移32字節(jié)用后面的。

讀之前需要設(shè)置B0寄存器的OTP_EN為1.

然后回讀確認(rèn)OTP_EN為1

然后用0x13指令讀FLASH到緩沖區(qū),24位地址寫0.

確認(rèn)OIP讀完

然后用0x03/0x0B讀UID數(shù)據(jù),可以一次讀32x16字節(jié),也可以一次讀32字節(jié)檢查不對(duì)再讀后面的。

讀參數(shù)頁(yè)

參數(shù)頁(yè)是一些描述芯片的組織,特征,時(shí)序和行為的參數(shù)。為了可靠數(shù)據(jù)至少存了3份,即至少有3個(gè)頁(yè)。

執(zhí)行過程和讀UID一樣,只是24位地址變?yōu)榱?.

讀之前需要設(shè)置B0寄存器的OTP_EN為1.

然后回讀確認(rèn)OTP_EN為1

然后用0x13指令讀FLASH到緩沖區(qū),24位地址寫1.

確認(rèn)OIP讀完

然后用0x03/0x0B讀緩存區(qū)中的數(shù)據(jù)。

參數(shù)頁(yè)符合ONFI標(biāo)準(zhǔn)(https://www.onfi.org/),比如uC-FS的NAND的FTL層就支持使用ONFI模式自動(dòng)配置NAND參數(shù)。

編程

先用0x02或者0x32指令將數(shù)據(jù)寫入緩沖區(qū)

然后0x06寫使能,確認(rèn)寫使能成功

然后0x10執(zhí)行緩沖區(qū)到FLASH的寫

最后0x0F讀寄存器0xC0確認(rèn)P_FAIL是否有錯(cuò),OIP是否完成

注意(84h/C4h/34h) 和(FFh) 指令是不會(huì)清除緩存中的內(nèi)容的,所以下次編程時(shí)要注意是否緩存區(qū)都是需要更新的數(shù)據(jù),所以必須是一次更新整個(gè)緩沖區(qū),不要部分更新。

0x02和0x32指令之后緊接著0x10則未被0x02和0x32指令更新的緩沖區(qū)區(qū)域的值變?yōu)?xFF。

(84h/C4h/34h) 指令之后緊接著0x10指令,緩沖區(qū)的內(nèi)容寫入NAND FLASH中。

編程地址按照塊的順序

QE=1時(shí)才能使用0x32指令

如果寫緩沖區(qū),繞到了緩沖區(qū)邊界2176,后面的數(shù)據(jù)忽略而不是繞回,這個(gè)和讀是不一樣的。如果使能ECC寫最后面的64字節(jié)是忽略的。

編程加載PL(0x02)

8位命令0x02后是4個(gè)Dummy Cycles,然后是12位頁(yè)內(nèi)偏移地址,然后是數(shù)據(jù)。

使能ECC時(shí)只能寫2112個(gè)字節(jié),否則可寫2176個(gè)字節(jié)。

編程加載PLx4(0x32)

必須QE=1

使能ECC時(shí)只能寫2112個(gè)字節(jié),否則可寫2176個(gè)字節(jié)。

前面時(shí)序一樣,從數(shù)據(jù)階段開始使用4xIO

編程執(zhí)行PE(0x10)

需要指定24位的PAGE地址, 執(zhí)行后需要等待tPROG時(shí)間等待編程完,

可以查詢0xC0寄存器的P_FAIL和OIP

注意編程完成后會(huì)自動(dòng)寫禁止,且緩沖區(qū)中的數(shù)據(jù)變得無效。

編程加載隨機(jī)數(shù)據(jù)(0x84)

該指令和0x02的區(qū)別是,0x02一次更新整個(gè)緩沖區(qū)的數(shù)據(jù),而本指令可以更新一部分緩沖區(qū)的數(shù)據(jù),多次執(zhí)行可以更新不連續(xù)的區(qū)域。

編程加載隨機(jī)數(shù)據(jù)x4(0xC4/0x34)

和0x84一樣,只是數(shù)據(jù)階段使用4個(gè)IO

必須QE=1

內(nèi)部數(shù)據(jù)移動(dòng)

0x13讀PAGE數(shù)據(jù)到緩沖區(qū)

84H/C4H/34H 編程加載隨機(jī)數(shù)據(jù)到緩沖區(qū)(可選更新部分?jǐn)?shù)據(jù)),如果有多個(gè)零散的區(qū)域更新則需要執(zhí)行多次。

0x06寫使能

0x10執(zhí)行緩沖到NAND的寫

0x0F查詢狀態(tài)

塊擦除操作(0xD8)

先0x06寫使能

0xD8擦除,指定24位頁(yè)地址

等待tBERS 時(shí)間

0x0F讀0xC0的E_FAIL和OIP查詢狀態(tài)

復(fù)位

軟復(fù)位(0xFF)

停止操作進(jìn)入idle狀態(tài)

軟復(fù)位后的寄存器值參考手冊(cè)

使能上電復(fù)位和上電復(fù)位(0x66,0x99)

比軟件復(fù)位更徹底,即和上電復(fù)位一樣的效果,寄存器值也和上電復(fù)位一樣。

復(fù)位完需要等待tVSL 時(shí)間,然后讀OIP確認(rèn)空閑再進(jìn)行其他操作。

正在編程的存儲(chǔ)器位置或正在擦除的塊的內(nèi)容不再有效。

先發(fā)0x66使能再發(fā)0x99執(zhí)行操作

特征操作與讀寫寄存器

寄存器用于控制行為,表示狀態(tài)

其中狀態(tài)寄存器0xC0 0xF0是只讀的,除了WEL可以通過0x06指令修改。

特征和保護(hù)寄存器0xA0 0xB0 0xD0可以讀寫進(jìn)行配置。

注意OTP_PRT是非易失的即掉電保存的,其他的是掉電不保存。

特征寄存器一直保持直到上電復(fù)位或者重新修改。0xFF軟復(fù)位不會(huì)清除。

保留值只能寫0

QE=1才能使用4xIO

BRWD=1且WP為低時(shí)則不能修改塊保護(hù)配置

寄存器如下

默認(rèn)值分別是

0xA0 0x38

0xB0 0x10

0xC0 0x00

0xD0 0x00

0xF0 0x08

寄存器的一些狀態(tài)位信息

ECC信息

驅(qū)動(dòng)能力

OTP

提供一個(gè)受保護(hù)的10個(gè)PAGE大小的一次可編程區(qū)域。訪問OTP的10個(gè)頁(yè)需要按如下修改對(duì)應(yīng)寄存器位。

PAGE0存UID

PAGE1存參數(shù)頁(yè)

PAGE2-PAGE11 用戶使用(只能通過0x02+0x10進(jìn)行編程),0x13+03H/0BH/3BH/6BH/BBH/EBH 讀出。需要按照如下設(shè)置OTP_PRT OTP_EN設(shè)置訪問屬性。寫的話先使能OTP的寫然后0x06寫使能,再編程。

塊保護(hù)

電源鎖定保護(hù)

BPL=1時(shí) 塊保護(hù)BP[0,2] , INV , CMP 和BRWD 將無法再修改除非掉電重啟。

可以用于QE模式?jīng)]有WP硬件保護(hù)時(shí),軟件進(jìn)行保護(hù),保護(hù)kuai塊保護(hù)狀態(tài)不被修改。

ECC

ECC_EN默認(rèn)為1,軟件可以修改使能或者禁用硬件ECC,

寫數(shù)據(jù)硬件自動(dòng)計(jì)算ECC,此時(shí)最后64字節(jié)用戶不能寫,讀時(shí)自動(dòng)進(jìn)行數(shù)據(jù)校正,狀態(tài)信息更新到ECCS0/1 ECCSE0/1

布局如下,使能ECC時(shí)最后64字節(jié)可讀不可寫

讀寄存器(0x0F)

先發(fā)0x0F再發(fā)地址,無需dummy,然后讀字節(jié)

只有普通SPI模式

以下是實(shí)測(cè)不同寄存器的波形

寫寄存器(0x1F)

先發(fā)0x1F再發(fā)地址,無需dummy,然后寫字節(jié)

只有普通SPI模式

休眠操作

只針對(duì)1.8V的設(shè)備

進(jìn)入休眠(0xB9)

此模式忽略所有的編程操作,收到指令tDP 時(shí)間后進(jìn)行真正的休眠

只接受0xAB 0xFF 0x66 0x99指令

退出休眠(0xAB)

上電復(fù)位 或者0xAB指令

收到指令后tRES1 時(shí)間才可查詢狀態(tài),進(jìn)行后續(xù)操作

總結(jié)

以上基于GD5F1GM7xExxG的GD的NAND為例,對(duì)SPI NAND Flash進(jìn)行了詳細(xì)的介紹,對(duì)于驅(qū)動(dòng)編寫來說重點(diǎn)關(guān)注其波形,所以邏輯分析儀不可少,然后是關(guān)注寫保護(hù)相關(guān)的操作量產(chǎn)時(shí)合適的保護(hù)可以避免異常的改寫數(shù)據(jù)。

-

嵌入式

+關(guān)注

關(guān)注

5082文章

19104瀏覽量

304800 -

NAND

+關(guān)注

關(guān)注

16文章

1681瀏覽量

136118 -

FlaSh

+關(guān)注

關(guān)注

10文章

1633瀏覽量

147939 -

SPI

+關(guān)注

關(guān)注

17文章

1706瀏覽量

91502

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

5CGTFD7D5F27C7N Intel/Altera可編程邏輯器件(CPLD/FPGA)

【GD32 MCU 移植教程】9、從 STM32F10x 系列移植到 GD32F30x 系列

【GD32 MCU 移植教程】7、從 GD32F10x 移植到 GD32E103

【GD32 MCU 移植教程】6、從GD32F1x0和GD32F3x0移植到GD32E230

【GD32 MCU 移植教程】5、GD32E230 系列移植到 GD32F330 系列

【GD32 MCU 移植教程】2、從 GD32F303 移植到 GD32F503

【GD32 MCU 移植教程】1、從 GD32F10x 移植到 GD32F30x

GD32F407 SPI數(shù)據(jù)異常的原因?

SD NAND、SPI NAND和eMMC的區(qū)別對(duì)比分析

Verilog:【8】基于FPGA實(shí)現(xiàn)SD NAND FLASH的SPI協(xié)議讀寫

【GD32F303紅楓派開發(fā)板使用手冊(cè)】第二十講 SPI-SPI NAND FLASH讀寫實(shí)驗(yàn)

SD NAND和SPI NAND的區(qū)別

【GD32H757Z海棠派開發(fā)板使用手冊(cè)】第十一講 SPI-SPI NOR FLASH讀寫實(shí)驗(yàn)

【GD32F470紫藤派開發(fā)板使用手冊(cè)】第十一講 SPI-SPI NOR FLASH讀寫實(shí)驗(yàn)

SPI NAND完全解讀-基于GD5F1GM7xExxG

SPI NAND完全解讀-基于GD5F1GM7xExxG

評(píng)論