毫米波 (mmWave) 成像已成為機(jī)場(chǎng)、公共建筑和體育場(chǎng)館安防掃描系統(tǒng)的重要組成部分。毫米波掃描儀優(yōu)于傳統(tǒng)金屬探測(cè)器,因?yàn)樗鼈兛梢宰R(shí)別和定位金屬和非金屬威脅。本文 介紹 了 毫米波 成像 硬件 的 工作 原理, 并 將 介紹 一種 芯片 組, 該 芯片 組 使用 邊緣 處理 來(lái) 管理 大量 數(shù)據(jù) 負(fù)載, 從而 支持 漫游 安全 掃描 系統(tǒng) 的 開發(fā)。

毫米波成像的工作原理

圖 1 說(shuō)明 了 毫米波 掃描 器 的 工作 原理。該系統(tǒng)由連接到空間分散天線陣列的發(fā)射器和接收器陣列組成。該系統(tǒng)類似于測(cè)量回波損耗或S11的網(wǎng)絡(luò)分析儀。在任何時(shí)候,陣列中的一個(gè)天線都在以單個(gè)頻率發(fā)射低功率信號(hào)。該信號(hào)從目標(biāo)反射并產(chǎn)生反向散射(插圖顯示了目標(biāo)上單個(gè)點(diǎn)的反射,但實(shí)際上傳輸?shù)男盘?hào)是全向的,因此目標(biāo)上的多個(gè)點(diǎn)會(huì)有反射)。

反向散射的相位和幅度由陣列中的所有接收天線測(cè)量。發(fā)射天線和接收天線之間可以使用極化,以減少直接發(fā)射到接收泄漏。測(cè)量完成后,從另一個(gè)發(fā)射天線(以相同頻率工作)發(fā)射相同的信號(hào),并重復(fù)測(cè)量過(guò)程。

由于RF信號(hào)的穿透深度和反射的性質(zhì)隨頻率而變化,因此前面描述的掃描通常在多個(gè)頻率下在寬帶上重復(fù)。由此產(chǎn)生的矢量矩陣形成一個(gè)多維數(shù)組(相對(duì)于頻率和空間位置),用于創(chuàng)建可以識(shí)別隱藏在衣服層之間和下方的金屬和非金屬物體的圖像。

完成此類掃描所需的硬件必須是多通道的,并且具有較寬的工作頻率范圍。10 GHz 至 40 GHz 的頻率范圍足夠?qū)挘阋詤^(qū)分典型安全掃描場(chǎng)景中的對(duì)象(衣服、背包、武器和爆炸物)。較高的通道數(shù)系統(tǒng)往往具有更高的分辨率,使它們能夠識(shí)別小物體。例如,雖然檢測(cè)剃須刀片在機(jī)場(chǎng)掃描儀中至關(guān)重要,但保護(hù)公共建筑和體育場(chǎng)更側(cè)重于檢測(cè)較大的物品,如武器或爆炸物。在這些應(yīng)用中,通常使用較少的通道數(shù)。

這些系統(tǒng)中的另一個(gè)關(guān)鍵組件是快速切換時(shí)間。這使得掃描系統(tǒng)得以實(shí)現(xiàn),其中被掃描者只需在短時(shí)間內(nèi)(通常為一秒或更短)擺姿勢(shì)。下一代演練系統(tǒng)需要更快的切換時(shí)間,以便人不必停下來(lái)擺姿勢(shì)。

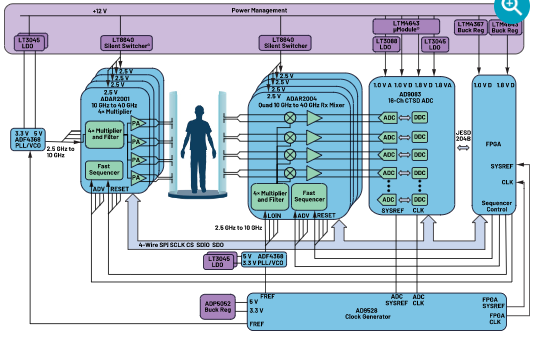

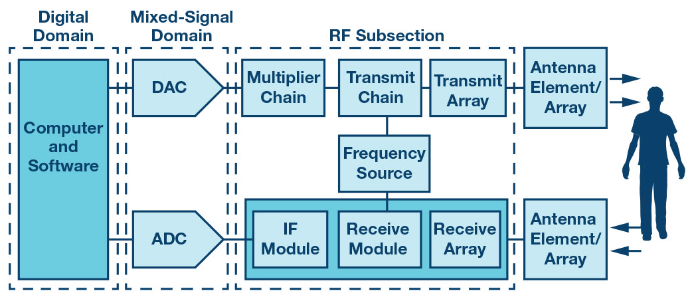

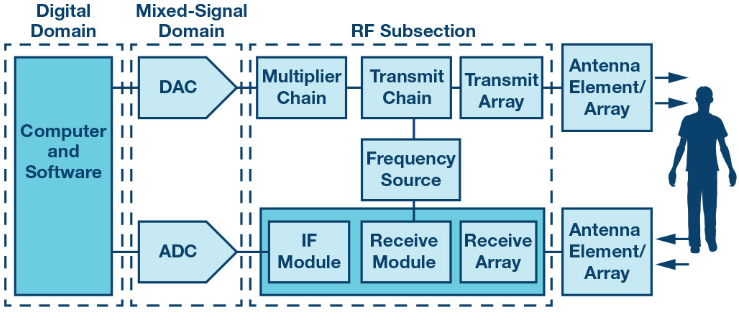

圖2顯示了如何使用ADI公司的毫米波成像芯片組實(shí)現(xiàn)完整的毫米波掃描儀。發(fā)射器陣列(ADAR2001)由中央捷變頻率源驅(qū)動(dòng)。接收器陣列(ADAR2004)檢測(cè)反射信號(hào),并將其下變頻至低中頻,在該頻率下,多通道連續(xù)時(shí)間Σ-Δ(CTSD)轉(zhuǎn)換器(AD9083)對(duì)其進(jìn)行中頻采樣。

現(xiàn)在,我們將仔細(xì)研究這些組件以及它們的功能如何優(yōu)化整體系統(tǒng)性能。

發(fā)射機(jī)

如前所述,發(fā)射器由大量空間分散天線組成,每個(gè)天線由功率放大器驅(qū)動(dòng)。ADAR2001是一款4通道發(fā)射器,直接連接到天線,輸出頻率范圍為10 GHz至40 GHz。由于在大型陣列中分配10 GHz至40 GHz信號(hào)存在困難,ADAR2001集成了4×乘法器。因此,發(fā)射器 IC 前面的所有管道和信號(hào)分配都在 2.5 GHz 至 10 GHz 頻率范圍內(nèi)進(jìn)行。

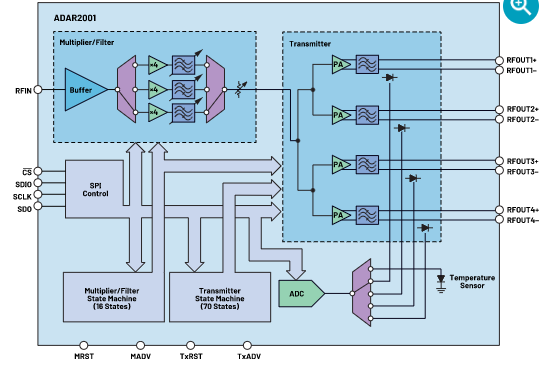

ADAR2001發(fā)射器的主要RF元件包括RF輸入緩沖器、帶集成可切換諧波濾波器的4×倍頻器、1:4信號(hào)分配器和2001個(gè)差分輸出功率放大器,用于驅(qū)動(dòng)偶極子或螺旋天線等差分天線結(jié)構(gòu)。ADAR3的詳細(xì)框圖如圖<>所示。

RFIN 端口施加 2.5 GHz 至 10 GHz 之間的 CW RF 輸入信號(hào),功率電平至少為 –20 dBm。寬帶倍頻器由三個(gè)并聯(lián)子電路組成。每個(gè)子電路(低頻段、中頻段、高頻段)都經(jīng)過(guò)優(yōu)化,可乘以和濾波總頻率范圍的一部分。乘法器塊輸入端和輸出端的開關(guān)用于選擇所需工作頻率的子電路。

乘法器輸出通過(guò)可編程衰減器,然后分成四個(gè)并施加到四個(gè)功率放大器。除了乘法器模塊中的可配置濾波外,每個(gè)PA還包含一個(gè)可以啟用或禁用的低通/陷波濾波器。對(duì)于高達(dá) 20 GHz 的輸出頻率,應(yīng)啟用此濾波器。高于 20 GHz,應(yīng)禁用它。

可編程衰減器用于幫助確保輸出功率與頻率的關(guān)系相對(duì)平坦。該衰減器具有大約15 dB的數(shù)字步進(jìn)衰減范圍。當(dāng)輸出頻率從10 GHz掃描到40 GHz時(shí),應(yīng)減小此衰減,以保持所需的輸出功率平坦度與頻率的關(guān)系。這使得每個(gè)差分PA輸出的標(biāo)稱PA輸出功率為+5 dBm,諧波抑制范圍為–20 dBc至–30 dBc。

要進(jìn)行完整的 10 GHz 至 40 GHz 頻率掃描,必須將乘法器/濾波器模塊設(shè)置調(diào)整七次,以確保最佳的諧波抑制和輸出功率。此外,當(dāng)系統(tǒng)以一個(gè)頻率駐留時(shí),每個(gè)頻率

圖2.完整的毫米波成像系統(tǒng)。

圖3.ADAR2001 10 GHz至40 GHz發(fā)射器。

發(fā)射機(jī)通道必須依次打開和關(guān)閉。為了避免造成SPI命令瓶頸,ADAR2001包括兩個(gè)狀態(tài)機(jī),可以預(yù)編程多達(dá)70種狀態(tài)。一旦器件的RAM被編程,就可以通過(guò)簡(jiǎn)單的脈沖到器件的MADV(前進(jìn))引腳來(lái)實(shí)現(xiàn)狀態(tài)推進(jìn)。這些特性相結(jié)合,可確保2 ns通道切換時(shí)間。在IC之間切換時(shí)也可以實(shí)現(xiàn)此切換時(shí)間(例如,器件A的通道4在器件B的通道1接通時(shí)關(guān)閉)。由于全掃描涉及多個(gè)頻率的全通道掃描,因此切換時(shí)間至關(guān)重要。例如,如果陣列有 500 個(gè)晶片,并且要以 10 MHz 的步長(zhǎng)從 40 GHz 掃描到 50 GHz,則它必須執(zhí)行總共 300,000 個(gè)通道切換才能完成完全掃描。

每個(gè)通道上的RF輸出功率可以使用單獨(dú)的片上RF檢波器進(jìn)行監(jiān)控。芯片溫度也可以通過(guò)片上溫度傳感器監(jiān)控。這些傳感器饋入 5:1 模擬多路復(fù)用器,該多路復(fù)用器將所需信號(hào)傳遞到片內(nèi) 8 位 ADC。

ADF4368 PLL/VCO為發(fā)射器網(wǎng)絡(luò)提供激勵(lì)。其輸出信號(hào)將根據(jù)發(fā)射通道的數(shù)量多次分離。ADF4368的輸出功率相對(duì)較高(+9 dBm)和ADAR2001的最小輸入閾值(–20 dBm)確保ADF4368的輸出在需要放大器緩沖之前可以多次無(wú)源分離。

接收器

來(lái)自傳輸?shù)姆瓷浔唤邮掌魇叭。邮掌魇嵌嗤ǖ阑祛l器和ADC陣列。ADAR2004是一款四通道混頻器和ADC驅(qū)動(dòng)器,內(nèi)置數(shù)字編程增益放大器(DGA)。LO輸入也具有一個(gè)內(nèi)部4×乘法器,由第二個(gè)PLL驅(qū)動(dòng),其輸出頻率與射頻偏移,因此混頻器產(chǎn)生真正的IF輸出。然后,混頻器的IF輸出由AD9083采樣,AD16是一款集成數(shù)字下變頻的<>通道連續(xù)時(shí)間Σ-Δ型ADC。選擇中頻采樣架構(gòu)而不是零中頻架構(gòu),以避免接收器中LO泄漏引起的直流偏移,以及LO正交分路器中不完美的正交平衡引起的I/Q誤差。雖然這些缺陷可以通過(guò)校準(zhǔn)來(lái)緩解,但每個(gè)輸入頻率都需要校準(zhǔn),因?yàn)長(zhǎng)O泄漏和正交誤差往往隨頻率變化。

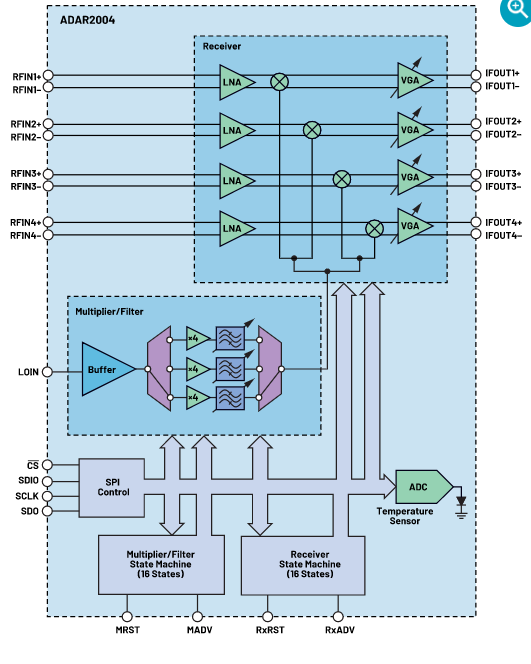

圖4所示為四通道混頻器ADAR2004的框圖。LO輸入由2.5 GHz至10 GHz正弦波驅(qū)動(dòng),在乘法器輸出端產(chǎn)生10 GHz至40 GHz的正弦波。乘法器輸出饋送到四個(gè)混頻器,這些混頻器的IF輸出具有可編程增益。與ADAR2001發(fā)射器一樣,ADAR2004接收器也具有兩個(gè)可預(yù)編程的片內(nèi)狀態(tài)機(jī)。

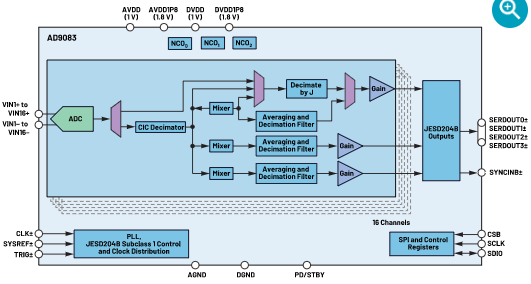

圖5所示為9083通道CTSD ADC AD16的框圖。ADC輸入設(shè)計(jì)為具有與ADAR2004的IF輸出相同的共模電壓。這允許混頻器輸出和ADC輸入直接連接。由于沒有交流耦合電容,可確保當(dāng)混頻器輸出突然切換時(shí)(例如,在混頻器輸入端的頻率階躍期間),不會(huì)出現(xiàn)充電/放電瞬變。

使用集成單極點(diǎn)濾波器的一階CTSD ADC架構(gòu),最大限度地減少外部濾波,從而節(jié)省PCB空間。與奈奎斯特速率轉(zhuǎn)換器的建立時(shí)間相比,該架構(gòu)還具有較快的信號(hào)建立時(shí)間,奈奎斯特速率轉(zhuǎn)換器需要高選擇性抗混疊濾波器來(lái)消除噪聲折疊。快速建立時(shí)間是本應(yīng)用的關(guān)鍵要求,因?yàn)锳DC建立時(shí)間必須能夠跟上發(fā)射側(cè)的快速通道開關(guān)。

圖4.ADAR2004 10 GHz至40 GHz接收器框圖。

每個(gè)ADC都有一個(gè)信號(hào)處理模塊,用于濾除來(lái)自Σ-Δ ADC的帶外整形噪聲并降低采樣速率。每個(gè)模塊包含一個(gè)級(jí)聯(lián)積分梳(CIC)濾波器、一個(gè)具有多個(gè)有限輸入響應(yīng)(FIR)抽取濾波器(由J塊抽取)的正交數(shù)字下變頻器(DDC),或多達(dá)三個(gè)帶平均抽取濾波器的正交DDC通道,用于數(shù)據(jù)門控應(yīng)用。三個(gè)正交DDC通道的存在可以同時(shí)解調(diào)多達(dá)三個(gè)頻率。稍后我們將看到如何使用它來(lái)顯著加快掃描時(shí)間。

系統(tǒng)設(shè)置和操作

ADAR2001和ADAR2004專為在大型陣列中高效工作而設(shè)計(jì)。特別強(qiáng)調(diào)減少布線開銷。ADAR2001和ADAR2004的RFIN和LO輸入端口可在低至–20 dBm的輸入電平下工作。由于需要從公共LO源(本例中為ADF4368)驅(qū)動(dòng)這些輸入,因此這種低輸入靈敏度允許在需要放大之前進(jìn)行大量無(wú)源扇出。例如,假設(shè)威爾金森功率分配器的凈損耗為1 dB,則ADF4368的9 dBm輸出功率可以無(wú)源扇出128次,可以驅(qū)動(dòng)512個(gè)器件(<>個(gè)通道)。

驅(qū)動(dòng)ADAR2001和ADAR2004片內(nèi)時(shí)序控制器的進(jìn)階和復(fù)位引腳也設(shè)計(jì)為并行驅(qū)動(dòng),以最大限度地減少處理器或FPGA必須提供的GPIO數(shù)量。通過(guò)在時(shí)序控制器中提供足夠的深度和復(fù)雜性,可以使用一組前進(jìn)和復(fù)位脈沖驅(qū)動(dòng)多達(dá)16個(gè)ADAR2001器件。

在工作之前,必須對(duì)ADAR2001和ADAR2004的時(shí)序控制器進(jìn)行編程。雖然可以使用SPI命令訪問(wèn)兩個(gè)設(shè)備的所有功能,但相關(guān)的延遲將導(dǎo)致不可接受的總掃描時(shí)間。

讓我們考慮如何為基于通道的掃描設(shè)置一個(gè) 64 通道系統(tǒng)(64 發(fā)射器、64 接收器),也就是說(shuō),我們?cè)谠黾宇l率并重復(fù)掃描之前以單個(gè)頻率循環(huán)遍歷所有傳輸通道。

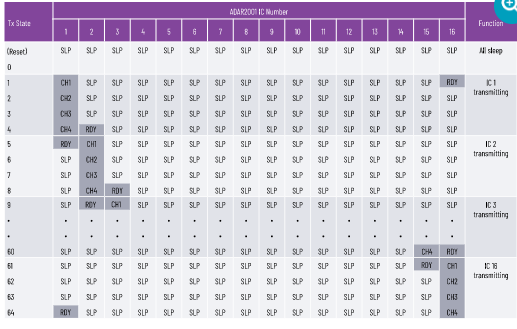

圖6顯示了如何對(duì)16個(gè)ADAR2001器件中的狀態(tài)機(jī)進(jìn)行編程以啟用此掃描。該架構(gòu)的一個(gè)關(guān)鍵目標(biāo)是能夠?qū)墓部刂凭€執(zhí)行不同操作的多個(gè)設(shè)備進(jìn)行排序。

請(qǐng)注意,在圖6中,雖然每個(gè)IC有65種狀態(tài),但大多數(shù)IC大部分時(shí)間都設(shè)置為休眠模式(SLP)。例如,IC 1僅在前四種狀態(tài)下完全處于活動(dòng)狀態(tài),因?yàn)樵揑C的通道1、2、3和4按順序傳輸。在這四種狀態(tài)下,所有其他IC都處于SLP或就緒(RDY)模式。

圖5.AD9083原理框圖

同樣,IC 2僅在狀態(tài)5至8期間完全激活,因?yàn)樗衅渌鸌C都處于SLP或RDY模式。通過(guò)以這種方式配置16個(gè)狀態(tài)機(jī),它們的導(dǎo)通周期彼此偏移,可以用并行脈沖驅(qū)動(dòng)所有16個(gè)器件的前進(jìn)和復(fù)位線路。

RDY模式是開發(fā)用于優(yōu)化開關(guān)時(shí)間同時(shí)節(jié)省功耗的中間狀態(tài)。由于大多數(shù)發(fā)射器大部分時(shí)間處于非活動(dòng)狀態(tài),因此SLP模式是降低功耗的關(guān)鍵。但是,從系統(tǒng)角度來(lái)看,從SLP模式切換到傳輸模式(50 ns)所需的時(shí)間過(guò)長(zhǎng),會(huì)導(dǎo)致掃描期間出現(xiàn)延遲。RDY模式是一種中間狀態(tài),可以在IC準(zhǔn)備傳輸時(shí)調(diào)用。請(qǐng)注意,在圖7中,在狀態(tài)4中,IC 4的通道1正在傳輸,而IC 2通過(guò)將IC 4置于RDY模式來(lái)準(zhǔn)備傳輸。在從發(fā)射器狀態(tài) 5 過(guò)渡到 1 的過(guò)程中,IC 2 從發(fā)射模式轉(zhuǎn)換到 RDY 模式,IC 10 從 RDY 模式轉(zhuǎn)換到發(fā)射模式。此轉(zhuǎn)換需要 1 ns。隨后的片內(nèi)通道開關(guān)(即,從IC2上的通道3到通道4到通道2到通道2)的切換時(shí)間為1024 ns。對(duì)于以 10.40 GHz 步長(zhǎng)從 0 GHz 掃描到 1 GHz 的 20 元素陣列,完整的掃描時(shí)間將小于 50 毫秒。這假設(shè)PLL鎖定時(shí)間為5 μs。如果使用兩個(gè)以乒乓模式運(yùn)行的PLL來(lái)實(shí)現(xiàn)更快的頻率建立,則掃描時(shí)間將遠(yuǎn)低于<> ms。

圖6.對(duì)16個(gè)ADAR2001發(fā)送器進(jìn)行編程,用于由單個(gè)提前脈沖驅(qū)動(dòng)的通道掃描。

ADAR2004接收器的操作和時(shí)序不太復(fù)雜,因?yàn)橥ǔ5淖龇ㄊ菍⑺薪邮掌魍ǖ琅渲脼槭冀K接收。狀態(tài)機(jī)仍必須排序,以便在接收器與發(fā)射器一起掃描時(shí)選擇正確的乘法器路徑和濾波器設(shè)置。

如前所述,每個(gè)AD9083 ADC通道最多可以訪問(wèn)三個(gè)正交DDC通道。這意味著它可以同時(shí)解調(diào)三個(gè)頻率,假設(shè)所有三個(gè)頻率都在ADC模擬輸入帶寬(125 MHz)的輸入頻率范圍內(nèi)。例如,通過(guò)將三個(gè)IF音調(diào)定位在50 MHz、75 MHz和100 MHz,可以將這三個(gè)音調(diào)同時(shí)解調(diào)為I和Q基帶數(shù)據(jù)。

為了在發(fā)射端促進(jìn)這種方法,必須使用三個(gè)發(fā)射PLL,而不是一個(gè)。三個(gè)發(fā)射頻率必須始終指向不同的物理發(fā)射IC(ADAR2001中的乘法器不能傳導(dǎo)多音信號(hào))。這三個(gè)頻率必須始終不同,但在掃描時(shí)必須保持彼此接近的頻率。例如,如果其中一個(gè)ADAR2001器件上的一個(gè)通道以10 GHz的頻率傳輸,則另外兩個(gè)器件將以10.025 GHz和10.050 GHz的頻率發(fā)射,以支持50 MHz、75 MHz和100 MHz的IF輸出。此方案在傳輸路徑中需要更多的硬件和交換基礎(chǔ)設(shè)施,但具有將整體掃描時(shí)間減少 3 倍的好處。

結(jié)論

該芯片組由四通道發(fā)送器ADAR2001、四通道接收器ADAR2004、9083通道ADCAD16和PLL/VCOADF4368組成,具有實(shí)現(xiàn)下一代漫游毫米波安全掃描器所需的高集成度和功能。集成狀態(tài)機(jī)和片上數(shù)字下變頻可顯著卸載傳統(tǒng)的集中式處理,并將其轉(zhuǎn)移到智能邊緣。最終結(jié)果是,中央處理器在掃描期間不必?fù)?dān)心控制系統(tǒng),并且它接收的數(shù)據(jù)已經(jīng)被解調(diào)和抽取。雖然該芯片組專為毫米波安全成像應(yīng)用而開發(fā),但ADAR2001發(fā)射器和ADAR2004接收器的寬頻率范圍以及AD9083 16通道ADC的集成度,使該芯片組適用于需要高通道密度和快速開關(guān)的其他應(yīng)用。

審核編輯:郭婷

-

芯片

+關(guān)注

關(guān)注

459文章

52425瀏覽量

439663 -

接收器

+關(guān)注

關(guān)注

15文章

2568瀏覽量

73779 -

毫米波

+關(guān)注

關(guān)注

21文章

1970瀏覽量

65946

發(fā)布評(píng)論請(qǐng)先 登錄

恩智浦與吉利汽車開展合作,定義下一代毫米波雷達(dá)

毫米波雷達(dá)(一)

毫米波傳感器如何實(shí)現(xiàn)邊緣智能

毫米波傳感器是如何實(shí)現(xiàn)邊緣智能的?

毫米波技術(shù)基礎(chǔ)

毫米波技術(shù)如何為自主機(jī)器人提供邊緣智能

毫米波傳感器實(shí)現(xiàn)邊緣智能的方法

實(shí)現(xiàn)下一代高密度電源轉(zhuǎn)換

實(shí)現(xiàn)下一代高密度電源轉(zhuǎn)換

毫米波人體掃描儀市場(chǎng) 過(guò)去和現(xiàn)在以及未來(lái)

毫米波人體掃描儀市場(chǎng):過(guò)去、現(xiàn)在和未來(lái)

毫米波人體掃描儀市場(chǎng): 過(guò)去、現(xiàn)在和未來(lái)

毫米波人體掃描儀市場(chǎng):過(guò)去、現(xiàn)在和未來(lái)

評(píng)論