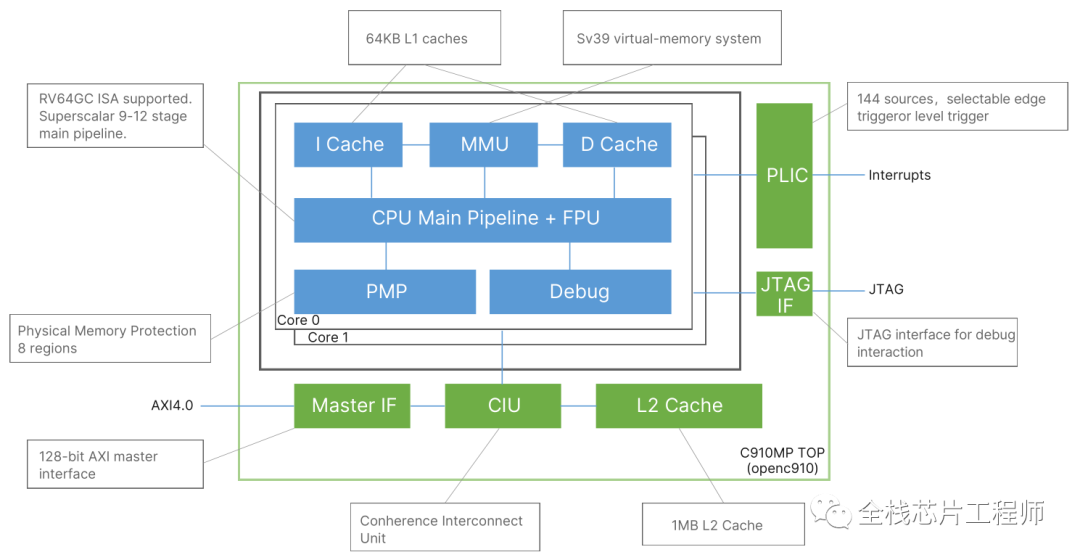

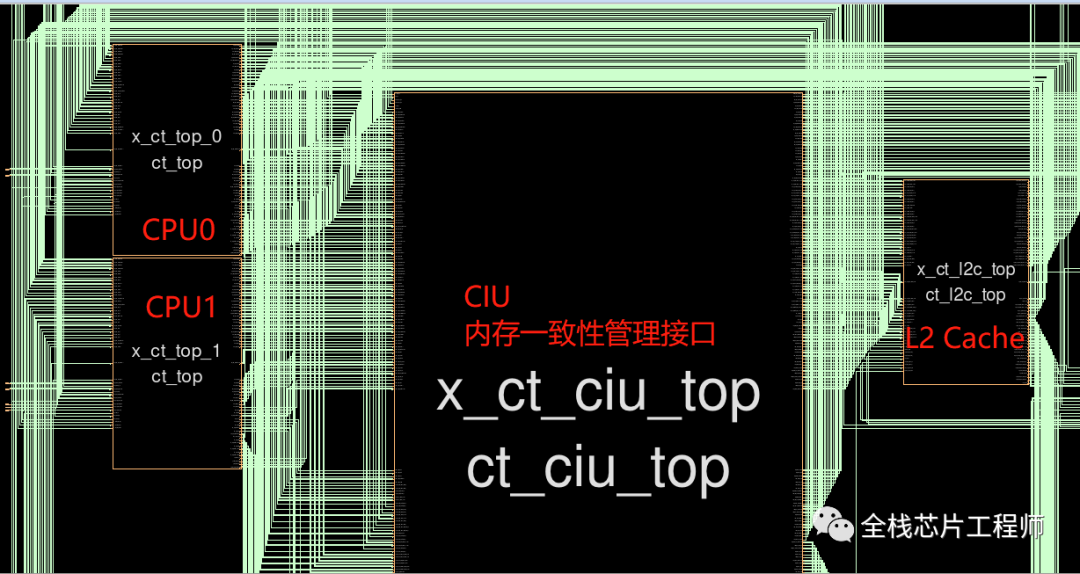

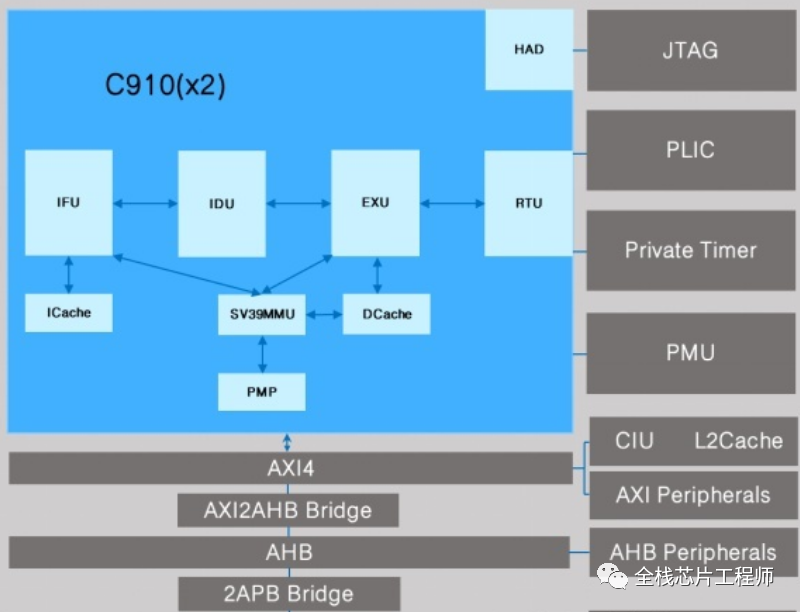

玄鐵C910處理器是同構多核架構,支持雙核;(開源版本為雙核,預留四核接口),主要特征有:

? 支持各個核心獨立下電以及cluster下電;

? 支持1 個AXI4.0 Master 接口,128比特的總線寬度;

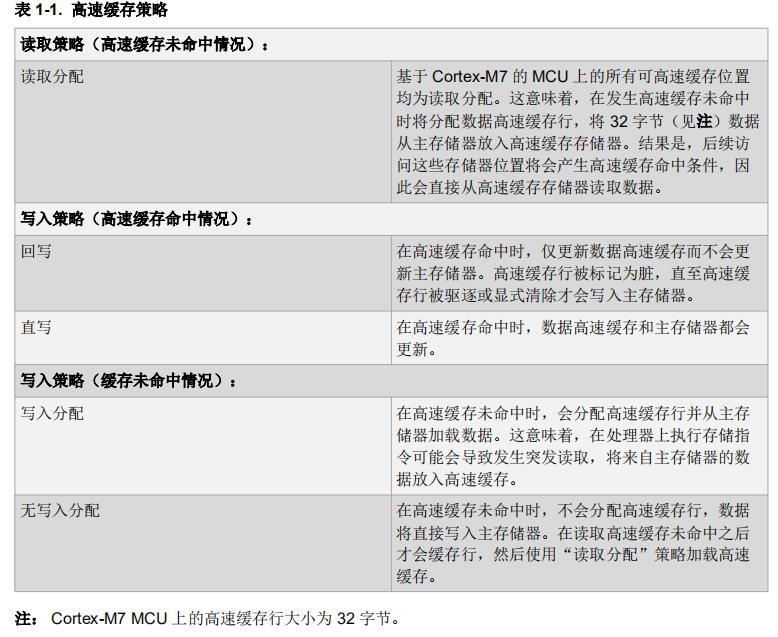

? 兩級cache結構,哈佛結構L1cache(Icache、Dcache)和共享的L2cache;

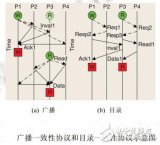

? L1cache支持MESI 的一致性協議,L2cache支持MOESI 的一致性協議;

? 支持RISC-V私有中斷控制器CLINT 和平臺級中斷控制器PLIC;

? 支持自定義且接口兼容RISC-V 的多核調試框架;

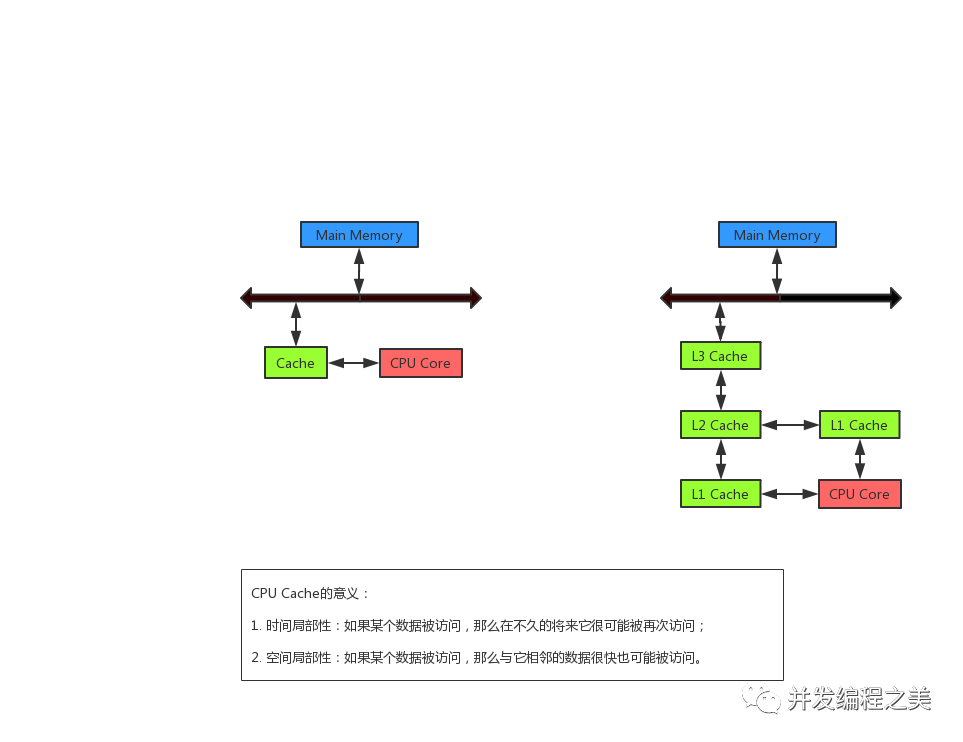

C910MP 二級高速緩存采用 MOESI 協議維護多個處理器核心數據高速緩存的一致性。MOESI 代表了每個緩存行在數據高速緩存上的 5 個狀態,分別是:

? M:表示緩存行僅位于此數據高速緩存中,且被寫臟;(UniqueDirty)

? O:表示緩存行可能位于多個數據高速緩存中,且被寫臟;(ShareDirty)

? E:表示緩存行僅位于此數據高速緩存中,且是干凈的;(UniqueClean)

? S:表示緩存行可能位于多個數據高速緩存中,且是干凈的;(ShareClean)

? I:表示緩存行不在該數據高速緩存中。(Invalid)

那么MESI是什么原理?硬件如何維護多核CPU的數據一致性?答案參見知識星球討論。

-

處理器

+關注

關注

68文章

19819瀏覽量

233678 -

控制器

+關注

關注

114文章

16993瀏覽量

183077 -

cpu

+關注

關注

68文章

11045瀏覽量

216093 -

接口

+關注

關注

33文章

8959瀏覽量

153250 -

soc

+關注

關注

38文章

4354瀏覽量

221800

原文標題:多核CPU的SoC緩存一致性設計概述

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

介紹ARM存儲一致性模型的相關知識

如何解決數據庫與緩存一致性

一致性規劃研究

加速器一致性接口

Cache一致性協議優化研究

自主駕駛系統將使用緩存一致性互連IP和非一致性互連IP

搞定緩存一致性驗證,多核SoC設計就成功了一半

本周五|搞定緩存一致性驗證,多核SoC設計就成功了一半

Redis緩存與Mysql如何保證一致性?

評論