在上一篇文章中(FPGA 的數(shù)字信號(hào)處理:Verilog 實(shí)現(xiàn)簡(jiǎn)單的 FIR 濾波器)演示了在 Verilog 中編寫(xiě)自定義 FIR 模塊的初始demo。該項(xiàng)目在行為仿真中正常,但在布局和布線時(shí)未能滿足時(shí)序要求。

所以今天的文章讓我們來(lái)看看當(dāng)設(shè)計(jì)不能滿足時(shí)序要求時(shí)如何分析并解決它。

當(dāng)在目標(biāo) FPGA 芯片中布局和布線時(shí),首先在 Vivado 中確定時(shí)序要求.

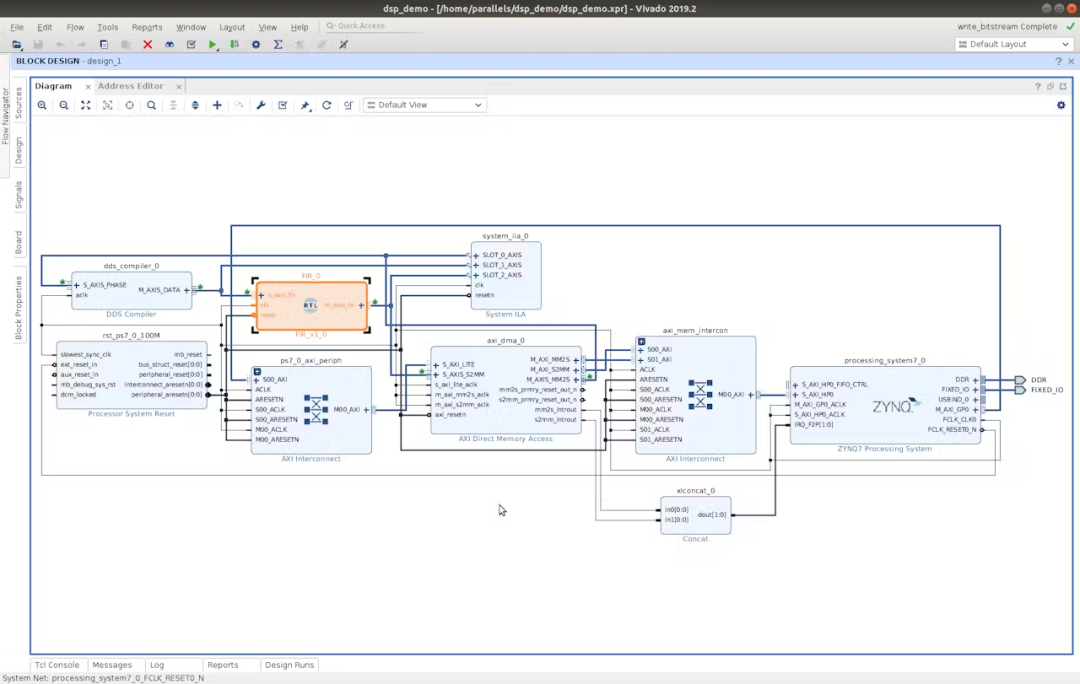

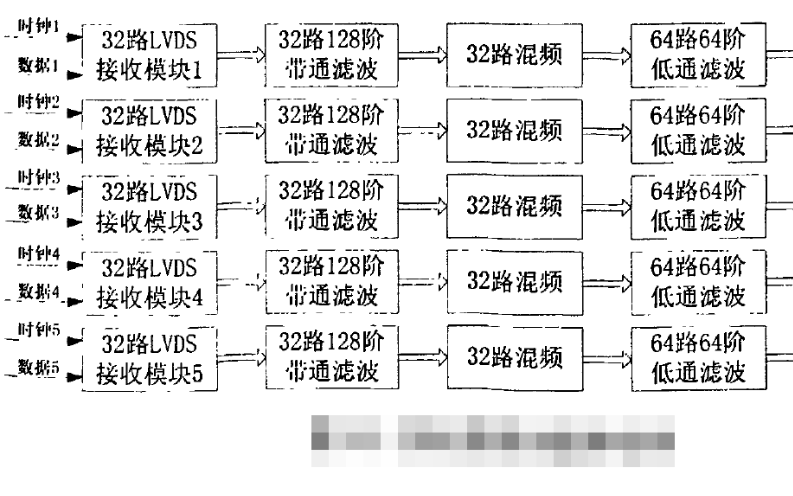

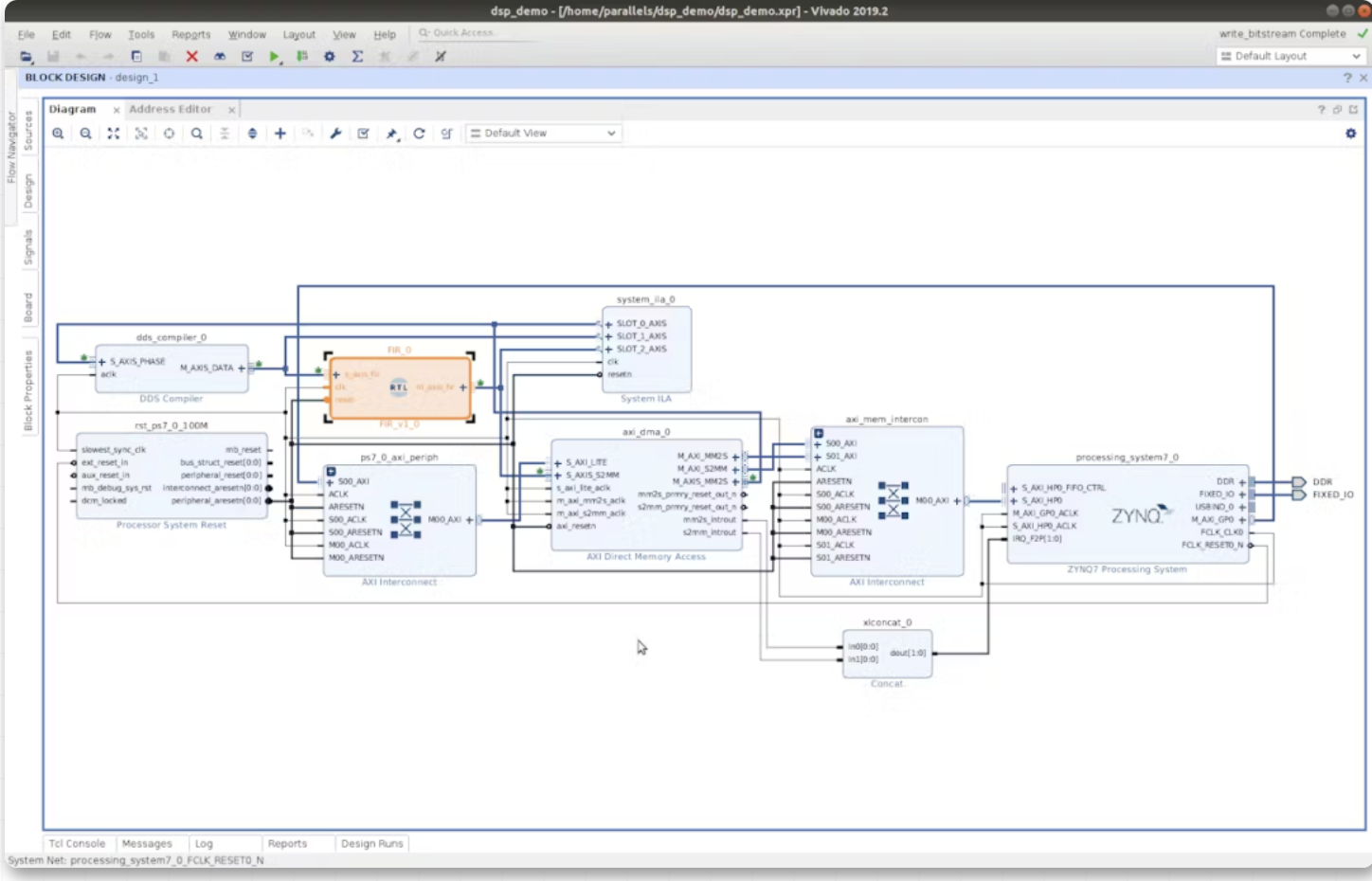

將 FIR 作為RTL 模塊導(dǎo)入到block design中,其中通過(guò)AXI DMA 從存儲(chǔ)器傳輸相位增量偏移值的DDS可以輸入可變頻率正弦曲線,這樣就可以演示FIR的行為。

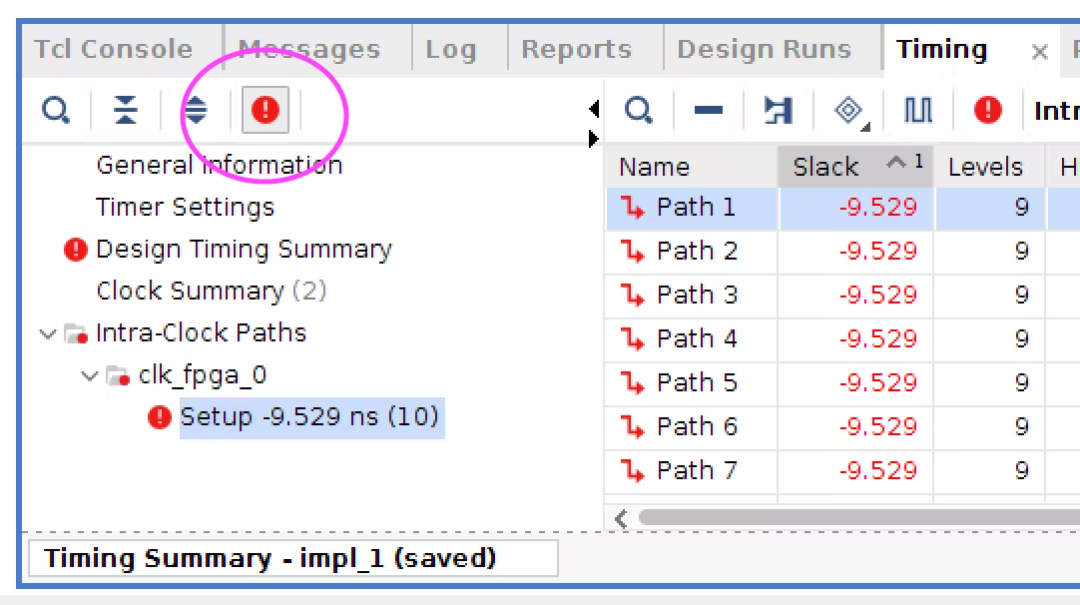

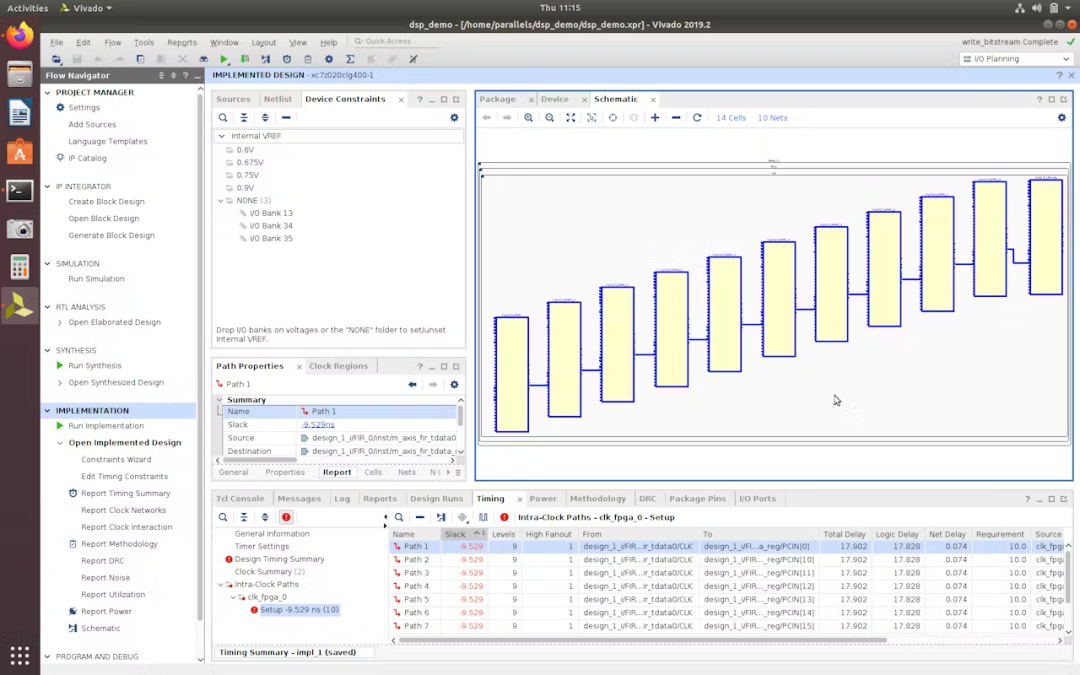

在 Vivado 中綜合布局布線并打開(kāi)設(shè)計(jì)后,會(huì)彈出嚴(yán)重警告,告知設(shè)計(jì)不符合時(shí)序要求。

為了能夠準(zhǔn)確查看設(shè)計(jì)時(shí)序失敗的原因,在已完成綜合設(shè)計(jì)的底部窗口包含一個(gè)選項(xiàng)卡,用于 Vivado 在綜合期間對(duì)設(shè)計(jì)執(zhí)行的時(shí)序分析。當(dāng)存在時(shí)序失敗的信號(hào)路徑時(shí),用戶可以過(guò)濾此時(shí)序分析以僅使用下圖中顯示的紅色圓圈感嘆號(hào)查看這些違規(guī)路徑:

在這個(gè)特定的設(shè)計(jì)中,有幾個(gè)信號(hào)路徑未能達(dá)到其分配的時(shí)序,這意味著信號(hào)的物理距離太遠(yuǎn)而無(wú)法穿過(guò)芯片和/或在信號(hào)出去之前需要通過(guò)太多的邏輯級(jí)別。保持時(shí)間太長(zhǎng)的信號(hào)意味著當(dāng)將其計(jì)時(shí)到下一級(jí)寄存器中時(shí),不能依賴它的值是否有效,從而使其余下游邏輯的行為不可靠/不可預(yù)測(cè)。

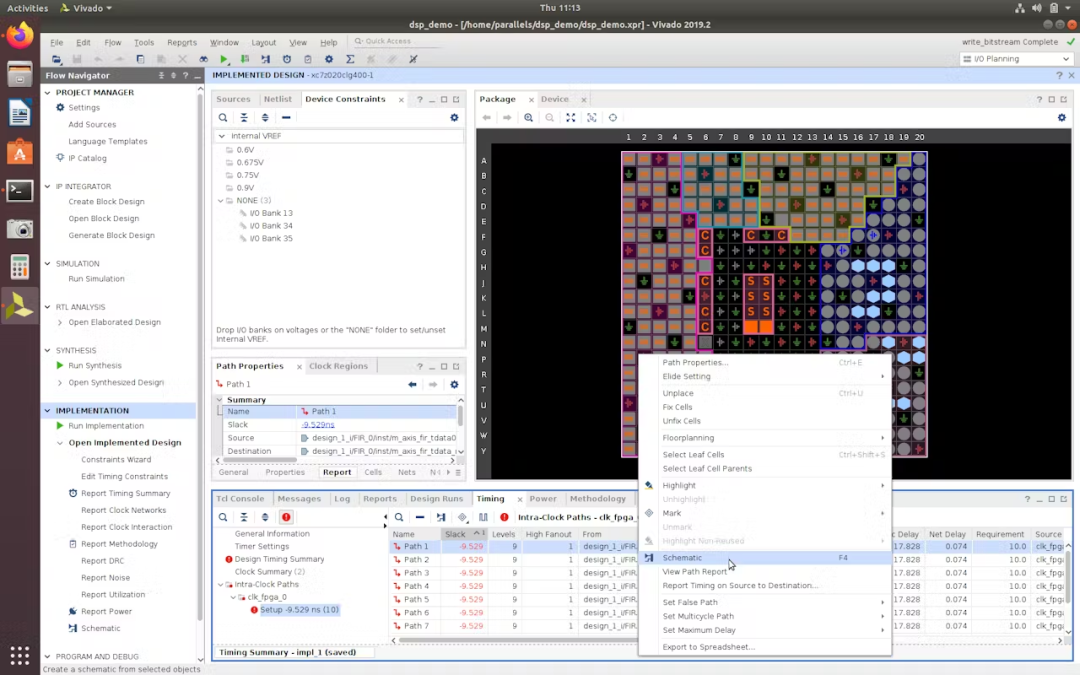

s_axis_fir_tdata在這種情況下,進(jìn)入 FIR 模塊的 AXI Stream 輸入接口的數(shù)據(jù)信號(hào)需要很長(zhǎng)時(shí)間才能到達(dá)m_axis_fir_tdata目標(biāo)寄存器處的輸出。要查看比屏幕底部的時(shí)序分析窗口中的內(nèi)容更多的詳細(xì)信息,右鍵單擊底部時(shí)序分析窗口中的違規(guī)信號(hào)路徑,然后選擇“查看路徑報(bào)告(View Path Report)”選項(xiàng)。然后,將能夠看到 Vivado 如何計(jì)算出該信號(hào)的允許建立時(shí)間,并與它實(shí)際給出的 HDL 設(shè)計(jì)編寫(xiě)方式進(jìn)行比較。這會(huì)給一些提示,說(shuō)明是什么導(dǎo)致建立時(shí)間延長(zhǎng)。然而,我發(fā)現(xiàn)要真正可視化保持時(shí)序違規(guī)比在示意圖中查看信號(hào)會(huì)更直觀。

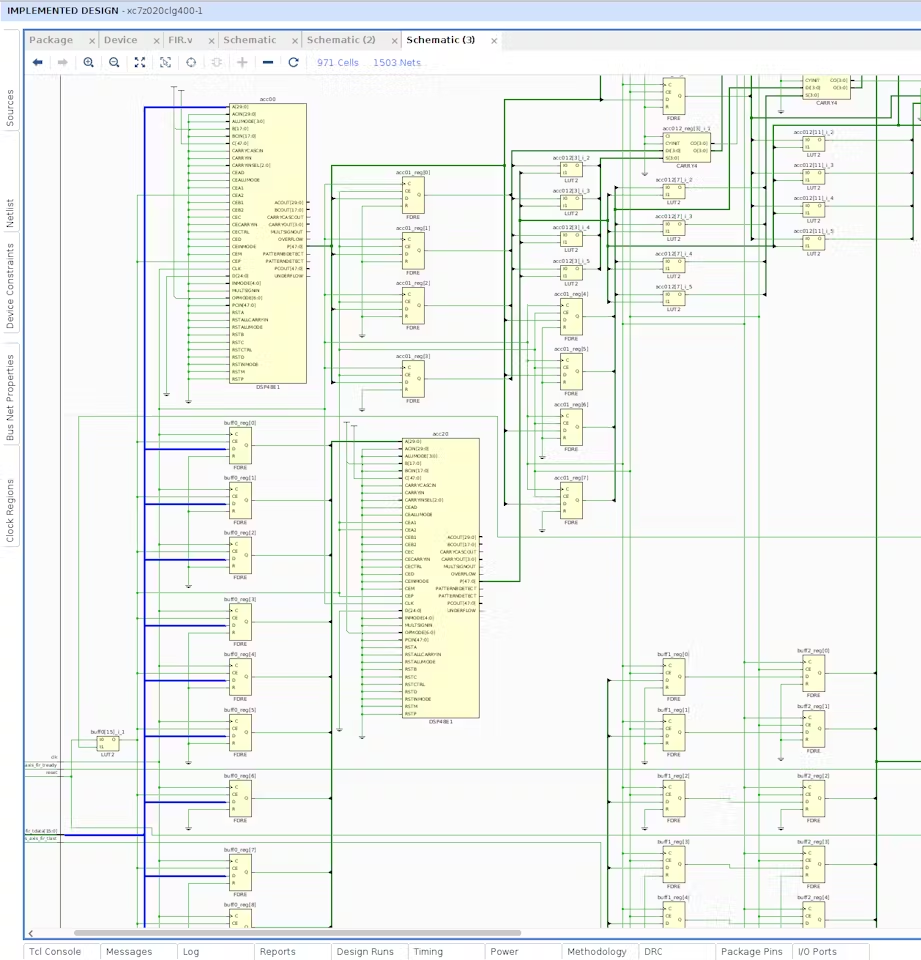

要在原理圖中打開(kāi)特定信號(hào)路徑,再次右鍵單擊底部時(shí)序分析窗口中的違規(guī)信號(hào)路徑,然后選擇“Schematic”選項(xiàng)。將打開(kāi)一個(gè)新選項(xiàng)卡,顯示信號(hào)路徑在設(shè)計(jì)的物理布局中經(jīng)過(guò)的邏輯。

在為axis_fir_tdata的數(shù)據(jù)總線中的一個(gè)位打開(kāi)信號(hào)路徑時(shí),它揭示了設(shè)計(jì)在芯片中的布線,從圖中可以看出信號(hào)必須通過(guò) 11 級(jí)邏輯串行后才能到達(dá)其目的地。

既然對(duì)已實(shí)施設(shè)計(jì)的分析已經(jīng)揭示了哪些信號(hào)路徑是哪個(gè)時(shí)序違規(guī)的問(wèn)題,現(xiàn)在的問(wèn)題是我們?nèi)绾谓鉀Q它?在這種情況下,很明顯需要重新設(shè)計(jì)當(dāng)前邏輯,以更并行的方式處理更小的數(shù)據(jù)塊,從而縮短數(shù)據(jù)到其目標(biāo)寄存器的總路徑。

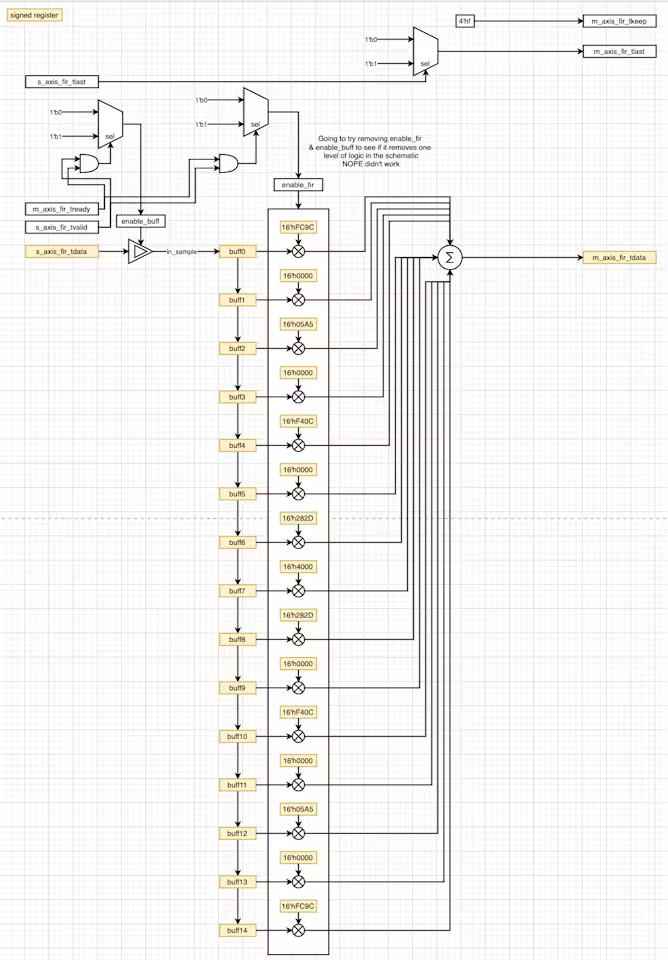

個(gè)人更喜歡在嘗試編寫(xiě)任何實(shí)際的 Verilog 代碼之前繪制出邏輯。當(dāng)有這種設(shè)計(jì)執(zhí)行的操作的可視化表示時(shí),調(diào)試設(shè)計(jì)會(huì)容易得多,特別是對(duì)于跟蹤此類時(shí)序違規(guī)等問(wèn)題。

檢查當(dāng)前 FIR 模塊的邏輯設(shè)計(jì),其中數(shù)據(jù)總線違反了建立時(shí)序,很明顯循環(huán)緩沖區(qū)串行填充然后將所有 15 個(gè)數(shù)據(jù)發(fā)送到累加塊時(shí),立即求和會(huì)產(chǎn)生大量的處理延遲。

核心的想法是嘗試填充循環(huán)緩沖區(qū),將每個(gè)緩沖區(qū)乘以適當(dāng)?shù)南禂?shù),最后一次性對(duì) 15 個(gè)算子的每一個(gè)求和,但是這次我們考慮重新設(shè)計(jì)邏輯,讓循環(huán)緩沖區(qū)中僅花費(fèi)乘法和累加(求和)兩個(gè)寄存器一個(gè)級(jí)聯(lián)的時(shí)間。

新 FIR 模塊的 Verilog 代碼:

`timescale1ns/1ps moduleFIR( inputclk, inputreset, inputsigned[15:0]s_axis_fir_tdata, input[3:0]s_axis_fir_tkeep, inputs_axis_fir_tlast, inputs_axis_fir_tvalid, inputm_axis_fir_tready, outputregm_axis_fir_tvalid, outputregs_axis_fir_tready, outputregm_axis_fir_tlast, outputreg[3:0]m_axis_fir_tkeep, outputregsigned[31:0]m_axis_fir_tdata ); /*ThisloopcontrolstkeepsignalonAXIStreaminterface*/ always@(posedgeclk) begin m_axis_fir_tkeep<=?4'hf; ????????end ???????? ????/*?This?loop?controls?tlast?signal?on?AXI?Stream?interface?*/ ????always?@?(posedge?clk) ????????begin ????????????if?(s_axis_fir_tlast?==?1'b1) ????????????????begin ????????????????????m_axis_fir_tlast?<=?1'b1; ????????????????end ????????????else ????????????????begin ????????????????????m_axis_fir_tlast?<=?1'b0; ????????????????end ????????end ???? ????//?15-tap?FIR? ????reg?enable_fir; ????reg?signed?[15:0]?buff0,?buff1,?buff2,?buff3,?buff4,?buff5,?buff6,?buff7,?buff8,?buff9,?buff10,?buff11,?buff12,?buff13,?buff14; ????wire?signed?[15:0]?tap0,?tap1,?tap2,?tap3,?tap4,?tap5,?tap6,?tap7,?tap8,?tap9,?tap10,?tap11,?tap12,?tap13,?tap14;? ????reg?signed?[31:0]?acc0,?acc1,?acc2,?acc3,?acc4,?acc5,?acc6,?acc7,?acc8,?acc9,?acc10,?acc11,?acc12,?acc13,?acc14;? ???? ????/*?Taps?for?LPF?running?@?1MSps?*/ ????assign?tap0?=?16'hFC9C;??//?twos(-0.0265?*?32768)?=?0xFC9C ????assign?tap1?=?16'h0000;??//?0 ????assign?tap2?=?16'h05A5;??//?0.0441?*?32768?=?1445.0688?=?1445?=?0x05A5 ????assign?tap3?=?16'h0000;??//?0 ????assign?tap4?=?16'hF40C;??//?twos(-0.0934?*?32768)?=?0xF40C ????assign?tap5?=?16'h0000;??//?0 ????assign?tap6?=?16'h282D;??//?0.3139?*?32768?=?10285.8752?=?10285?=?0x282D ????assign?tap7?=?16'h4000;??//?0.5000?*?32768?=?16384?=?0x4000 ????assign?tap8?=?16'h282D;??//?0.3139?*?32768?=?10285.8752?=?10285?=?0x282D ????assign?tap9?=?16'h0000;??//?0 ????assign?tap10?=?16'hF40C;?//?twos(-0.0934?*?32768)?=?0xF40C ????assign?tap11?=?16'h0000;?//?0 ????assign?tap12?=?16'h05A5;?//?0.0441?*?32768?=?1445.0688?=?1445?=?0x05A5 ????assign?tap13?=?16'h0000;?//?0 ????assign?tap14?=?16'hFC9C;?//?twos(-0.0265?*?32768)?=?0xFC9C ???? ????/*?This?loop?controls?tready?&?tvalid?signals?on?AXI?Stream?interface?*/ ????always?@?(posedge?clk) ????????begin ????????????if(reset?==?1'b0?||?m_axis_fir_tready?==?1'b0?||?s_axis_fir_tvalid?==?1'b0) ????????????????begin ????????????????????enable_fir?<=?1'b0; ????????????????????s_axis_fir_tready?<=?1'b0; ????????????????????m_axis_fir_tvalid?<=?1'b0; ????????????????end ????????????else ????????????????begin ????????????????????enable_fir?<=?1'b1; ????????????????????s_axis_fir_tready?<=?1'b1; ????????????????????m_axis_fir_tvalid?<=?1'b1; ????????????????end ????????end ???? ????reg?[3:0]?cnt; ????reg?signed?[31:0]?acc01,?acc012,?acc23,?acc34,?acc45,?acc56,?acc67,?acc78,?acc89,?acc910,?acc1011,?acc1112,?acc1213; ???? ????/*?Circular?buffer?w/?Multiply?&?Accumulate?stages?of?FIR?*/ ????always?@?(posedge?clk?or?posedge?reset) ????????begin ????????????if?(reset?==?1'b0) ????????????????begin ????????????????????m_axis_fir_tdata?<=?32'd0; ????????????????end ????????????else?if?(enable_fir?==?1'b1) ????????????????begin ????????????????????buff0?<=?s_axis_fir_tdata; ????????????????????acc0?<=?tap0?*?buff0; ???????????????????? ????????????????????buff1?<=?buff0;? ????????????????????acc1?<=?tap1?*?buff1;?? ????????????????????acc01?<=?acc0?+?acc1; ????????????????????????? ????????????????????buff2?<=?buff1;? ????????????????????acc2?<=?tap2?*?buff2; ????????????????????acc012?<=?acc01?+?acc2; ???????????????????????????? ????????????????????buff3?<=?buff2;? ????????????????????acc3?<=?tap3?*?buff3; ????????????????????acc23?<=?acc012?+?acc3; ????????????????????????? ????????????????????buff4?<=?buff3;? ????????????????????acc4?<=?tap4?*?buff4; ????????????????????acc34?<=?acc23?+?acc4; ????????????????????????? ????????????????????buff5?<=?buff4; ????????????????????acc5?<=?tap5?*?buff5;? ????????????????????acc45?<=?acc34?+?acc5; ?????????????????????????? ????????????????????buff6?<=?buff5;? ????????????????????acc6?<=?tap6?*?buff6; ????????????????????acc56?<=?acc45?+?acc6; ??????????????????????? ????????????????????buff7?<=?buff6;? ????????????????????acc7?<=?tap7?*?buff7; ????????????????????acc67?<=?acc56?+?acc7; ?????????????????????????? ????????????????????buff8?<=?buff7; ????????????????????acc8?<=?tap8?*?buff8; ????????????????????acc78?<=?acc67?+?acc8; ??????????????????????????? ????????????????????buff9?<=?buff8;? ????????????????????acc9?<=?tap9?*?buff9; ????????????????????acc89?<=?acc78?+?acc9; ?????????????????????????? ????????????????????buff10?<=?buff9;? ????????????????????acc10?<=?tap10?*?buff10; ????????????????????acc910?<=?acc89?+?acc10; ??????????????????????????? ????????????????????buff11?<=?buff10;? ????????????????????acc11?<=?tap11?*?buff11; ????????????????????acc1011?<=?acc910?+?acc11; ?????????????????????????? ????????????????????buff12?<=?buff11;? ????????????????????acc12?<=?tap12?*?buff12; ????????????????????acc1112?<=?acc1011?+?acc12; ?????????????????????????? ????????????????????buff13?<=?buff12;? ????????????????????acc13?<=?tap13?*?buff13; ????????????????????acc1213?<=?acc1112?+?acc13; ?????????????????????????? ????????????????????buff14?<=?buff13;? ????????????????????acc14?<=?tap14?*?buff14; ????????????????????m_axis_fir_tdata?<=?acc1213?+?acc14; ???????????????????? ????????????????end ????????end ???? endmodule

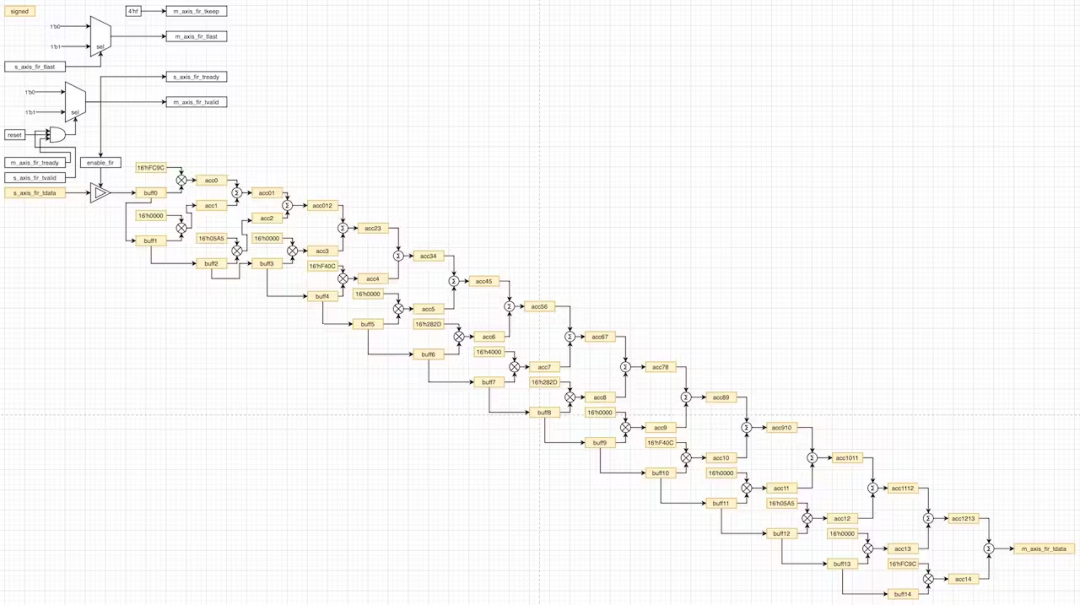

使用新 FIR 模塊的 Verilog 代碼重新運(yùn)行綜合布局布線后就可以產(chǎn)生滿足所有時(shí)序要求的設(shè)計(jì)。打開(kāi)之前違反建立時(shí)序的相同數(shù)據(jù)信號(hào)路徑的原理圖,可以直觀地證明信號(hào)路徑是如何整體縮短的。

新原理圖顯示axis_fir_tdata總線中每個(gè)位的信號(hào)路徑都被并行處理,有效地縮短了它們到達(dá)目標(biāo)寄存器的時(shí)間,這就是減少信號(hào)建立時(shí)間的原因。

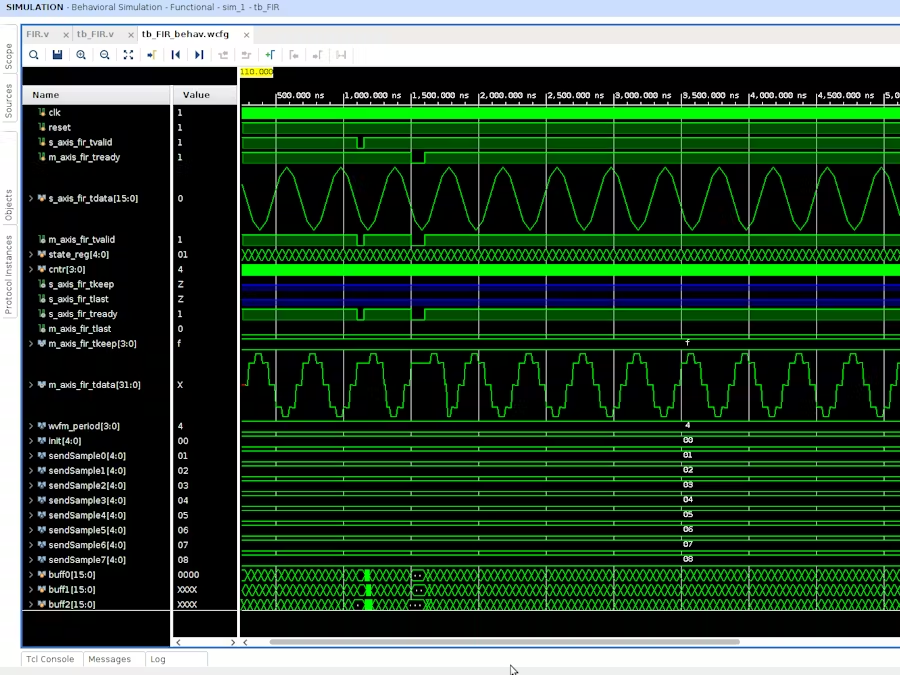

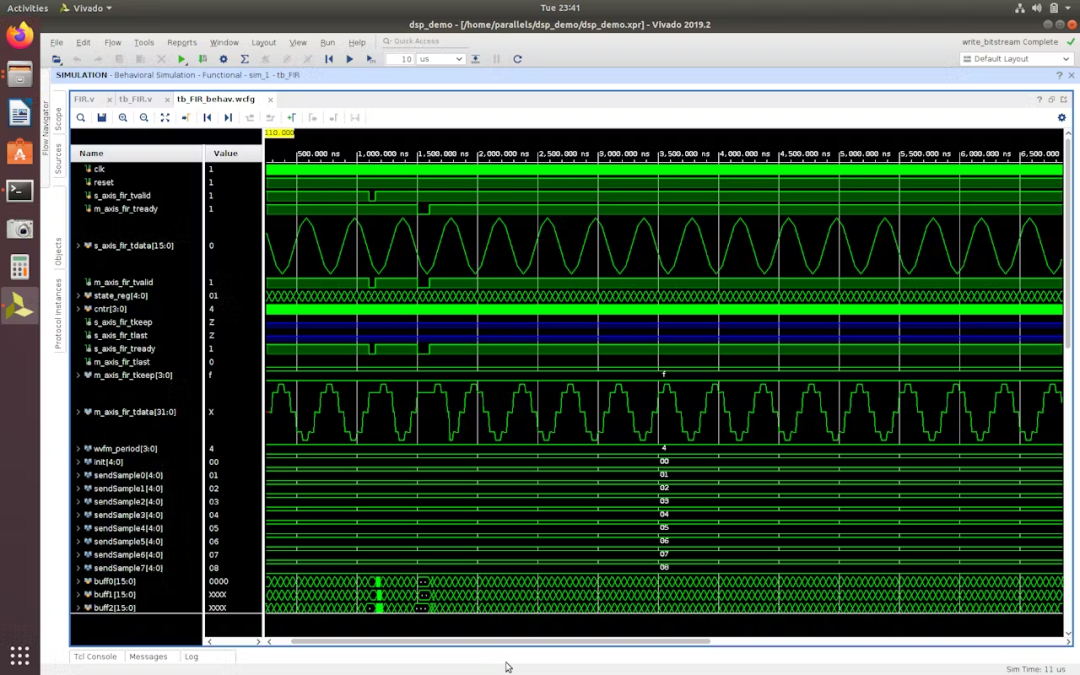

當(dāng)新設(shè)計(jì)滿足時(shí)序要求時(shí),接下來(lái)就是驗(yàn)證重寫(xiě)后的邏輯是否仍然與舊邏輯一樣。重新運(yùn)行行為仿真將很快回答這個(gè)問(wèn)題。

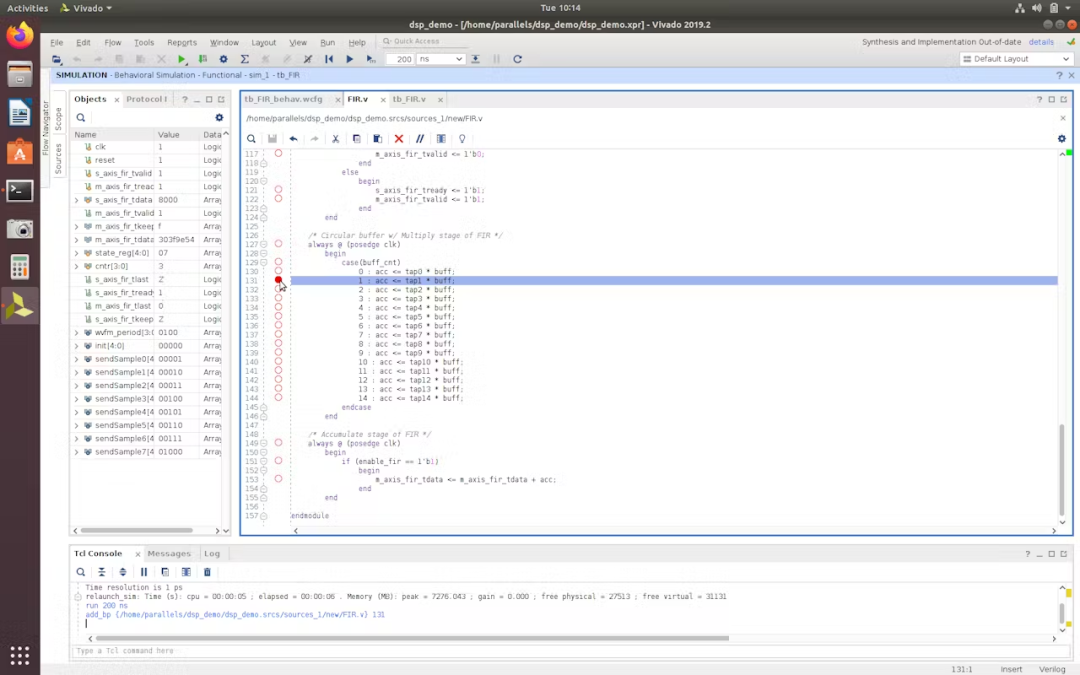

由于希望用新代碼替換之前的邏輯,發(fā)現(xiàn)設(shè)置斷點(diǎn)并在更新波形圖時(shí)單步執(zhí)行 Verilog 的每一行的功能可以實(shí)現(xiàn)我們的目的。

啟動(dòng)行為仿真后,會(huì)注意到 HDL 的每條有效行的行號(hào)右側(cè)都有一個(gè)紅色圓圈。單擊這些紅色圓圈之一將啟用該行上的斷點(diǎn)。

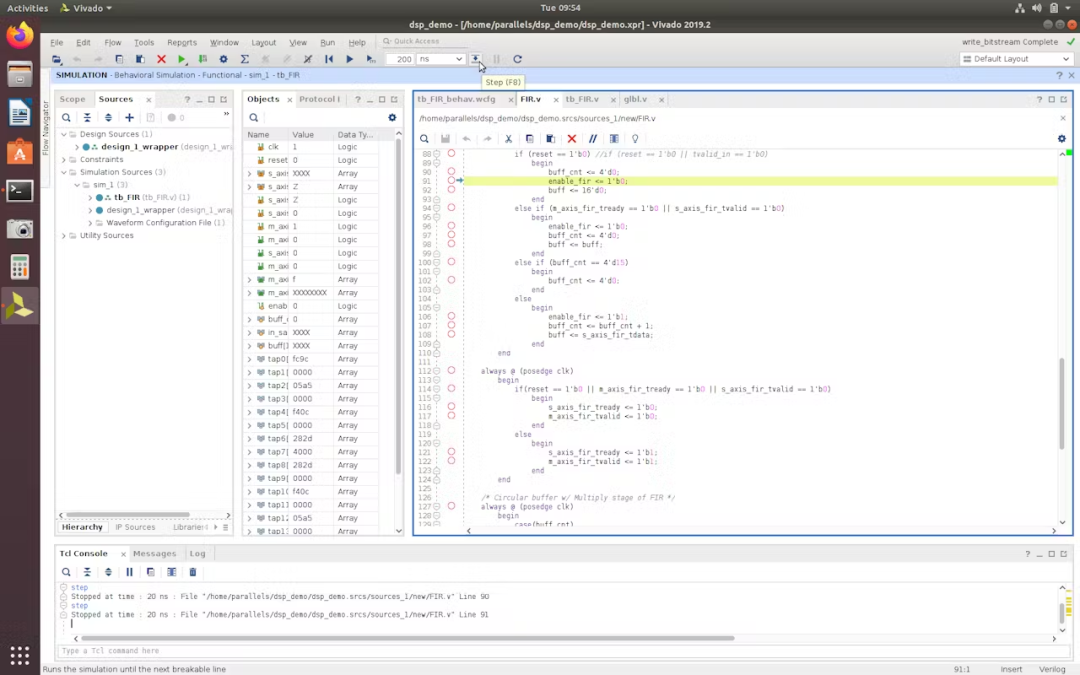

當(dāng)仿真運(yùn)行并遇到該斷點(diǎn)時(shí),可以使用頂部工具欄中的“步進(jìn)”按鈕(如下所示)或 F8 來(lái)逐步執(zhí)行剩余的代碼行。

最后,我們看到 FIR 濾波器的新邏輯設(shè)計(jì)確實(shí)按預(yù)期運(yùn)行!

總結(jié)

上面的兩個(gè)例子能證明在目標(biāo) FPGA 芯片上,最終輸出相同結(jié)果的兩種不同的 HDL 編寫(xiě)方式對(duì)時(shí)序影響不同的重要性。這就是為什么在編寫(xiě)代碼腦中“有電路”是很重要的原因。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603018 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7484瀏覽量

163767 -

數(shù)字信號(hào)處理

+關(guān)注

關(guān)注

15文章

560瀏覽量

45845 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110077 -

時(shí)序

+關(guān)注

關(guān)注

5文章

387瀏覽量

37318

原文標(biāo)題:FPGA 的數(shù)字信號(hào)處理:重寫(xiě) FIR 邏輯以滿足時(shí)序要求

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【參考書(shū)籍】基于FPGA的數(shù)字信號(hào)處理——高亞軍著

利用FPGA怎么實(shí)現(xiàn)數(shù)字信號(hào)處理?

如何設(shè)計(jì)一個(gè)脈動(dòng)陣列結(jié)構(gòu)的FIR濾波器?

數(shù)字信號(hào)處理的FPGA實(shí)現(xiàn)

數(shù)字信號(hào)處理的FPGA實(shí)現(xiàn)_劉凌譯

FPGA在數(shù)字信號(hào)處理中的簡(jiǎn)單應(yīng)用

基于FPGA數(shù)字信號(hào)處理

數(shù)字信號(hào)處理的FPGA實(shí)現(xiàn)

基于FPGA的數(shù)字信號(hào)處理算法研究與高效實(shí)現(xiàn)

如何使用FPGA實(shí)現(xiàn)數(shù)字信號(hào)處理算法的研究

數(shù)字信號(hào)處理的FPGA實(shí)現(xiàn).第3版英文

FPGA的數(shù)字信號(hào)處理:重寫(xiě)FIR邏輯以滿足時(shí)序要求

FPGA的數(shù)字信號(hào)處理:重寫(xiě)FIR邏輯以滿足時(shí)序要求

FPGA的數(shù)字信號(hào)處理:重寫(xiě)FIR邏輯以滿足時(shí)序要求

評(píng)論