概述

Verilog 是一種用于數字邏輯電路設計的硬件描述語言,可以用來進行數字電路的仿真驗證、時序分析、邏輯綜合。

既是一種行為級(可用于電路的功能描述)描述語言又是一種結構性(可用于元器件及其之間的連接)描述語言

Verilog模塊基本概念

模塊是Verilog的基本單位,除了編譯指令,其他的所有的設計代碼都必須放在一個或多個模塊中

一個模塊內部可以使用其他模塊,稱為實例。上層模塊可以引用底層任意層次模塊的變量

模塊內部可以包含若干個“塊”

Verilog模塊總結

· Verilog中的標示符可以是任意一組字母、數字、$符號和下劃線符號的組合,但標示符的第一個字符必須是字母或者下劃線。標示符區分大小寫。

· Verilog程序是有模塊組成的,每個模塊嵌套在module和endmodule聲明語句中。模塊是可以進行層次嵌套的

· 每個Verilog源文件中只準有一個頂層模塊,其他為子模塊

· 每個模塊要進行端口定義,并說明輸入輸出端口,然后對模塊的功能進行行為邏輯描述

· 程序書寫格式自由,一行可以寫幾個語句,一個語句可以分幾行寫

· 除了endmodule語句,begin...end語句,fork...join語句外,每個語句和數據定義的最后必須有分號

· 可用/*...*/和//...對程序的任何部分做注釋,加上必要的注釋,以增強程序的可度性和可維護性。

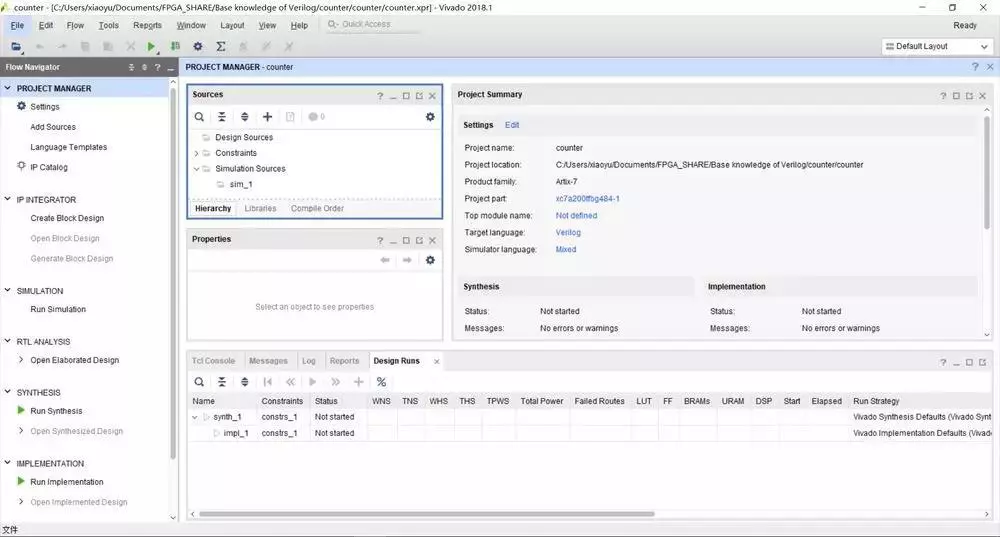

Verilog用于模塊的測試

檢查程序的功能是否正確要求:

· 需要有測試激勵信號輸入到被測模塊

· 需要記錄被測模塊的輸出信號

· 需要把用功能和行為描述的Verilog模塊轉換為門級電路互連的電路結構(綜合)

· 需要對已經轉換為門級電路結構的邏輯進行測試(門級電路仿真)

· 需要對布局布線后的電路結構進行測試(布局布線后仿真)

何為仿真?為何要仿真?

仿真是對電路模塊進行動態的全面測試,通過觀測被測試模塊的輸出信號是否符合要求可以調試和驗證邏輯系統的設計和結構是否準確,并發現問題及時修改。

仿真可以在幾個層面上進行?每個層面的仿真有什么意義?

仿真有:前(RTL)仿真,邏輯網表仿真,門級仿真和布線后仿真;

前仿真:前(RTL)仿真,邏輯網表仿真,門級仿真;可以調試和驗證邏輯系統的設計和結構準確與否,并發現問題及時修改。

布線后仿真:分析設計模塊運行是否正常;

模塊的結構

Verilog 的基本設計單元是"模塊(block)"

verilog 模塊的結構由在module和endmodule關鍵字之間的4個主要部分組成:

module block1(a,b,c,d); //端口定義 input a,b,c; output d; //I/O聲明 wirex;//信號類型聲明 assign d = a | x; assign x = (b &~c); //功能描述 endmodule

邏輯功能的定義

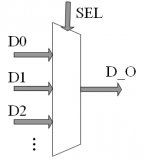

在Verilog中有3種方法可以描述電路的邏輯功能:

1. 用assign語句(連續賦值語句,常用于描述組合邏輯)

assign x = (b &~c);

2.用元件例化(instance 門元件例化)

and(門元件關鍵字) u_and3(例化原件名)(f,a,b,c);

注1:元件例化即是調用Verilog提供的元件;

注2:元件例化包括門元件例化和模塊元件例化;

注3:每個實例元件的名字必須唯一,以避免與其他調用元件的實例相混淆;

注4:例化元件名也可以省略。

3.用”always“塊語句

always @(posedge clk) //當時鐘上升沿到來時執行一遍塊內語句 begin if(load) out = data; //同步預置數據 else out = data + cin +1; //加1計數 end

注1:”always“塊語句常用于描述時序邏輯,也可描述組合邏輯;

注2:”always“塊可用多種手段來表達邏輯關系,如用if...else語句或case語句;

注3:”always“塊語句與assign語句是并發執行的,assign語句一定要放在”always“塊語句之外。

模塊結構模板:

module <頂層模塊名> (<輸入輸出端口列表>); output 輸出端口列表; input 輸入端口列表; //更推薦 module <頂層模塊名> ( output 輸出端口列表, input 輸入端口列表 ); //1.使用assign語句定義邏輯功能 wire 結果信號名; assign <結果信號名> =表達式; //2.使用always塊定義邏輯功能 always@(<敏感信號表達式>) begin //過程賦值語句 //if語句 //case語句 //while,repeat,for循環 //task,function調用 end //3.文件例化( );//模塊元件例化 ( );//門元件例化 endmodule

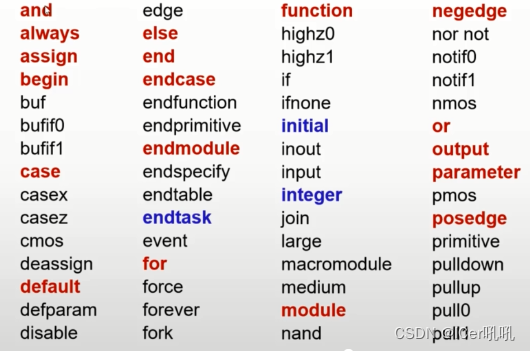

關鍵字

標示符

任何用Verilog語言描述的東西都可以通過其名字來識別,這個名字被稱為標示符;

如源文件名,模塊名,端口名,變量名,常量名,實例名等

標示符可由字母,數字,$和下劃線組成,但第一個字符必須是字母或下劃線,不能是$和數字

在Verilog中標示符是區分大小寫的,且不能與關鍵字同名。

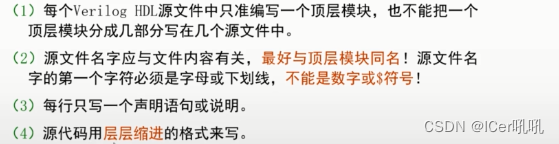

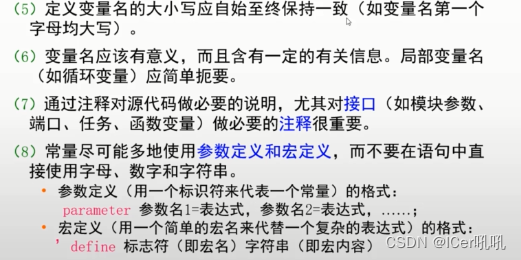

語匯代碼編寫標準

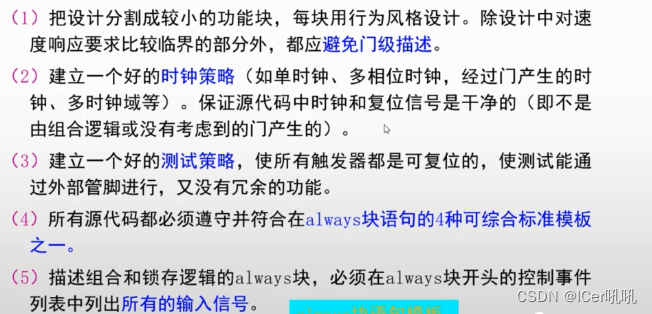

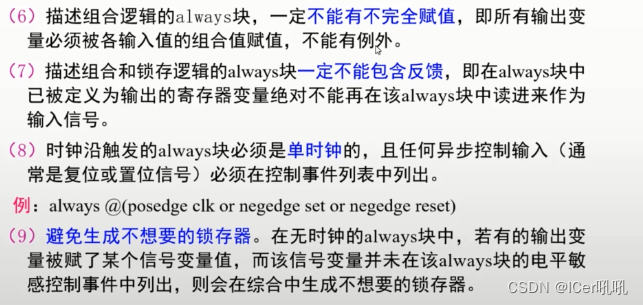

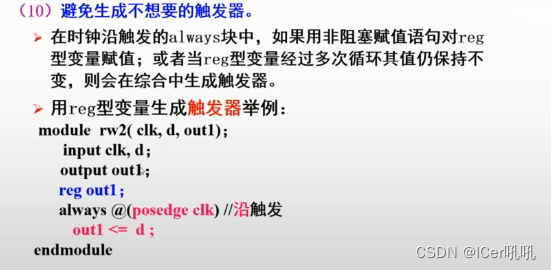

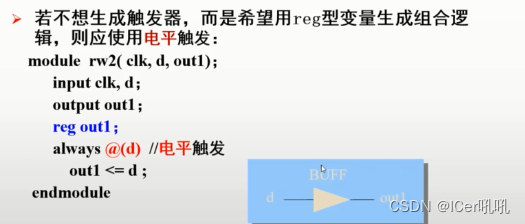

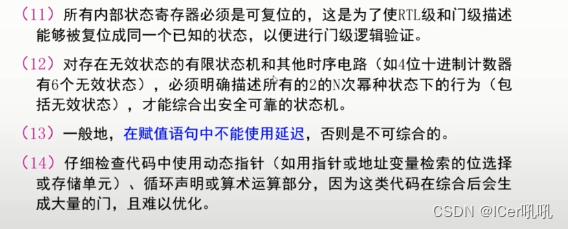

綜合代碼編寫標準

-

邏輯電路

+關注

關注

13文章

494瀏覽量

42610 -

電路設計

+關注

關注

6673文章

2451瀏覽量

204168 -

Verilog

+關注

關注

28文章

1351瀏覽量

110077 -

時序分析

+關注

關注

2文章

127瀏覽量

22565 -

數字邏輯電路

+關注

關注

0文章

106瀏覽量

15812

原文標題:IC學霸筆記 | Verilog基本語法概述

文章出處:【微信號:IC修真院,微信公眾號:IC修真院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Verilog_HDL的基本語法詳解(夏宇聞版)

Verilog語法基礎

通過實例設計來加深Verilog描述語法理解

Verilog基本語法概述

Verilog基本語法概述

評論