1 引言

我們在學習STM32的時候,把被控單元的 FLASH,RAM,FSMC和AHB 到 APB 的橋(即片上外設),這些功能部件共同排列在一個 4GB 的地址空間內。我們在編程的時候,可以通過他們的地址找到他們,然后來操作他們(通過 C 語言對它們進行數據的讀和寫)。它的地址是由芯片廠商或用戶分配,給__存儲器__分配地址的過程就稱為__存儲器映射。 我們可以根據每個單元功能的不同,以功能為名給這個內存單元取一個別名,這個別名就是我們經常說的__寄存器 。給已經分配好地址的特定功能的__內存單元取別名__的過程就叫__寄存器映射__。

然而筆者這里要講的寄存器和我們操作STM32的寄存器不是一個東西,這里是CPU中的寄存器,它是一個存儲器,其作用是進行數據的__臨時存儲__。為了進一步說明,筆者把CPU的寄存器叫做__內部寄存器__。首先我們來回顧下ARM架構CPU的內部結構。

控制單元是整個CPU的指揮控制中心 ,由程序計數器PC(Program Counter),指令寄存器IR (Instruction Register)、指令譯碼器ID(Instruction Decoder)和操作控制器OC(Operation Controller)等,對協調整個電腦有序工作極為重要。它根據用戶預先編好的程序,依次從存儲器中取出各條指令,放在指令寄存器IR中,通過指令譯碼(分析)確定應該進行什么操作,然后通過操作控制器OC,按確定的時序,向相應的部件發出微操作控制信號。操作控制器OC中主要包括節拍脈沖發生器、控制矩陣、時鐘脈沖發生器、復位電路和啟停電路等控制邏輯。

運算單元可以執行算術運算(包括加減乘數等基本運算及其附加運算)和邏輯運算(包括移位、邏輯測試或兩個值比較) 。相對控制單元而言,運算器接受控制單元的命令而進行動作,即運算單元所進行的全部操作都是由控制單元發出的控制信號來指揮的,所以它是執行部件。

存儲單元包括CPU片內緩存和寄存器組 ,本文要將的內部寄存器也就是這里的寄存器組。是CPU中暫時存放數據的地方,里面保存著那些等待處理的數據,或已經處理過的數據,CPU訪問寄存器所用的時間要比訪問內存的時間短。采用寄存器,可以減少CPU訪問內存的次數,從而提高了CPU的工作速度。但因為受到芯片面積和集成度所限,寄存器組的容量不可能很大。寄存器組可分為專用寄存器和通用寄存器。專用寄存器的作用是固定的,分別寄存相應的數據。而通用寄存器用途廣泛并可由程序員規定其用途,通用寄存器的數目因微處理器而異。

總的來說,CPU從內存中一條一條地取出指令和相應的數據,按指令操作碼的規定,對數據進行運算處理,直到程序執行完畢為止。而指令又是開發者設計好的, 開發者可以通過改變內部寄存器的內容來實現對CPU的控制 。

CPU的內部寄存器是一個存儲單元,它在CPU內部。為了進一步說明它的重要性,那就請看下圖。

為什么會出現多級緩存呢?最主要的原因就是CPU 的頻率太快了,而若是沒有緩存,直接讀取內存中的數據又太慢了,我們不想讓 CPU 停下來等待,所以加入了一層讀取速度大于內存但小于 CPU 的這么一層東西,不同性能的CPU的緩存層數有一般不同。同樣內存寄存器的存在也是為了提高CPU的利用率,它的讀寫速度比緩存又要快一個等級,從而節省讀取操作數所需占用總線和訪問存儲器的時間。

好了,接下里正式講解ARM的內部寄存器。

2 ARM內部寄存器

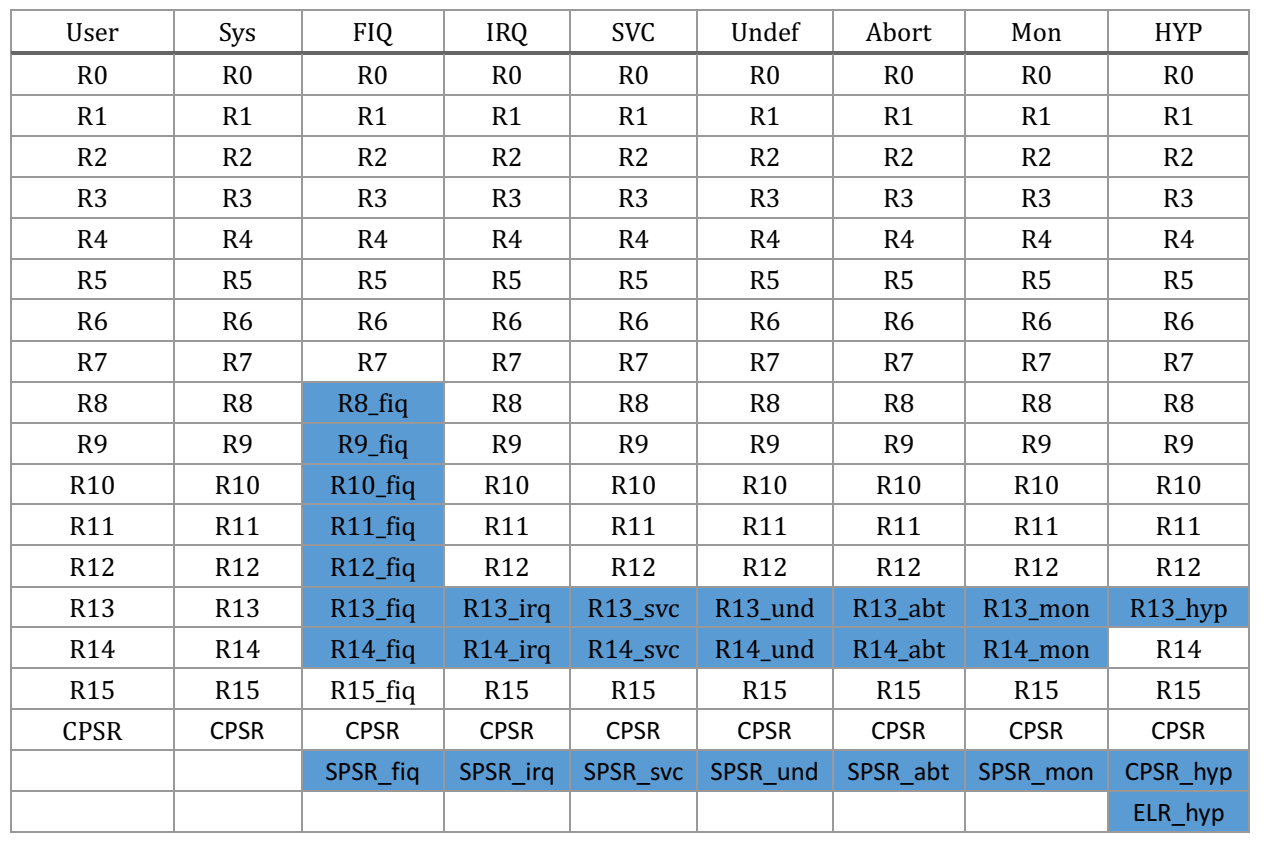

ARM 體系架構的處理器提供了 16 個 32 位的通用寄存器(R0R15),如下圖所示。前15個(R0R14)可以用作通用的數據存儲, R15 是程序計數器 PC,用來保存將要執行的指令。 ARM 還提供了一個當前程序狀態寄存器 CPSR 和一個備份程序狀態寄存器 SPSR,SPSR 寄存器就是 CPSR 寄存器的備份。

R0 - R12:通用寄存器。當C和匯編互相調用時,R0 - R3用來傳遞函數參數。

R13:SP(Stack Pointer),用于各種模式下的堆棧寄存器。

R14:LR(Link Register),用來保存程序返回地址的鏈接寄存器。

R15:PC(Program Counter),程序計數器,表示當前指令地址,寫入新值即可跳轉。

CPSR:(Current Program Status Register),保存程序狀態,比如上一條指令的執行結果,也有控制作用,比如屏蔽中斷等。

值得注意的是,絕大部分的16位thumb只能訪問R0到R7,而32位thumb-2可以訪問全部寄存器。

ARM 處理器有 7 中常見的運行模式:__ User(用戶模式)、 FIQ(快中斷模式)、 IRQ(中斷模式)、 SVC(管理模式)、 Abort(終止模式)、 Undef(未定義模式)和 Sys(系統模式)__。其中 User 是非特權模式,其余 6 中都是特權模式。但新的 Cortex-A 架構加入了TrustZone 安全擴展,所以就新加了一種運行模式:Monitor(安全模式),新的處理器架構還支持虛擬化擴展,因此又加入了另一個運行模式: Hyp(虛擬化模式),所以 Cortex-A7 處理器有9 種處理模式(上電后默認進入SVC模式)。

除了 User(USR)用戶模式以外,其它 8 種運行模式都是特權模式。這幾個運行模式可以通過軟件進行任意切換,也可以通過中斷或者異常來進行切換。大多數的程序都運行在用戶模式,用戶模式下是不能訪問系統所有資源的,有些資源是受限的,要想訪問這些受限的資源就必須進行模式切換。但是用戶模式是不能直接進行切換的,用戶模式下需要借助異常來完成模式切換,當要切換模式的時候,應用程序可以產生異常,在異常的處理過程中完成處理器模式切換。

當中斷或者異常發生以后,處理器就會進入到相應的異常模式種,每一種模式都有一組寄存器供異常處理程序使用,這樣的目的是為了保證在進入異常模式以后,用戶模式下的寄存器不會被破壞。

值得注意的是,一般Cortex-A系列的處理器都有常見的7中模式,而Cortex-M只有兩種運行模式, 特權模式和非特權模式 ,但是 Cortex-A 就有 9 種運行模式。

在不同的工作模式和處理器狀態下,程序員可以訪問的寄存器也不盡相同。每一種運行模式都有一組與之對應的寄存器組。每一種模式可見的寄存器包括 15 個通用寄存器(R0~R14)、一兩個程序狀態寄存器和一個程序計數器 PC。在這些寄存器中,有些是所有模式所共用的同一個物理寄存器,有一些是各模式自己所獨立擁有的,各個模式所擁有的寄存器如下表。

藍色背景的是各個模式所獨有的寄存器,其他寄存器都是和User 模式所共用的。除了User和System模式外,各種模式都有自己獨立的R13和R14,當然HYP除外。在所有的模式中,低寄存器組(R0~R7)是共享同一組物理寄存器的,只是一些高寄存器組在不同的模式有自己獨有的寄存器。

2.1 程序狀態寄存器

所有的處理器模式都共用一個 CPSR 物理寄存器,因此 CPSR 可以在任何模式下被訪問。CPSR 是當前程序狀態寄存器,該寄存器包含了條件標志位、中斷禁止位、當前處理器模式標志等一些狀態位以及一些控制位。所有的處理器模式都共用一個 CPSR 必然會導致沖突,為此,除了 User 和 Sys 這兩個模式以外,其他 7 個模式每個都配備了一個專用的物理狀態寄存器SPSR(備份程序狀態寄存器),當特定的異常中斷發生時, SPSR 寄存器用來保存當前程序狀態寄存器(CPSR)的值,當異常退出以后可以用 SPSR 中保存的值來恢復 CPSR。

因為 User 和 Sys 這兩個模式不是異常模式,所以并沒有配備 SPSR,因此不能在 User 和Sys 模式下訪問 SPSR,會導致不可預知的結果。由于 SPSR 是 CPSR 的備份,因此 SPSR 和CPSR 的寄存器結構相同。如下圖所示。

1.標志位

N、Z、C、V均為條件碼標志位。它們的內容可被算術或邏輯運算的結果所改變,并且可以決定某條指令是否被執行。

2.Q標志位

在ARMv5以前的版本Q標志位沒有意義,屬于帶擴展的位。在ARMv5以后的版本Q位用于判斷是否發生了溢出。

3.控制位

CPSR的低8位統稱為控制位。當發生異常時,這些位也發生了相應的變化。另外,在特權模式下,也可以通過軟件編程的方式來改變這些位的值。

- 中斷禁止位

I=1,IQR被禁止,

F=1,FIQ被禁止。

- 狀態控制位

T=0是ARM狀態,

T=1是Thumb狀態。

- 模式控制位

M[4:0]為模式控制位。

| M[4 : 0] | 處理器模式 | 可以訪問的寄存器 |

|---|---|---|

| 0b10000 | User | PC,R14~R0,CPSR |

| 0b10001 | FIQ | PC,R14_fiq |

| 0b10010 | IRQ | PC,R14_irq |

| 0b10011 | Supervisor | PC,R14_svc |

| 0b10111 | Abort | PC,R14_abt |

| 0b11011 | Undefined | PC,R14_und |

| 0b11111 | System | PC,R14~R0,CPSR |

| 0b10110 | Monitor | PC,R14_mon |

| 0b11010 | HYP | PC,R14_hyp |

值得注意的是,對于Cortex-M3/M4系列的處理器,與CPSR對應的是xPSR。

xPSR實際上對應3個寄存器:

① APSR:Application PSR,應用PSR

② IPSR:Interrupt PSR,中斷PSR

③ EPSR:Exectution PSR,執行PSR

這3個寄存器含義如下:

程序寄存器的位域描述如下:

這3個寄存器,可以單獨訪問:

MRS R0, APSR ;讀APSR

MRS R0, IPSR ;讀IPSR

MSR APSR, R0 ;寫APSR

這3個寄存器,也可以一次性訪問:

MRS R0, PSR ; 讀組合程序狀態

MSR PSR, R0 ; 寫組合程序狀態

所謂組合程序狀態,如下表所示:

2.2 程序計數器(PC)

馮 ·諾伊曼計算機體系結構的主要內容之一就是“程序預存儲,計算機自動執行”!處理器要執行的程序(指令序列)都是以二進制代碼序列方式預存儲在計算機的存儲器中,處理器將這些代碼逐條地取到處理器中再譯碼、執行,以完成整個程序的執行。為了保證程序能夠連續地執行下去,CPU必須具有某些手段來確定下一條取指指令的地址。程序計數器(PC )正是起到這種作用,所以通常又稱之為‘指令計數器’。CPU總是按照PC的指向對指令序列進行取指、譯碼和執行,也就是說,最終是PC 決定了程序運行流向。故而,程序計數器(PC )屬于特別功能寄存器范疇,不能自由地用于存儲其他運算數據。

在程序開始執行前,將程序指令序列的起始地址,即程序的第一條指令所在的內存單元地址送入PC,CPU 按照 PC的指示從內存讀取第一條指令(取指)。當執行指令時,CPU自動地修改PC 的內容,即每執行一條指令PC增加一個量,這個量等于指令所含的字節數(指令字節數),使 PC總是指向下一條將要取指的指令地址。由于大多數指令都是按順序來執行的,所以修改PC 的過程通常只是簡單的對PC 加“指令字節數”。

當程序轉移時,轉移指令執行的最終結果就是要改變PC的值,此PC值就是轉去的目 標地址。處理器總是按照PC 指向取指、譯碼、執行,以此實現了程序轉移。

ARM 處理器中使用R15 作為PC,它總是指向取指單元,并且ARM 處理器中只有一個PC 寄存器,被各模式共用 。R15 有32 位寬度(下述標記為R15[31:0],表示R15 的‘第31位’到‘第0位'),ARM 處理器可以直接尋址4GB 的地址空間(2^32 = 4G )。

(解釋什么是字對齊什么是半字對齊)存儲器是計算機中用于記憶數據信息的電子裝置,它通過記憶“高/低”電平記憶“1/0”能記憶 1 位“1/0”數據的電子單元,稱之為存儲元,計算機中的存儲器通常將每8 個這樣的存儲元組成一個單元,稱之為字節,字節是處理器訪問存儲器的最小單位。ARM 處理器對存儲器空間的訪問分辨率以字節為最小單位;ARM 處理器還支持 16bit 數據(2 字節)的存儲器訪問和 32bit數據(4 子節)的存儲器訪問。在ARM 中將32 位的數據稱之為‘字’,將 16 位的數據稱之為‘半字’。

ARM 處理器在對于“字”/ “半字”數據進行訪問時,對數據的存儲格式是有要求的。要求被訪問的“半字”必須存放在存儲器緊鄰的兩個字節單元,并且首字節地址必須能被2整除,這樣存儲的 16bit 數據稱為 ‘半字對齊’存儲數據,16bit 數據這樣的存儲方式稱為‘半字對齊’存儲。類似的,ARM 處理器在進“字”數據訪問時,要求被訪問的“字”必須存放在存儲器緊鄰的4 個字節單元,并且首字節地址必須能被4 整除,這樣存儲的32bit數據稱為‘字對齊’存儲數據,32bit 數據這樣的存儲方式稱為‘字對齊’存儲。

能被2 整除數據的二進制表示,其最低位一定是‘0’;能被4 整除數據的二進制表示,其最低兩位一定是‘00’。ARM 體系要求32 位長的ARM 指令在存儲器中必須字對齊存儲,16 位長的 Thumb 指令必須半字對齊存儲。因此,在ARM 狀態下,R15 的值總是能被4 整除,也就是R15 寄存器的最低2 位總是 0;Thumb 狀態下,R15 的值總是能被2 整除,也就是R15 寄存器的最低位總是0。

審核編輯:湯梓紅

-

ARM

+關注

關注

134文章

9084瀏覽量

367382 -

嵌入式

+關注

關注

5082文章

19104瀏覽量

304804 -

寄存器

+關注

關注

31文章

5336瀏覽量

120230 -

STM32

+關注

關注

2270文章

10895瀏覽量

355730 -

C語言

+關注

關注

180文章

7604瀏覽量

136686

發布評論請先 登錄

相關推薦

深入理解STM32

對arm按鍵中斷的深入理解

對棧的深入理解

為什么要深入理解棧

淺談ARM寄存器組織

深入理解ARM寄存器

深入理解ARM寄存器

評論