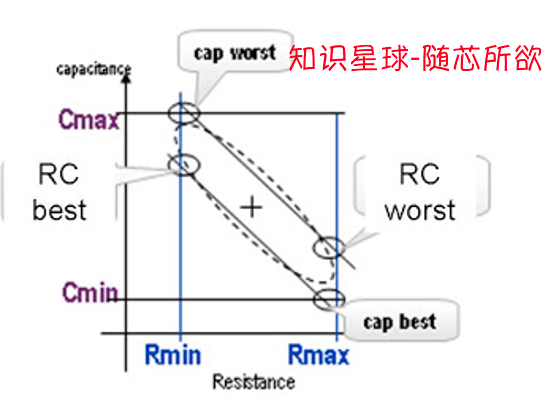

90nm 更早的工藝,通常都只有兩個RC Corner: Cworst = Cmax, Rmin;

Cbest =Cmin, Rmax 電容電阻特性分別占主導。

90nm后更新的工藝,考慮到互連線coupling的影響,出現了RCworst, RCbest corner. RCbest(也被稱為XTALK Corner)= Cc max(此時耦合電容最大),Cg x R min RCworst(也被稱為Delay Corner)= Cg x R max(此時RC的乘積最大), Cc min Cc是耦合電容,Cg是對地電容

因此加起來就有4個RC Corner,

Cbest, Cworst, RCbest,

C-best:

?它具有最小的電容,所以也被稱為Cmin Corner;

?互連電阻大于Typical Corner;

?此Corner導致那些nets都非常短的路徑的延遲非常小,可用于hold分析。

C-worst:

?具有最大的電容,所以也被稱為Cmax Corner;

?互連電阻小于Typical Corner;

?此Corner導致那些nets都非常短的路徑的延遲非常大,可用于setup分析。

RC-best:

?指最小化互連RC乘積的Corner,所以也被稱為RC-min Corner; ?通常對應于較小的蝕刻,這增加了Trace(實際走線)的寬度。這導致最小的電阻,但其電容值要大于Typical Corner; ?對于具有長互連的路徑,該Corner具有最小的路徑延遲,可用于hold分析。

RC-worst:

?指最大化互連RC乘積的Corner,所以也稱為RC-max Corner;

?通常對應于較大的蝕刻,這會減少Trace(實際走線)的寬度,這導致最大的電阻,但其電容值要小于Typical Corner;

?對于具有長互連的路徑,該Corner具有最大的路徑延遲,可用于setup分析。

Typical:

?典型值,這是指互連電阻和電容的標稱值。

總結: 所以你可能已經注意到有兩種類型的寄生:一種是基于C的,另一種是基于RC的。 在基于C的里面,C意味著最差和最佳情況的電容C;

但在基于RC的里面,RC意味著最差和最佳情況的電阻R,同時調整C為最差或最佳。

根據經驗,發現基于C的提取比基于RC的提取為內部時序路徑提供了更差和最好的情況,因為電容主導了短線。

然而,對于大型設計,由于R在長導線中占優勢,因此Block之間的時序路徑(inter-block timing path通常)最差,RC寄生效應最差。

注意:沒有Corner能保證任意晶體管驅動任意導線拓撲的最小或最大延遲 借助下面的圖片,很容易理解該內容:

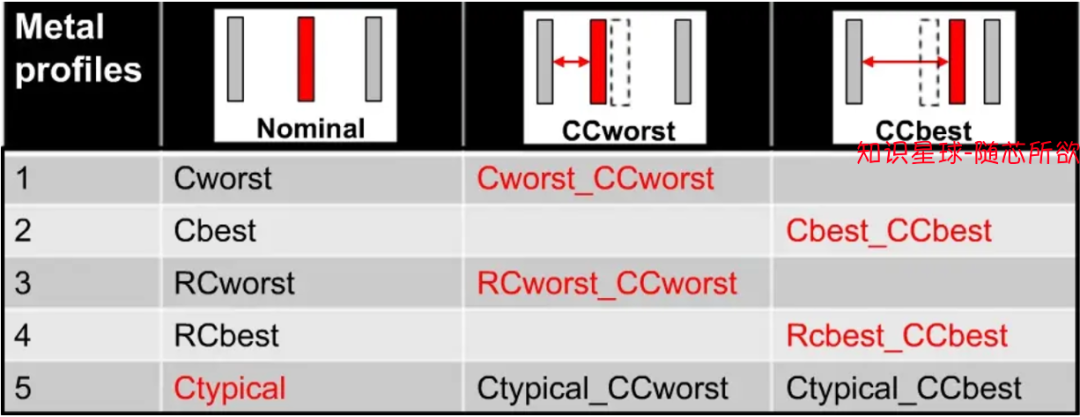

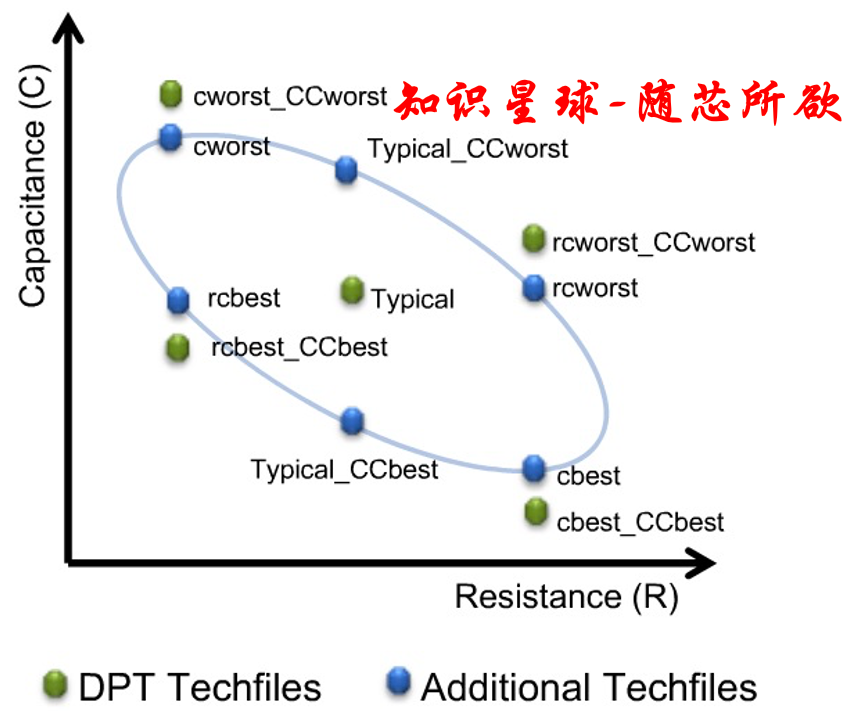

在先進工藝的下,會引入Double Pattern,考慮到不同Mask之間的misalign,因此會增加額外的CCworst和CCbest Corner。引入Double Pattern之后的Corner如下:

它們之間的RC關系如下:

審核編輯:劉清

-

寄生電容

+關注

關注

1文章

292瀏覽量

19236 -

耦合電容

+關注

關注

2文章

154瀏覽量

19827 -

電容電阻

+關注

關注

0文章

12瀏覽量

6708

原文標題:RC Corner詳細講解

文章出處:【微信號:集成電路設計及EDA教程,微信公眾號:集成電路設計及EDA教程】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

嵌入式系統基礎知識講解

Oracle數據庫基礎知識講解

RC Corner基礎知識詳細講解

RC Corner基礎知識詳細講解

評論