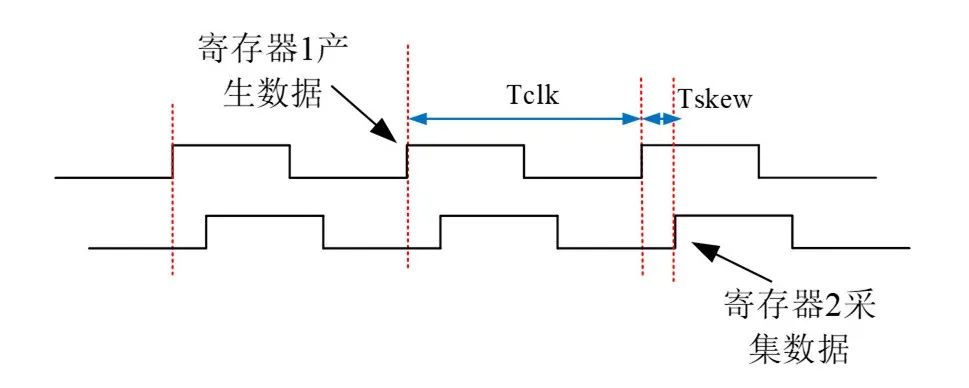

Q:clock skew會影響時序違例嗎?

對于發送時鐘和接收時鐘是同一時鐘的單周期路徑,時鐘抖動對建立時間有負面影響,但對保持時間沒有影響。

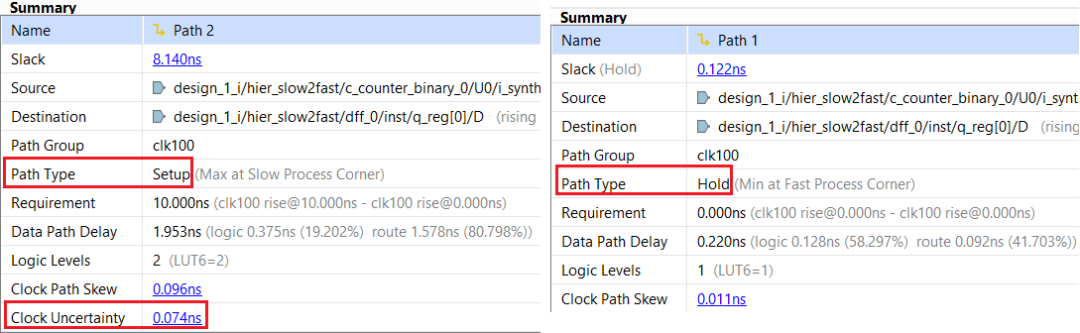

這一點,在Vivado的時序報告中也可以看到。

如下圖所示,圖中左側為建立時間時序報告,可以看到Clock Uncertainty,而右側為保持時間時序報告,是沒有Clock Uncertainty。

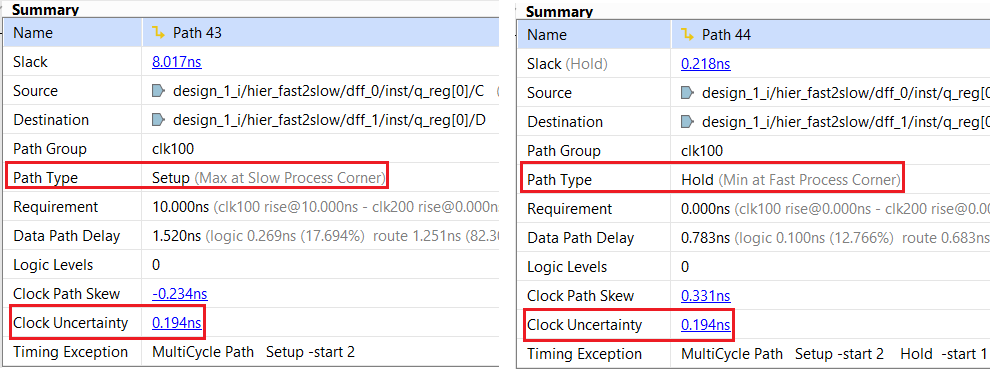

但如果發送和接收是不同的時鐘,而且這兩個不是異步時鐘,那我們可采用多周期路徑進行約束,這個時候,skew對建立和保持時間都是有影響的,也可以從時序報告中看出:

Q:定義一個parameter不指明位寬,工具在implemention時應該是會自動轉換成最小位寬么?

A:如果parameter沒定義位寬,vivado應該會默認為integer類型,parameter的參數應該不會在implemention看到,在綜合之前就會把這些參數吃掉了。

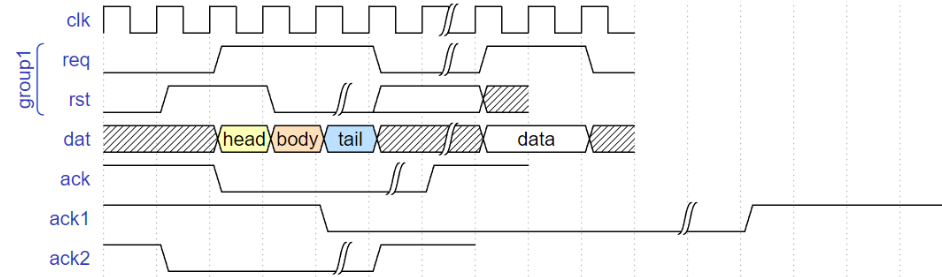

Q:有什么好用的時序繪圖工具?

A:WaveDrom是一個免費開源的在線數字時序圖渲染引擎。它可以使用JavaScript, HTML5和SVG來將時序圖的WaveJSON描述轉成SVG矢量圖形,從而進行顯示。WaveDrom可以嵌入到任何網頁中。

下圖是WaveDrom畫出來的時序圖:

image-20230611175031176

image-20230611175031176

Q:fpga + dac輸出波形,為何鋸齒波的時候,頻率稍微高一點,幅度下降,正弦波卻不會下降?

A:這跟鋸齒波的頻譜有很大關系,如果我們畫一下鋸齒波的頻譜,會發現它的頻譜是很寬的,不像正弦波是單一的頻點,所以當鋸齒波信號帶寬超過DAC的帶寬時,輸出的信號就會被削弱。

審核編輯:劉清

-

正弦波

+關注

關注

11文章

644瀏覽量

55408 -

SVG

+關注

關注

0文章

127瀏覽量

16432 -

時鐘信號

+關注

關注

4文章

449瀏覽量

28571 -

異步時鐘

+關注

關注

0文章

17瀏覽量

9407 -

Vivado

+關注

關注

19文章

812瀏覽量

66580

原文標題:FPGA問答系列--clock skew是影響時序收斂嗎?

文章出處:【微信號:傅里葉的貓,微信公眾號:傅里葉的貓】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

UltraFast設計方法時序收斂快捷參考指南

FPGA 高級設計:時序分析和收斂

使用時鐘PLL的源同步系統時序分析

Skew Correction Using Delay Li

基于MCMM技術IC時序收斂的快速實現

時序分析之useful skew的作用分析

同步電路設計中CLOCK SKEW的分析說明

clock skew會影響時序收斂嗎?

clock skew會影響時序收斂嗎?

評論