Checks和coverage是覆蓋率驅動的驗證流程的關鍵。在驗證環境中,Checks和coverage可以被定義在多個位置。

在Classes中實現Checks和Coverage

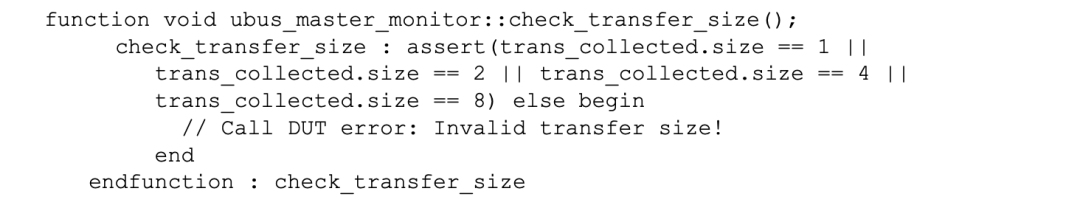

uvm_monitor的派生類總是存在于agent中,因此包含必要的Checks和Coverage。下面是一個斷言檢查的簡單例子,傳輸的size字段是1、2、4或8。否則斷言失敗。

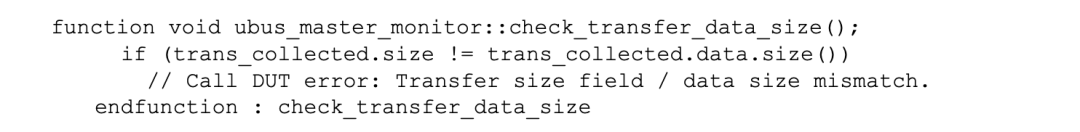

check也可以寫成函數的形式,例如檢查size字段的值與動態數組的size相匹配。

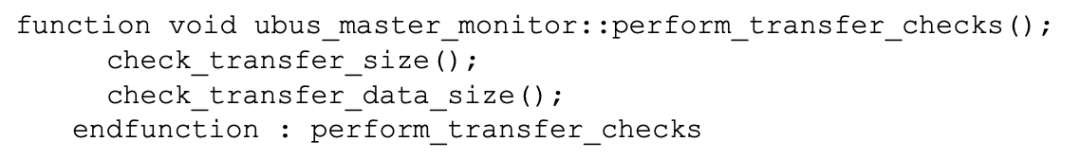

這兩個檢查都應該在transfer被monitor收集時執行。由于這些check是在同一時間發生的,所以可以封裝成一個函數,這樣就只需要進行一次調用。

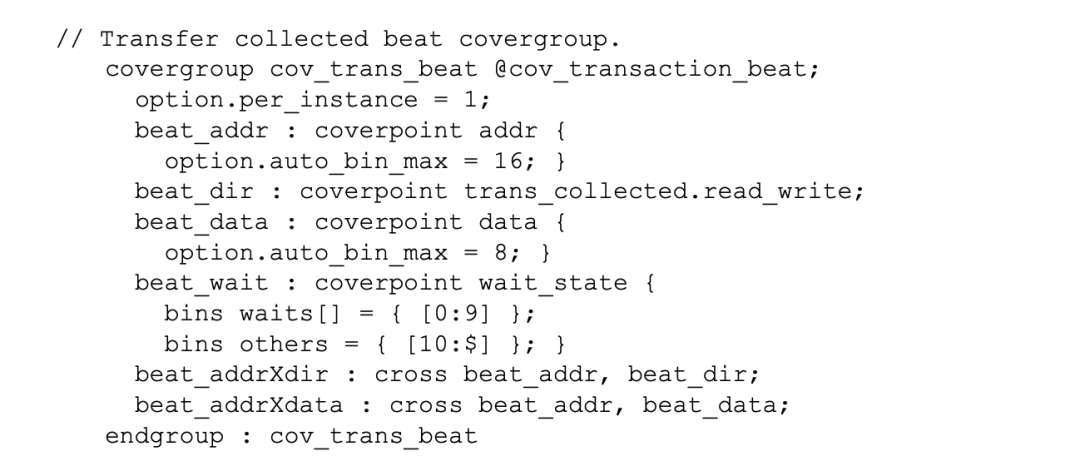

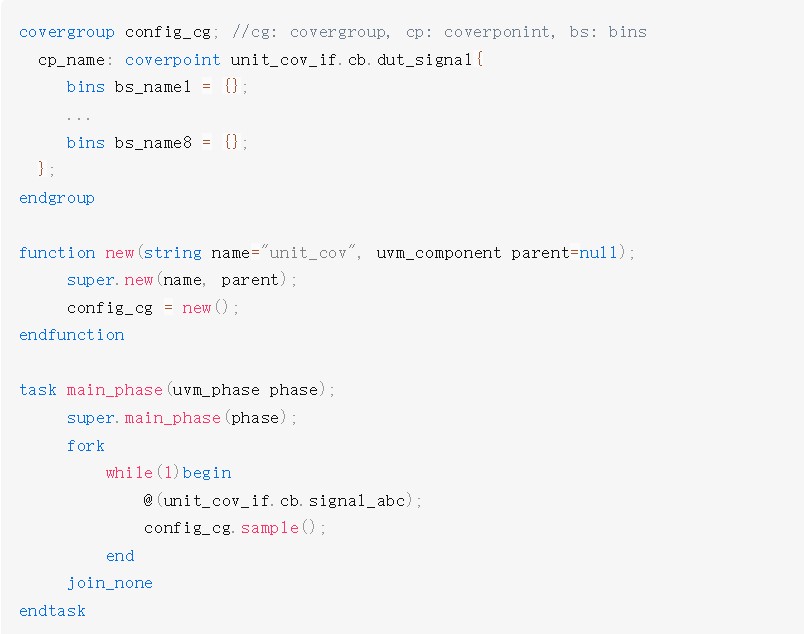

功能覆蓋是通過SystemVerilog covergroups實現的,下面是一個簡單的covergroups的例子。

這個covergroup被定義在一個從uvm_monitor派生出來的類里面。對于上述covergroup,應該在一個函數中聲明作為coverpoints的局部變量,然后對covergroup進行采樣。

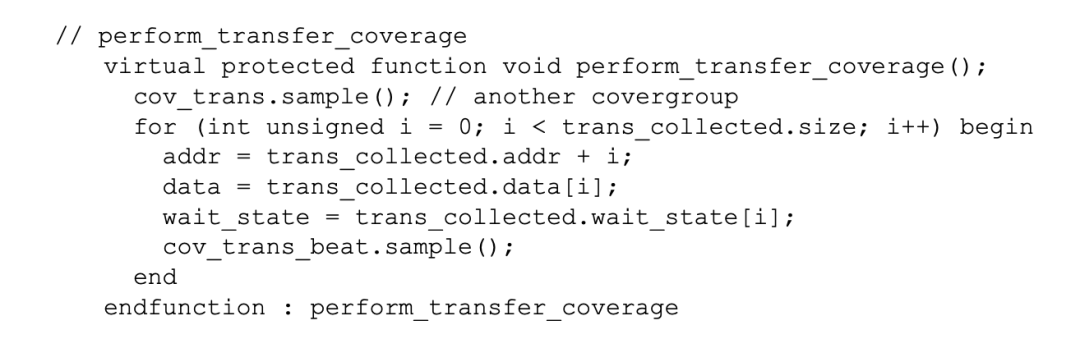

SystemVerilog沒有提供動態數組覆蓋率收集的能力,這個函數實現了這個功能。perform_transfer_coverage()函數會像 perform_transfer_checks()一樣,在transaction被monitor收集時調用。

在Interfaces中實現Checks和Coverage

InterfacesChecks被實現為assertions,以檢查信號協議為主。例如,一個斷言可能會檢查一個地址在有效的傳輸過程中從未出現過X。

在Formal FPV中,

當property表達DUT的內部和輸出行為時,使用assert進行檢查。

當property表達產生DUT激勵的環境行為時,就使用assume約束。

控制Checks和Coverage

應該提供一個字段來控制Checks是否被執行和Coverage是否被收集,該字段可以通過uvm_config_db接口來控制。下面是一個使用checks_enable位來控制Checks的例子。

if (checks_enable) perform_transfer_checks();

uvm_config_db#(int)::set(this,"masters[0].monitor", "checks_enable", 0);

?

審核編輯:劉清

-

Verilog

+關注

關注

28文章

1351瀏覽量

110077 -

UVM

+關注

關注

0文章

182瀏覽量

19167 -

DUT

+關注

關注

0文章

189瀏覽量

12373

原文標題:在驗證環境中開發Checks和Coverage

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

在STM32F334上使用IAR開發環境和jlink的SWD接口調試,怎么設置才可以使用IAR的code coverage功能?

【大聯大世平Intel?神經計算棒NCS2試用體驗】2.搭建OpenVino開發環境下——測試驗證開發環境

ST-Link調試開發環境介紹設置步驟

重點厘清覆蓋率相關的概念以及在芯片開發流程中跟覆蓋率相關的事項

SpinalHDL開發環境搭建步驟相關資料分享

聊聊芯片IC驗證中的風險

SystemVerilog實用知識點:覆蓋率之Function Coverage

可重用的驗證組件中構建測試平臺的步驟

在驗證環境中開發Checks和Coverage的步驟

在驗證環境中開發Checks和Coverage的步驟

評論