隨著SoC的容量和復雜性不斷增加,交叉開關帶來了路由擁塞、硅芯片面積過度使用和功耗等挑戰。

在不久的過去,片上系統 (SoC) 設備與今天的產品相比相對簡單。早期的 SoC 通常由 10 到 20 個IP塊組成,每個塊通常由大約 10,000 到 50,000 個邏輯門組成。大多數這些 IP,包括處理器和外圍功能,都是從第三方供應商處獲得許可的。開發人員通常只創建一個或兩個 IP,其中包含使他們的 SoC 區別于其他競爭產品的“秘密武器”。 當需要有限數量的 IP 來相互通信的互連相對簡單時,會使用經典的總線架構方法。負責極少數啟動器 IP 的設計人員使用了這種方法,這些啟動器 IP 將數據事務請求與響應這些請求的多個目標 IP 相結合。 隨著 IP 數量和規模的增加以及它們承擔起發起者的角色,采用交叉開關形式的更復雜的互連架構變得很有必要。交叉開關是有利的,因為它允許任何發起者 IP 與任何目標 IP 對話。

然而,隨著 SoC 的容量和復雜性不斷增加,交叉開關帶來了路由擁塞、硅芯片面積過度使用和功耗等挑戰。

輸入NoC

今天的 SoC 可以包含數百個 IP 塊,每個塊都比前幾代具有更多的邏輯門。通常,第三方供應商提供大部分 IP。除了數據總線寬度、控制總線功能和工作頻率的變化之外,每個 IP 還可以采用多種接口協議中的一種——OCP、APB、AHB、AXI、STBus 和 DTL——這些協議已被 SoC 設計人員定義和采用. 應對當今 SoC 中 IP 數量不斷增加的挑戰的解決方案是采用片上網絡 (NoC)。每個 IP 都配備了與 NoC 接口的套接字功能。在發起者觸發寫訪問的情況下,套接字序列化和打包由該 IP 生成的數據,并將其傳輸到其預期目標。反過來,與目標關聯的套接字將從數據包中提取要寫入的數據,并將其轉換為目標協議。可以同時有多個數據包。

什么是NoC?

NoC 可以通過多種拓撲結構實現,包括不規則樹、規則環和網狀或圓環結構。高維架構也可用于某些設計,包括三維立方體和四維和五維超立方體。 在大多數情況下,單個 NoC 是不夠的,設計人員經常將其互連分解為數十個 NoC 的組合。雖然非高速緩存一致的 NoC 可以滿足大多數外設的要求,但處理器和加速器等 IP 通常受益于高速緩存一致的 NoC 的功能。此外,SoC 的某些部分,例如人工智能/機器學習 (AI/ML) 處理節點陣列,可能會受益于網狀 NoC 架構。因此,SoC 可以輕松地結合多個 NoC 拓撲以實現最佳結果。 除了用于將 IP 連接到 NoC 的套接字之外,網絡還將包括必要的交換機和緩沖區。此外,隨著用于實現 SoC 的工藝節點不斷縮小,走線的電阻增加,導致信號在通過器件時出現電阻-電容延遲。因此,信號無法再在單個時鐘周期內遍歷設備的全部或部分。解決這個問題需要在信號通路中插入流水線寄存器。然而,優化它們的數量和位置是一項艱巨的任務。

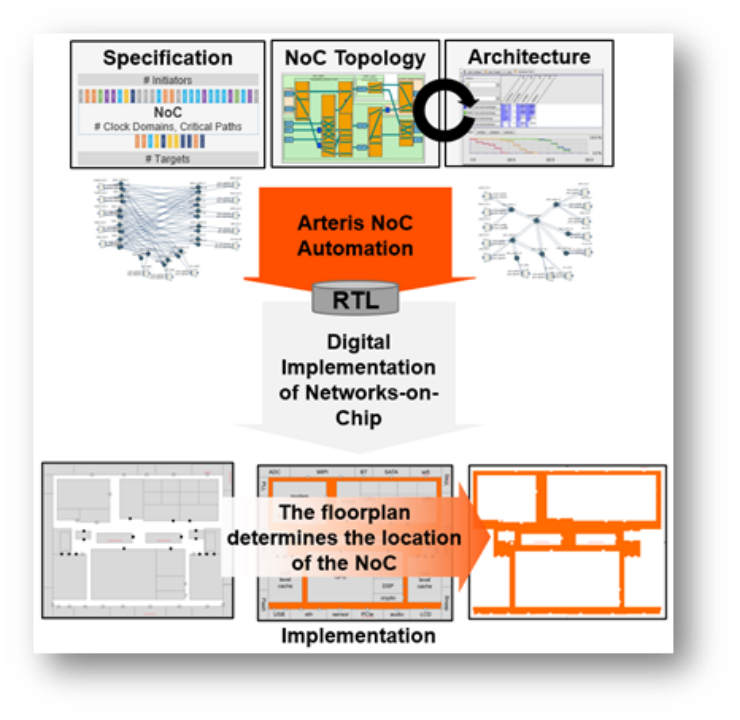

圖 1這是典型 NoC 配置和實施流程的概覽。來源:Arteris IP

SoC 的開發是雙重的——前端(上游)和后端(下游)設計(見圖1)。前端設計側重于邏輯和功能方面,例如使用哪些 IP、如何連接它們以及如何構建網絡以確保預期的吞吐量和延遲。另一方面,后端設計處理芯片的物理方面,包括 IP 相對于彼此的放置位置以及時序是否可以滿足。只有在這個階段,設計人員才會知道放置流水線寄存器的數量和位置。 執行完整的物理布局是一個耗時的過程。任何無法在后端解決的問題都必須在前端返工,這將重新啟動耗時的物理布局過程(參見圖 2)。能夠在流程的早期主動插入流水線寄存器對于實現任務的收斂和整個項目的周轉時間非常有價值。

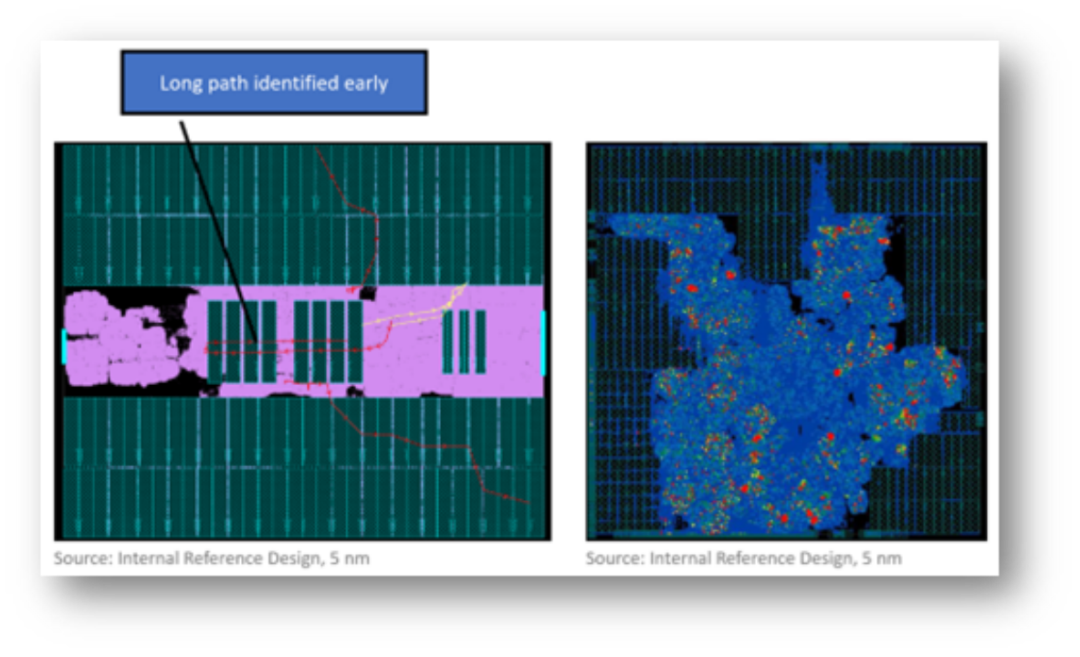

圖 2長時序路徑可以跨越整個 SoC。來源:Arteris IP

這給前端設計團隊帶來了很大壓力,他們不一定擁有做出明智決策所需的所有信息。插入太少的流水線寄存器會導致 SoC 無法滿足物理布局中的時序要求。這導致通過插入太多流水線階段來過度設計問題的趨勢。盡管可能會滿足時序要求,但級數過多會增加延遲和功耗。 所有這一切的結果是,僅擁有套接字、開關、緩沖區和流水線寄存器形式的原始 NoC。為了驗證性能和實現時序,NoC 的實現工具有必要了解它們將服務的環境。

物理感知NoC

在“物理感知”NoC IP 中,前端設計人員可以使用來自物理布局團隊的早期 IP 布局信息來預測實現能力并解決任何潛在的時序問題。作為其中的一部分,NoC 工具可以自動定義 RTL 中流水線寄存器的理想數量和位置,并生成相關的實現約束。 當今的 NoC 技術遠遠超出了許多設計人員的預期。例如,NoC 生成器利用特定于工藝技術節點的幾何和延遲信息。此信息使我們能夠進一步完善時序估計并確定流水線寄存器要求和位置。 通過以這種方式改進前端設計并向后端工具提供更詳細的信息,可以顯著改進整個過程,尤其是第一個物理實現。這可以顯著減少后端到前端的迭代次數,從而降低風險、提高生產率、降低成本并加快上市時間和資金周轉時間。

編輯:黃飛

-

寄存器

+關注

關注

31文章

5336瀏覽量

120232 -

片上網絡

+關注

關注

0文章

33瀏覽量

11804

原文標題:?SoC設計:什么時候片上網絡 (NoC) 不夠用?

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何利用NoC資源去支撐FPGA中的創新設計

怎么構建一種基于FPGA的NoC驗證平臺?

SOC設計與驗證流程是什么?

SoC芯片的開發流程有哪幾個階段

SoC設計流程相關資料下載

SOC的多核啟動流程詳解

SoC設計流程

從SoC到NoC:芯片架構的演進與變革

AMD Versal系列FPGA NoC介紹及實戰

傳智驛芯聯手Arteris,利用創新NoC技術駕馭復雜SoC設計

?SoC設計:NoC 配置和實施流程

?SoC設計:NoC 配置和實施流程

評論