信號特征的描述

信號完整性研究的是如何使驅動器輸出的信號傳輸到接收器件并被正確接收。由此,我們定義了信號完整性的三要素分別是:

- 信號;

- 驅動接收芯片;

- 傳輸通道。

這其中信號是主體,我們要做的主要工作就是設計好信號的傳輸路徑為信號的正確傳輸掃清障礙。要做信號完整性分析與設計首先要了解信號的特性,以及信號質量的判別標準。

對一個信號進行描述通常需要如下幾個指標:

信號特性的描述

** 擺幅:** 信號從低電平到高電平之間的電壓差,對于單端信號通常由信號的供電電壓決定。通常情況下擺幅越大越不容易出現信號完整性問題,但隨著半導體工藝的進步信號的擺幅在不斷地降低。就拿存儲器來說早期的SDRAM還是3.3V的TTL電平,而DDR3采用SSTL電平最低電壓已經達到了1.35V,現在即將量產的DDR5擺幅只有1.2V,LPDDR5的VDDQ電壓甚至低到了0.5V。可想而知信號完整性面臨的挑戰越來越大。

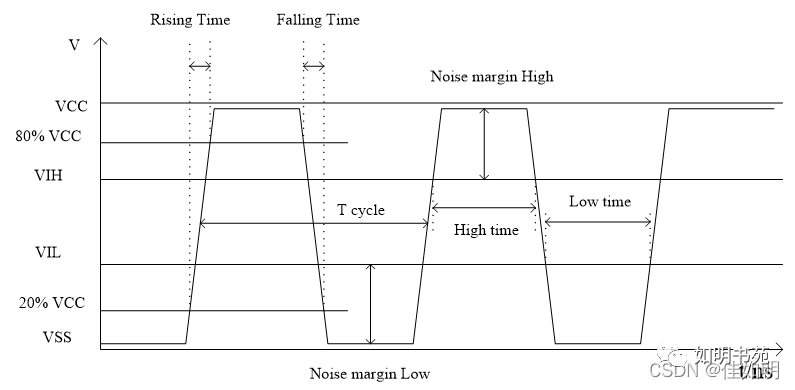

** 上升、下降時間:** 通常數據手冊或者IBIS模型中都會定義信號從20% VCC到80% VCC(或者10% VCC到90% VCC)的時間。信號的上升下降時間決定了信號的帶寬也就是信號的頻域特性,信號的上升下降時間越小,信號的帶寬越高,也就越容易產生信號完整性問題。通常情況下信號的上升下降時間受到芯片工藝、工作環境溫度、供電電壓等因素影響。

** 時鐘頻率:** 對于時鐘信號波形重復出現的頻率就是時鐘頻率,單位為Hz。時鐘頻率是時鐘周期的倒數。通常情況下時鐘頻率越高,留給總線的時序裕量就越小,時序問題也就越突出。

** 數據速率:** 對于數據信號由于波形不像時鐘那樣周期性重復,衡量數據傳輸快慢不能單看時鐘頻率。數據速率的單位為bps(bit/s),即每秒傳輸的數據bit數。對于時鐘單沿(通常為上升沿)采樣的系統,數據速率在數值上等于時鐘頻率;而對于雙沿采樣的系統,數據速率在數值上等于時鐘頻率的兩倍(如DDR的DQ信號)。

** 有效位寬:** 有效位寬分為高電平有效位寬和低電平有效位寬,是指信號保證為高或低電平的有效時間。在進行時序分析時必須保證接收端信號有足夠的高低電平有效位寬來滿足接收端對建立保持時間的要求。

** 噪聲裕量:** 分為高電平噪聲裕量和低電平噪聲裕量,指的是信號高電平和低電平到高低電平判決門限VIH和VIL之間的電壓差。噪聲裕量越大數據傳輸的穩定性越好,如果噪聲裕量為0或者負值,就會發生數據接收錯誤。

此外,我們也可以把 電源理解為一種特殊的信號 。芯片正常工作通常對PDN(電源傳輸網絡)提出了要求即需要PDN在多長時間內提供多大的電流。同時芯片對芯片內部電路、封裝、PCB級的電源波動都有明確要求。通常芯片內部電路允許的電源波動范圍是±10% (具體還要看芯片的spec),而對于PCB板級設計來說器件管腳處的噪聲要控制在±5%以內,此時我們就需要根據芯片電流的需求以及電壓噪聲的控制要求來設計整個PDN網絡。

芯片對電流的需求

那么什么是信號完整性的破壞呢?

信號通過互連線由驅動端向接收端傳輸,由于阻抗匹配、布線拓撲、電源噪聲、串擾等各種因素都會導致信號完整性問題。如果不能妥善解決信號完整性問題,那么在接收端接收到的信號波形就會發生畸變,產生的后果可能使總線不能滿足系統時序需求、接收端接收到錯誤的數據或者擊穿接收器件的Buffer對系統工作的穩定性造成影響,等等這些現象都叫作信號完整性破壞。

常見的信號完整性破壞包括以下幾個方面:

** 過沖(overshoot)和下沖(undershoot)** :過沖指的是信號超出供電電壓VCC的最高電壓或者低于參考地電壓VSS的最低電壓。當驅動器的驅動能力很強在源端和末端又沒有良好的阻抗匹配時就會在接收端波形產生嚴重的過沖和下沖。過沖和下沖并不會對功能產生影響,但是長期工作在過沖條件下可能會導致芯片輸入buffer擊穿,從而影響器件的使用壽命。因此,一般的器件手冊都會對過沖做出要求,有的器件會給出芯片所能承受的最大過沖電壓,有的手冊則是給出了對過沖面積(信號高于VCC或低于VSS部分的面積)的要求。

信號的過沖

振鈴(Ringback) :指接收端信號波形跳變之后并沒有達到穩定電平而是產生向著門限電壓“振蕩”的電壓波形。振鈴的形成一般都是由于阻抗不連續導致多次反射產生,振鈴使信號的噪聲裕量減小,嚴重的振鈴會導致接收錯誤。此外,振鈴還會導致信號高頻能量變多從而增大EMI問題,因此必須對其加以控制。

信號高低電平存在的振鈴

** 邊沿不單調:** 指的是信號上升沿或者下降沿存在回溝的現象。由于阻抗突變、串擾等互連線中的非理想效應有可能導致信號的上升下降邊沿出現臺階或者回溝。對于時鐘信號通常要求有單調的上升/下降邊沿用以對數據信號進行采樣;對于數據信號如果存在回溝也會使數據信號的有效位寬減小,從而減小時序裕量。

信號邊沿不單調

** 邊沿退化:** 指的是驅動器輸出的信號經過傳輸線傳輸后信號的邊沿相對于驅動器輸出信號邊沿會明顯變緩的現象。邊沿退化的原因可能是傳輸線的損耗或者負載的電容效應、其它信號的干擾、同步開關噪聲以及驅動器驅動能力不足等等。邊沿退化的影響主要體現在一些器件可能對信號上升下降時間做出了要求(如時鐘等),不能達到上升下降時間將導致無法觸發器件執行正確的操作;也可能導致數據信號上升下降時間的。

信號的邊沿退化

** 信號之間的偏移(skew** ) :接收端接收到的一組信號之間的時間差。主要由于信號的傳輸路徑上的延時不同、驅動器本身的輸出skew、以及信號傳輸過程中所遇到的噪聲干擾、同步開關噪聲等因素的影響造成。驅動器本身的輸出skew我們無法控制,只能作為設計的約束條件。我們要做的就是控制信號傳輸路徑上的上的延時以及一切對傳輸延時有影響的負面因素。一般在做DDR等高速并行總線設計時需要嚴格控制同組數據之間的skew來達到時序裕量最優化。

** 抖動(jitter** ) :指的是信號邊沿與其理想位置的偏差。在進行高速并行總線設計時過大的抖動會導致時域裕量的減小,在做高速串行總線設計時過大的抖動會導致誤碼率不達標。抖動的來源有很多包括電源噪聲、PCB布線、串擾、環境溫度、EMI輻射等等。

** 電源完整性**在高速信號傳輸過程中有著非常重要的作用。互連線路通流不足導致電壓降太大、電源網絡的濾波設計不好導致電源噪聲超標,等等這些現象都叫作電源完整性破壞。接口電源完成性的破壞會直接導致相應接口信號的噪聲、時序裕量的降低;內核電源完成性的破壞會直接導致處理器內部的指令無法正確傳輸。由此可見,電源完整性設計的目的就是保障用電芯片有穩定的電源供應,保證芯片正常工作。

如果把電路板比作人體,那么電流則是電路板的血液,電源則是心臟完成向大腦和四肢軀干(芯片)供血的工作。可想而知電路板上由電源到芯片的供電通路,也就是PDN網絡的作用有多重要了。

人體的血液流通不暢,可能導致腦梗、心梗,而電路板的PDN設計不好,也可能導致整個系統的癱瘓。電源完整性的指標分為AC和DC兩個部分,但AC和DC之間并不相互獨立,而是共同決定電源的性能。

如果這些問題單一的出現分析和解決并不會很麻煩,我們在實際設計中面臨的情況是非常復雜的可能會有很多因素作用在一起共同導致信號質量的惡化。此時就需要我們掌握信號完整性分析的手段找到產生問題的原因,并進行有針對性的整改、優化使其滿足設計要求。

-

驅動器

+關注

關注

54文章

8703瀏覽量

150139 -

PCB板

+關注

關注

27文章

1474瀏覽量

53538 -

存儲器

+關注

關注

38文章

7653瀏覽量

167587 -

信號完整性

+關注

關注

68文章

1446瀏覽量

96813 -

電源噪聲

+關注

關注

3文章

159瀏覽量

17834

發布評論請先 登錄

高速PCB電路板的信號完整性設計

聽懂什么是信號完整性

評論