點擊藍字關注我們

NCD(V)5700x 是大電流單通道柵極驅動器,內置電流隔離功能,用于在高功率應用中實現高系統(tǒng)效率和可靠性。其特性包括:互補輸入(IN+ 和 IN-),開漏故障( )和就緒 (RDY) 輸出,復位或清除故障功能(

)和就緒 (RDY) 輸出,復位或清除故障功能( ),有源米勒箝位 (CLAMP),去飽和保護 (DESAT),去飽和情況下軟關斷,拉電流 (OUTH) 和灌電流 (OUTL) 分離驅動輸出(僅限 NCD(V)57000),精確欠壓閉鎖 (UVLO),低傳播延遲(最大值90 ns)和小脈沖失真(最大值25 ns),較高的共模瞬變抗擾度 (CMTI)——在 VCM = 1500 V條件下可承受 100kV/us(最小值),輸入信號范圍涵蓋 5 V 和 3.3 V,輸出差分偏置電壓(VDD2-VEE2)最高 25 V(最大值),VDD2 額定值為 25 V(最大值),VEE2 額定值為 -10 V(最大值)。NCD(V)5700x 提供 5 kVrms 電流隔離和 1.2 kV 工作電壓能力,輸入和輸出之間的爬電距離保證至少 8 mm。寬體 SOIC-16 封裝滿足增強型安全絕緣要求。

),有源米勒箝位 (CLAMP),去飽和保護 (DESAT),去飽和情況下軟關斷,拉電流 (OUTH) 和灌電流 (OUTL) 分離驅動輸出(僅限 NCD(V)57000),精確欠壓閉鎖 (UVLO),低傳播延遲(最大值90 ns)和小脈沖失真(最大值25 ns),較高的共模瞬變抗擾度 (CMTI)——在 VCM = 1500 V條件下可承受 100kV/us(最小值),輸入信號范圍涵蓋 5 V 和 3.3 V,輸出差分偏置電壓(VDD2-VEE2)最高 25 V(最大值),VDD2 額定值為 25 V(最大值),VEE2 額定值為 -10 V(最大值)。NCD(V)5700x 提供 5 kVrms 電流隔離和 1.2 kV 工作電壓能力,輸入和輸出之間的爬電距離保證至少 8 mm。寬體 SOIC-16 封裝滿足增強型安全絕緣要求。

本應用筆記介紹 NCD(V)5700x 在系統(tǒng)應用中的一些參數、功能和設計技巧。

原版文檔獲取點擊文末的“贊”和“在看”,并發(fā)送截圖和您的郵箱地址到后臺,即可領取原版文檔哦~

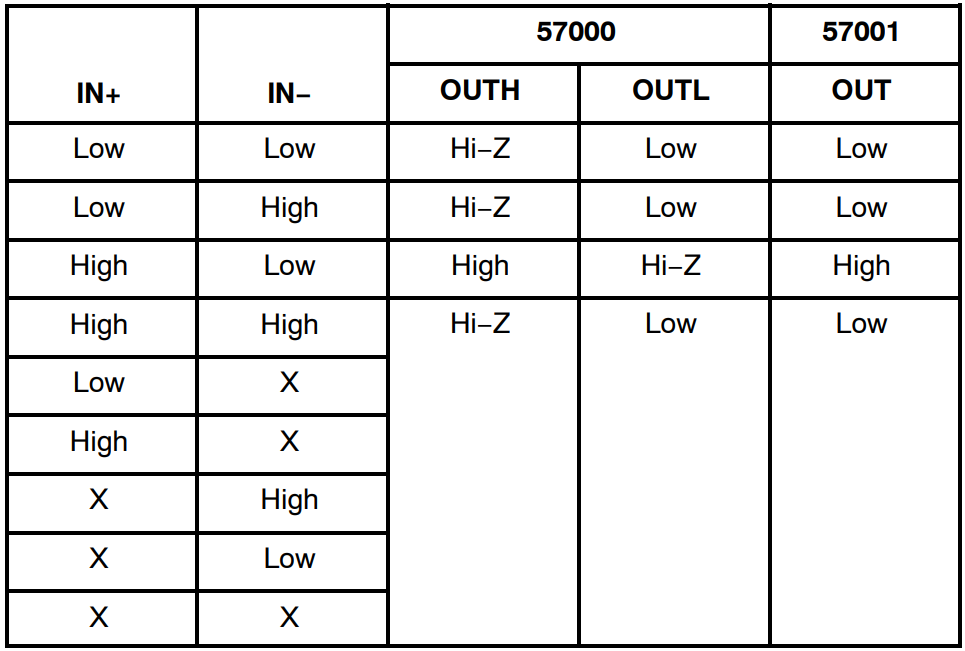

互補輸入邏輯信號與輸出之間的關系如表 1 所示。

表 1. 輸入和輸出信號邏輯

注:X:浮空,內部 50 kΩ 下拉電阻將 IN+ 下拉至 GND1,內部 50 kΩ 上拉電阻將 IN- 上拉至 VDD1。Hi-Z:高阻抗狀態(tài)。

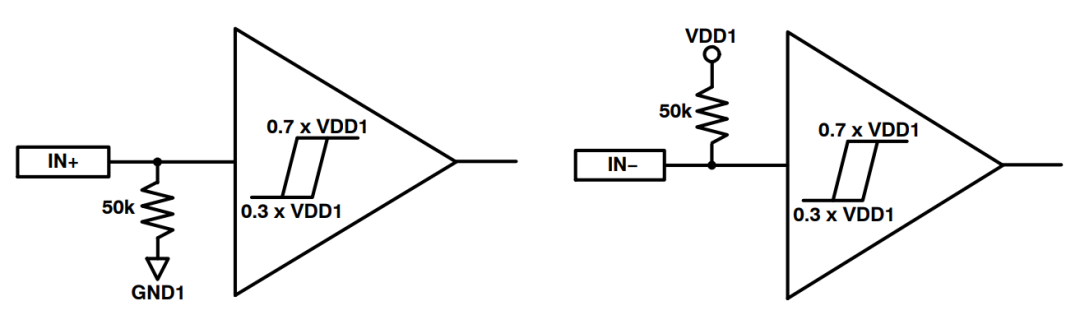

輸入邏輯信號框圖如圖 1 所示。

圖 1. 輸入邏輯信號框圖

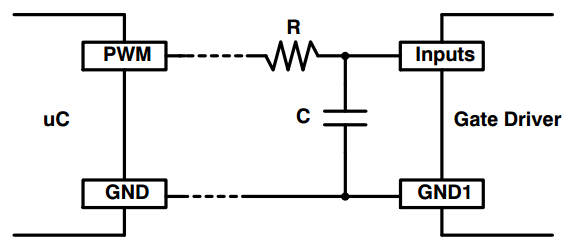

為了獲得良好的信號質量和抗擾度,可以在微控制器和柵極驅動器輸入(IN+、IN-、)之間放置一個輸入濾波器 RC 網絡。RC 值將取決于系統(tǒng)要求的輸入頻率范圍、占空比和時間延遲。此 RC 濾波器的應用電路如圖 2 所示。此 RC 濾波器需要放在盡可能靠近柵極驅動器引腳引線的地方。高壓輸出電路的共模瞬變噪聲可能會干擾低壓輸入側。數字控制輸入應使用低阻抗信號源以防止出現毛刺或造成意外開關。優(yōu)先使用標準 CMOS 或推挽驅動電路,避免開漏配置。

圖 2. 輸入信號的 RC 濾波器網絡

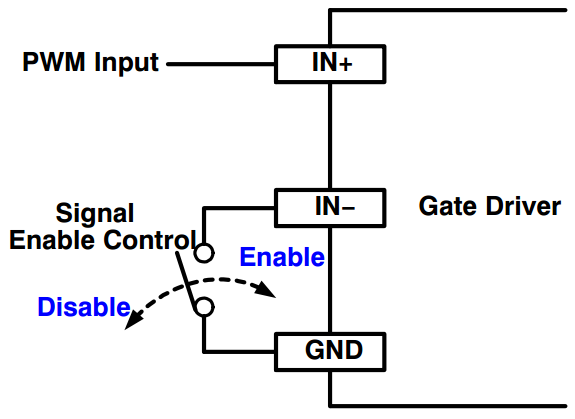

根據表 1,當 PWM 信號作用于同相輸入 (IN+) 時,反相輸入 (IN-) 可用于使能/禁用輸入信號。信號使能/禁用的電路示例如圖 3 所示。

此配置僅控制輸出信號,不控制任何保護(UVLO 和去飽和)的復位功能,輸出跟隨同相信號。

圖 3. 反相輸入 (IN-) 控制信號使能

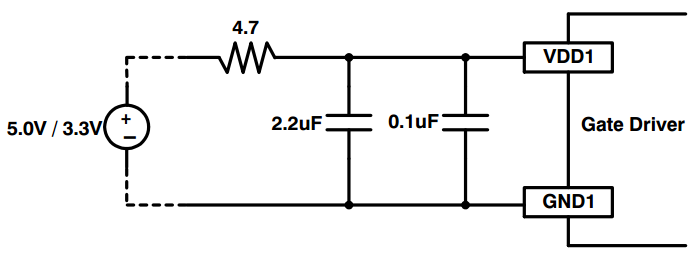

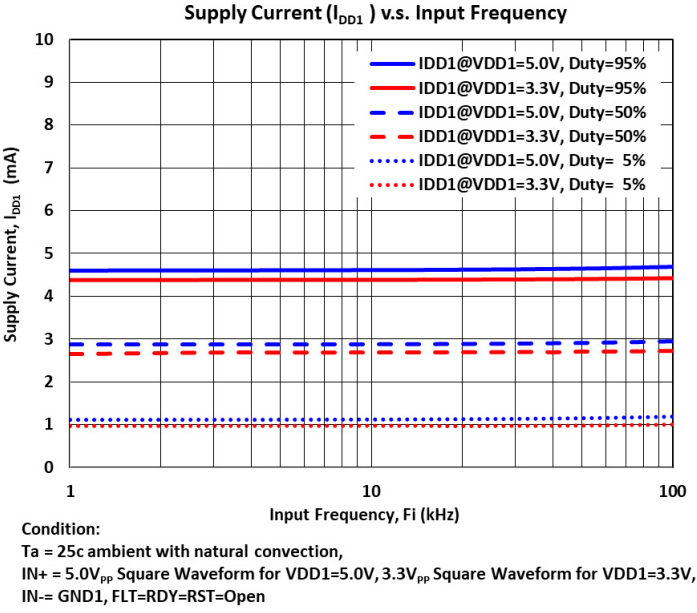

串聯電阻和解耦電容必須置于 VDD1 和 GND1 之間。電容需要盡可能靠近柵極驅動器引腳引線,以濾除任何高頻噪聲并維持輸入偏置電壓。一般使用值為 0.1 μF 和 2.2 μF 的低 ESL 和 ESR 芯片電容 (MLCC),如圖 4 所示。圖 5 顯示了 5.0 V 和 3.3 V 條件下的典型輸入偏置工作電源電流;當采用 5.0 V 或 3.3 V 電源供電時,可以估算功率需求。

圖 4.用于輸入電源偏置 (VDD1) 的解耦電容

圖 5. 輸入電源電流 (IDD1) 與輸入頻率

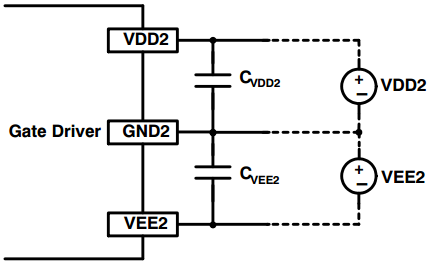

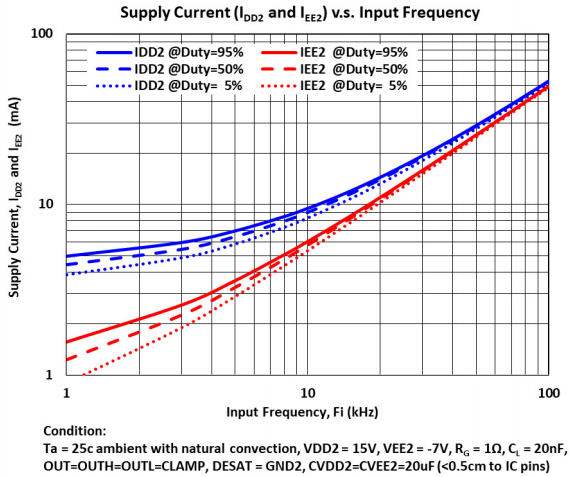

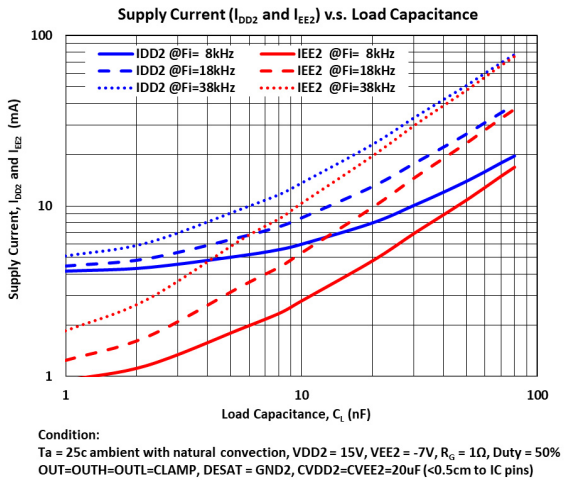

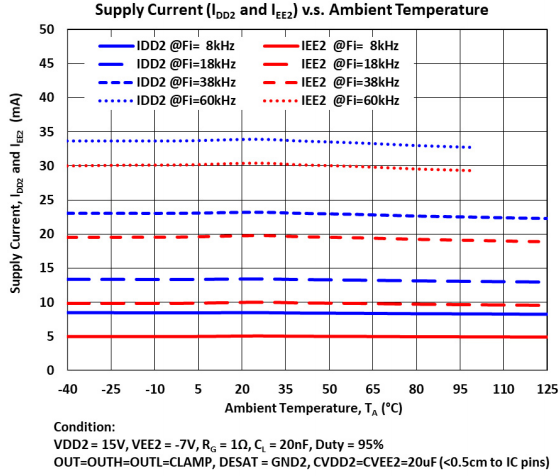

NCD5700x 系列具有高拉電流和灌電流能力。因而需要額外的布局措施,尤其是當外部柵極電阻值較小時。由于內部功率 MOSFET 導通,將出現高峰值電流瞬變。解耦電容須放置在 VDD2、VEE2 和 GND2 之間,并且盡可能靠近驅動器引腳引線,以防止 PCB 走線和封裝的寄生電感導致偏置電壓過沖或欠沖。主要電流需求來自外部負載電容,因此峰值電流取決于外部柵極電阻。在一般應用中,當柵極電阻值大于 10 Ω 時,每個正 (VDD2) 和負 (VEE2) 偏置需要 10 μF 電容。當柵極電阻小于 10 Ω 時,建議使用 20 μF 電容。當然,低 ESL 和 ESR 芯片電容 (MLCC) 是首選。電路示例如圖 6 所示。典型輸出偏置工作電源電流與輸入頻率、環(huán)境溫度、負載電容的關系分別如圖 7、圖 8 和圖 9 所示。

請注意,這些曲線代表外部柵極電阻僅為 1 Ω 時的極端開關條件。大多數應用會使用更高的柵極電阻值,因此,電流將比這些曲線中所示的值要低。可以估計正偏置和負偏置電源的功率需求。

圖 6. 用于輸出電源偏置的解耦電容(VDD2 和 VEE2)

圖 7. 輸出電源電流(IDD2 和 IEE2)與輸入頻率

圖 8. 輸出電源電流(IDD2 和 IEE2)與負載電容

圖 9. 輸出電源電流(IDD2 和 IEE2)與環(huán)境溫度

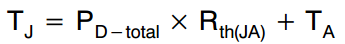

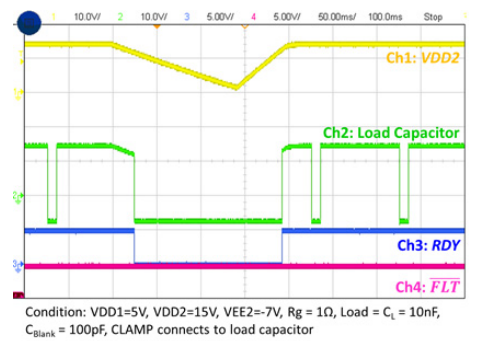

當外部柵極電阻和電源偏置是固定值時,務必檢查柵極驅動器的功耗。設計方案必須確保當器件在期望溫度范圍內工作時,器件結溫不超過額定最大值。柵極驅動器的功耗計算公式如下所示。

(公式1)

(公式1)

其中:

PD-total 為器件總功耗(W)

PD-input 為輸入偏置(VDD1)功耗 (W)

PD-output 為輸出偏置(VDD2、VEE2)功耗 (W)

為了計算輸入偏置功耗 (PD-input),可以使用圖 5 中提供的輸入電源電流值或數據表中的最大偏置電流。公式為:

(公式2)

(公式2)

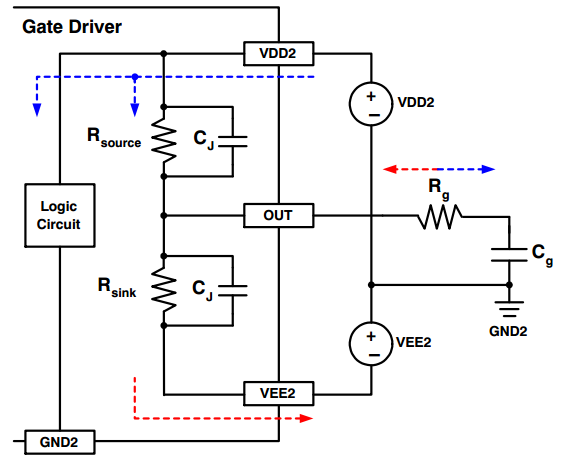

圖 10 中的框圖顯示了輸出偏置功率輸送路徑。為了計算輸出偏置功耗 (PD-output),必須考慮兩個因素。首先是拉電流/灌電流功率 MOSFET 的內部邏輯電路和結電容充放電損耗的基本工作功率需求。這可以在空載條件下使用特定的 VDD2 和 VEE2 電壓偏置條件進行測量,如圖 11 所示。其次,當輸出驅動負載時,輸出偏置的功耗在內部拉電流/灌電流功率 MOSFET 的等效導通電阻和外部柵極電阻之間分配。

圖 10.輸出偏置的功率輸送路徑

圖 11.空載時的輸出電源電流(IDD2、IEE2)與輸入頻率

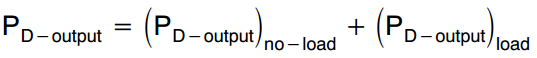

PD-output 的計算公式為:

(公式3)

其中:

Fi= 輸入頻率

Qg= 柵極電荷

Rsource = 內部拉電流 MOSFET 導通電阻  ?1Ω

?1Ω

Rsink= 內部灌電流 MOSFET 導通電阻  1Ω

1Ω

Rg= 外部柵極電阻

結溫可通過下式估算:

(公式4)

(公式4)

其中:

Rth(JA) = 結至環(huán)境熱阻

TA= 環(huán)境溫度

Tth(JA) = 150°C/W,條件:100 mm2,1 盎司銅,1 個表面層

Tth(JA) = 84°C/W,條件:650 mm2,1 盎司銅,1 個表面層和2個內部電源平面層

(公式4)也可用于計算最大結溫 TJ(MAX) 為 150°C 時環(huán)境溫度 (TA) 下的最大允許功耗 (PD )。圖 12 顯示了基于特定 PCB 布局、層和表面積的 NCD(V)5700x 系列結至環(huán)境熱阻對應的功耗降額曲線。

圖 12:NCD(V)5700x 系列的功耗降額曲線

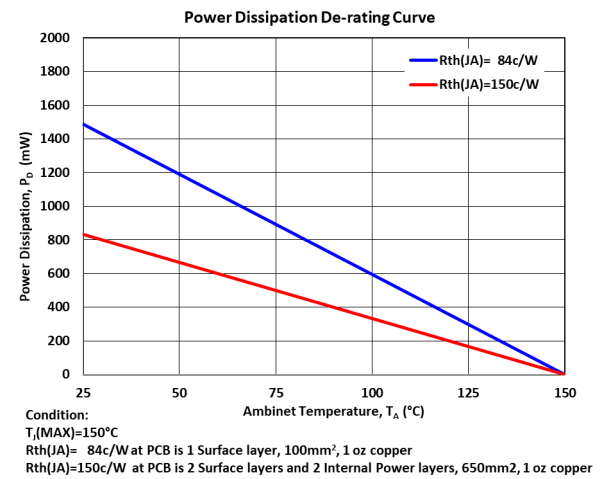

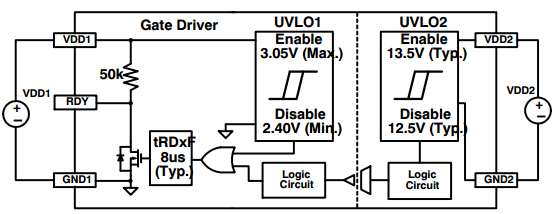

為確保驅動操作的電壓正確,輸入 (VDD1) 和輸出 (VDD2) 偏置電源通過欠壓閉鎖保護進行監(jiān)測。當 UVLO 保護被觸發(fā)時,輸出信號邏輯將立即變?yōu)榈碗娖剑瑐鞑パ舆t變短。RDY 引腳上的電源良好 (READY) 信號僅表示此 UVLO 事件,可能具有 8 μs(典型值)延遲時間。RDY 引腳輸出接口為內部開漏,通過 50 kΩ 上拉電阻拉至 VDD1。圖 13 中的框圖顯示了 UVLO 和 RDY 功能。詳細時序圖已在數據表中給出。圖 14 和圖 15 顯示,RDY 僅與欠壓閉鎖保護相關。

圖 13:NCD(V)5700x 系列的 UVLO 和 RDY 功能框圖

圖 14:NCD(V)5700x 系列的 UVLO2 觸發(fā)時的 RDY 波形

圖 15:NCD(V)5700x 系列的 DESAT 保護觸發(fā)時的 FAULT 波形

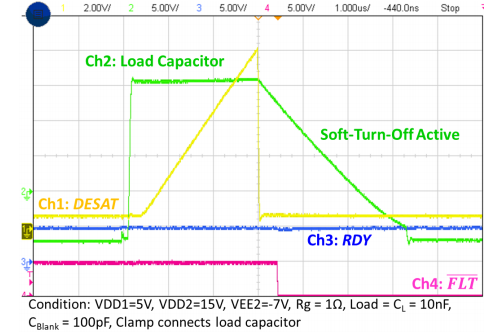

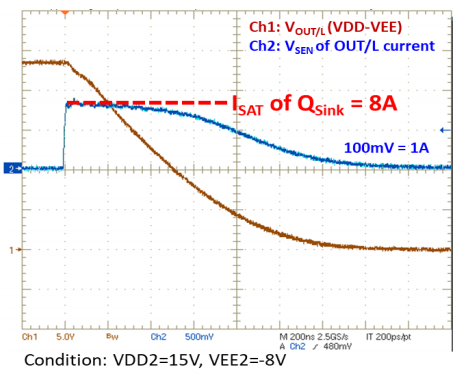

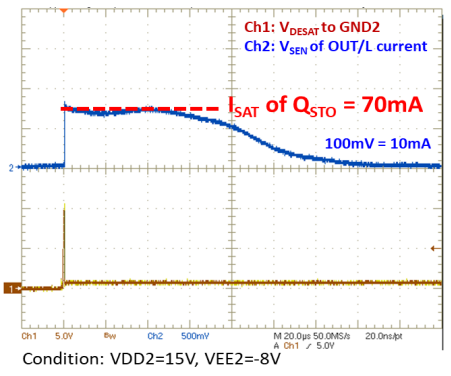

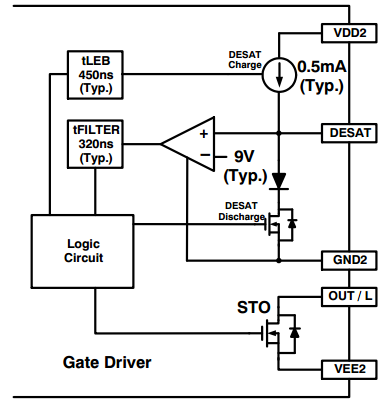

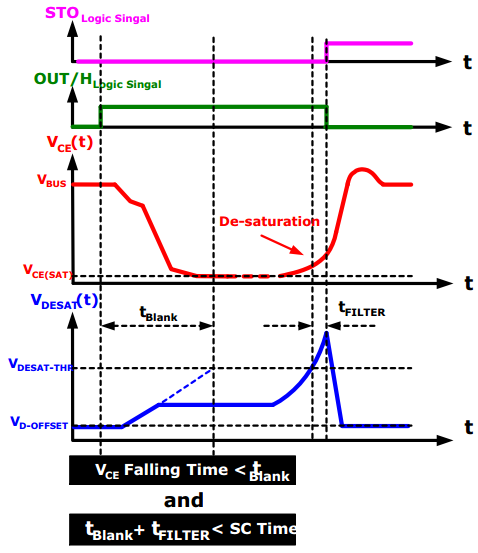

為了防止功率半導體器件在過流或短路事件中消耗過多功率,去飽和保護功能是一種在柵極驅動器中加以實現的有效且低成本的方法。利用功率器件的正向特性,可以檢測高器件電流導致較高飽和電壓或過渡到有源區(qū)域(雙極性器件)/飽和區(qū)域(單極性器件)的情況。因過流而關斷時,如果柵極電壓像在正常開關操作中一樣快速關斷,將出現高 di/dt。這與電源路徑中的寄生環(huán)路電感一起,會產生較高關斷 dV/dt,進而可能導致過壓應力,并可能損壞開關。當 DESAT 保護觸發(fā)時,軟關斷 (STO) 特性可降低功率器件上的應力。柵極驅動器中具有較低灌電流能力的額外 MOSFET (STO) 將激活,取代具有高灌電流能力的正常關斷晶體管。柵極放電電流減小,柵極電壓緩慢關斷,因此關斷 di/dt 和 dV/dt 較低。STO 功能不影響正常工作時的開關損耗。灌電流 MOSFET 和軟關斷 MOSFET 的典型飽和電流如圖 16(灌電流 MOSFET,QSink)和圖 17(軟關斷 MOSFET,QSTO)所示。圖 15 顯示 STO 激活時負載電容電壓緩慢下降。圖 18 是帶軟關斷功能的去飽和保護框圖,詳細時序圖參見數據表。

圖 16:內部灌電流 MOSFET (Qsink) 的典型飽和電流

圖 17:內部軟關斷 MOSFET (QSTO) 的典型飽和電流

圖 18:NCD(V)5700x 系列的去飽和保護示意圖

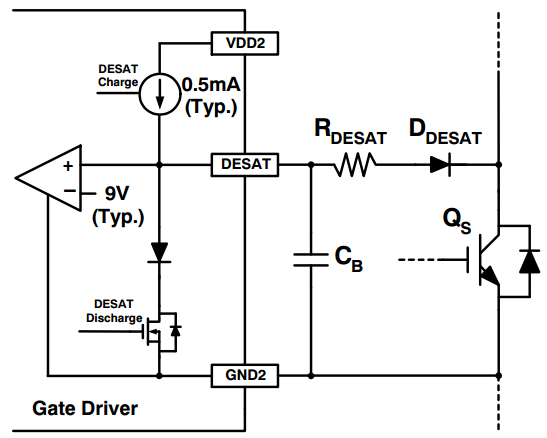

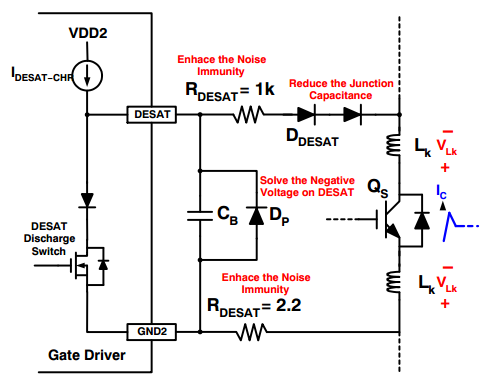

DESAT 保護電路仍需避免在功率器件導通的短瞬態(tài)時間內誤觸發(fā),以允許集電極/漏極電壓降至 DESAT 閾值以下。該瞬態(tài)持續(xù)時間稱為“DESAT 消隱時間 (tBlank)”。消隱時間由內部恒定充電電流源 (IDESAT-CHG )、DESAT 閾值電壓 (VDESAT-THR ) 和外部消隱電容 (CB) 控制。當輸入信號有效時,消隱電容由“DESAT 放電 MOSFET”進行放電,從而輸出低電平,然后在下一個導通周期復位消隱時間。典型應用電路如圖 19 所示。

圖 19:典型去飽和保護應用電路

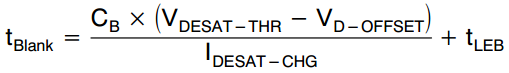

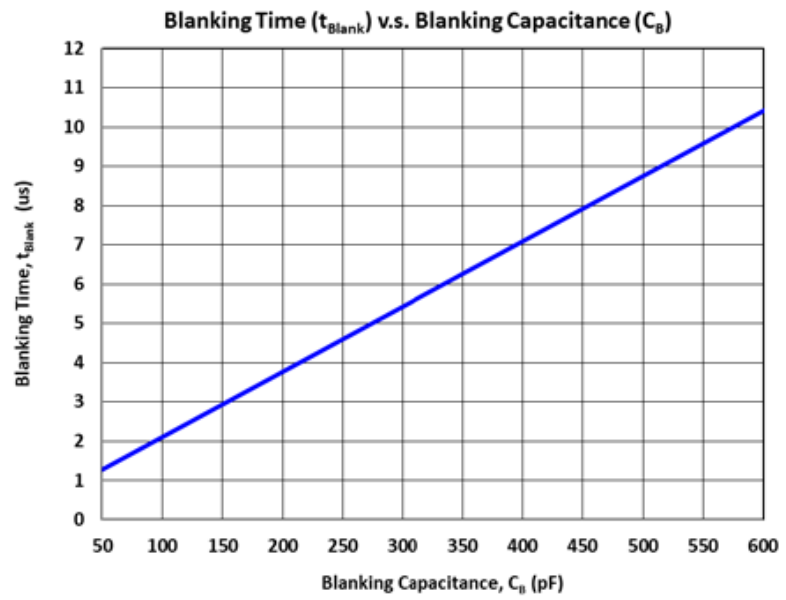

消隱時間公式如公式5 所示,其中包括前沿消隱;消隱時間與消隱電容的關系如圖 20 所示。

(公式5)

(公式5)

其中:

VDESAT?THR = 9 V(典型值)

VD?OFFSET = 0.7 V(典型值)

IDESAT?CHG = 0.5 mA(典型值)

tLEB= 450 ns(典型值)

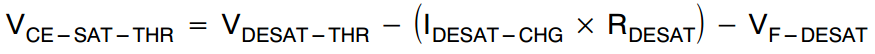

在穩(wěn)態(tài)下,DESAT 至 GND2 的電壓為以下電壓之和:電阻 (RDESAT) 上的電壓、二極管 (DDESAT) 的正向電壓和功率器件的飽和電壓 (VCE-SAT)。功率器件飽和電壓的觸發(fā)閾值 (VCE-SAT-THR) 可以計算如下:

(公式6)

(公式6)

圖 20:NCD(V)5700x 系列的消隱時間 (tBlank) 與消隱電容 (CB) 的關系

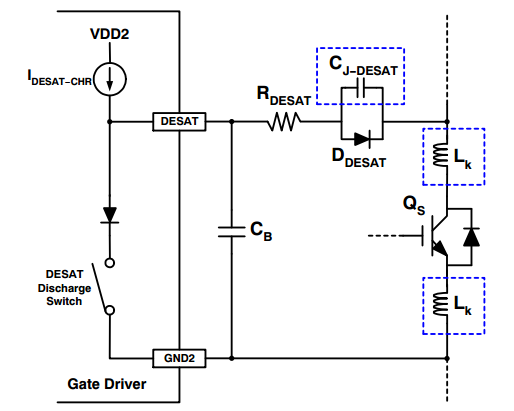

由于該檢測環(huán)路中的一些寄生元件的原因,DESAT 保護可能會誤觸發(fā),或者觸發(fā)電流值意外地與計算值不一致。圖 21 顯示了去飽和模塊二極管的結電容 (CJ-DESAT) 和電源環(huán)路中的寄生電感 (Lk);當應用 DESAT 保護時,電路需要考慮這些元件。

圖 21:考慮去飽和保護電路中的寄生元件

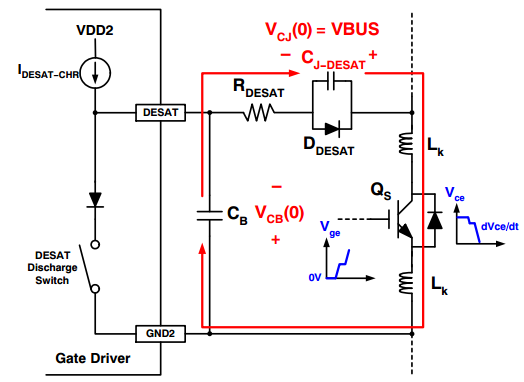

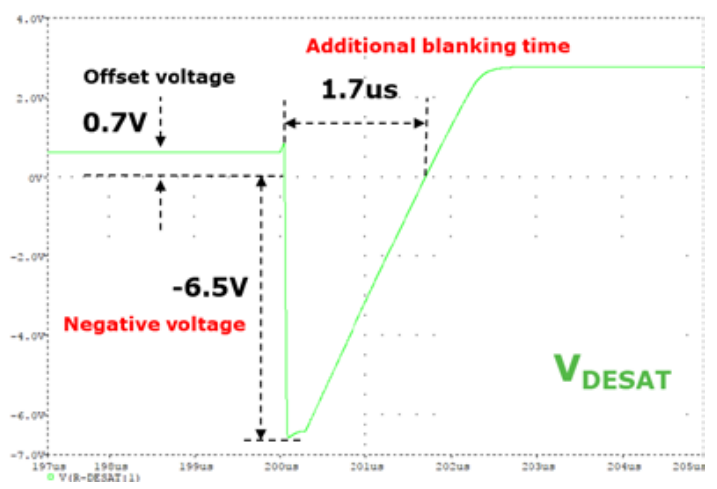

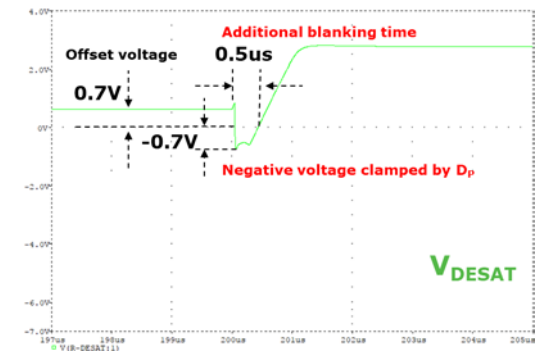

DESAT 上負電壓的機制主要是由于 CJ-DESAT 的放電。此負電壓的原理如圖 22 所示。在 QS 開關關斷狀態(tài)下,DDESAT 結電容 (CJ-DESAT) 的電壓接近 BUS 電壓,因為 DESAT 放電開關導通以使 DDESAT 能夠承受 BUS 電壓。結電容儲存的能量 ECJ-DESAT = 1/2 CJ-DESAT VBUS 2。當 QS 導通時,CJ-DESAT 放電,其能量傳輸到消隱電容 CB,導致 CB 上出現負電壓。如果結電容的值高于消隱電容的值,則消隱電容的負電壓將更高,因為來自結電容的能量更多。該負電壓會由 IDESAT-CHG電流源快速恢復,直至達到正電壓并跟隨 IGBT 的飽和電壓。如果不通過調整消隱電容值來應對,可能會延長去飽和觸發(fā)功能的延遲時間,導致 IGBT 的短路峰值電流更高。圖 23 顯示了以 GND2 為基準的 DESAT 電壓的仿真結果。NCD(V)5700x 系列 DESAT 引腳的設計可承受高達 -9 V 的負電壓而不會損壞 IC。

圖 22:當 Qs 導通且 DESAT 放電開關關斷時

圖 23:Qs 導通期間的 DESAT 波形(仿真)

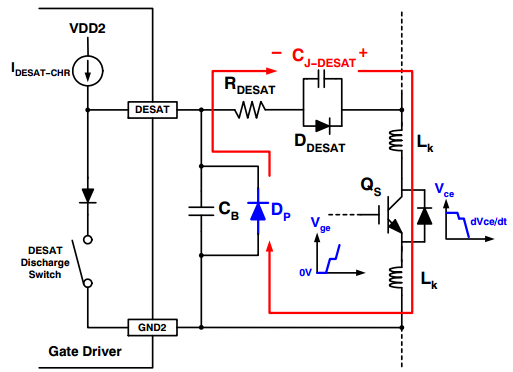

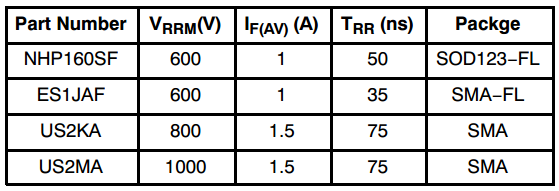

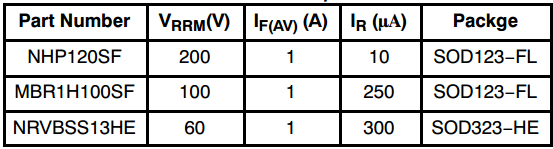

如果需要外部負電壓保護,保護二極管 Dp 可與消隱電容并聯。此二極管可以限制負電壓,并改善延遲時間。圖 24 和圖 25 顯示了使用保護二極管的電路和仿真結果。基于此分析,去飽和模塊二極管 (DDESAT) 應具有低結電容值和快速反向恢復性能。保護二極管 (Dp) 應具有低正向電壓和低漏電流。建議使用的 DDESAT 和 Dp 二極管如表 2 和表 3 所示。

圖 24:DESAT 和 GND2 之間使用保護二極管 (Dp)

圖 25:使用保護二極管時 Qs 導通期間的 DESAT 波形(仿真)

表 2:去飽和保護模塊二極管 (D-DESAT)

表 3:保護二極管 (Dp)

注意:VR < 20 V 時的漏電流,Ta = 125°C 或 150°C

布置保護二極管時,需要考慮額外結電容和漏電流對消隱時間的影響。基于功率整流器或 IGBT 關斷的反向恢復電流所帶來的 dIc/dt,功率路徑寄生電感將產生高頻電壓 (VLk)。此高頻噪聲可能通過去飽和引腳和 GND2 注入柵極驅動器。去飽和電阻 (RDESAT) 值如果足夠大,可以抑制這種情況,使該噪聲電流進入電源環(huán)路,而不是檢測環(huán)路。一般而言,RDESAT 建議使用大約 1 kΩ 和 2.2 Ω。如果因為使用快速切換功率器件而產生較高 dVCE/dt 或 dVds/dt,去飽和電阻還可以有兩個去飽和模塊二極管以降低總結電容。當然,如果因此導致去飽和模塊二極管和去飽和電阻上的正向電壓較高,則觸發(fā)閾值電壓也會改變。建議應用電路如圖 26 所示。

圖 26:改進去飽和保護的建議應用電路

理想的 DESAT 電壓波形圖和消隱時間設計概念如圖 27 所示。消隱和濾波時間之和必須小于功率器件的短路能力持續(xù)時間,以防止影響可靠性壽命,并且消隱時間應大于功率器件正常工作時的集電極/漏極電壓下降時間,以防止任何誤觸發(fā)。

圖 27:去飽和波形 (VDESAT) 圖和消隱時間設計概念

NCD(V)57000/57001 柵極驅動器設計涉及到很多設計技巧,很難在一篇文章中講述清楚。這篇中我們介紹了NCD(V)5700x的輸入(IN)和輸出(OUT)信號、輸入偏置電源(VDD1)、輸出正負偏置電源(VDD2和VEE2)、功耗(PD)和結溫(TJ)、欠壓閉鎖(UVLO)和就緒(RDY)和去飽和(DESAT)保護和軟關斷(STO)這六個部分的參數、功能和設計技巧。

下篇文章我們將重點關注NCD(V)5700x的考慮使用外部BJT緩沖器實現軟關斷(STO)、用于偏置電源的齊納分離式穩(wěn)壓器、柵極驅動電路中的箝位二極管、布局布線考慮等內容。

將安森美加入星標,下篇更新不容錯過~

原版文檔獲取點擊文末的“贊”和“在看”,并發(fā)送截圖和您的郵箱地址到后臺,即可領取原版文檔哦~

點個星標,茫茫人海也能一眼看到我

原文標題:工程師必須知道的大電流單通道柵極驅動器設計技巧

文章出處:【微信公眾號:安森美】歡迎添加關注!文章轉載請注明出處。

-

安森美

+關注

關注

32文章

1675瀏覽量

91997

原文標題:工程師必須知道的大電流單通道柵極驅動器設計技巧

文章出處:【微信號:onsemi-china,微信公眾號:安森美】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

淺談瑞盟科技·MS30517SA——單通道、高速、低側柵極驅動器

1.5A拉電流、2A 灌電流、5.7kVRMS光兼容單通道隔離式柵極驅動器UCC23511數據表

單通道、高速、低側柵極驅動器UCC2751x數據表

電隔離單通道柵極驅動器UCC21755-Q1數據表

電隔離單通道柵極驅動器UCC21710-Q1數據表

電隔離單通道柵極驅動器UCC21756-Q1數據表

10A拉電流和灌電流增強型隔離式汽車單通道柵極驅動器UCC21737-Q1數據表

電隔離單通道柵極驅動器UCC21738-Q1數據表

電隔離單通道柵極驅動器UCC21750-Q1數據表

具有4A峰值拉電流和8A峰值灌電流的單通道、高速、低側柵極驅動器UCC27511A數據表

電隔離單通道柵極驅動器UCC21732-Q1數據表

工程師必須知道的大電流單通道柵極驅動器設計技巧

工程師必須知道的大電流單通道柵極驅動器設計技巧

評論