本系列將帶來FPGA的系統性學習,從最基本的數字電路基礎開始,最詳細操作步驟,最直白的言語描述,手把手的“傻瓜式”講解,讓電子、信息、通信類專業學生、初入職場小白及打算進階提升的職業開發者都可以有系統性學習的機會。

系統性的掌握技術開發以及相關要求,對個人就業以及職業發展都有著潛在的幫助,希望對大家有所幫助。后續會陸續更新 Xilinx 的 Vivado、ISE 及相關操作軟件的開發的相關內容,學習FPGA設計方法及設計思想的同時,實操結合各類操作軟件,會讓你在技術學習道路上無比的順暢,告別技術學習小BUG卡破腦殼,告別目前忽悠性的培訓誘導,真正的去學習去實戰應用,這種快樂試試你就會懂的。話不多說,上貨。

按鍵控制LED

利用按鍵控制LED的要求為:按一下按鍵,改變一下LED的狀態。按鍵按一次,LED由熄滅變為點亮,按鍵再按一次,LED由點亮變為熄滅。

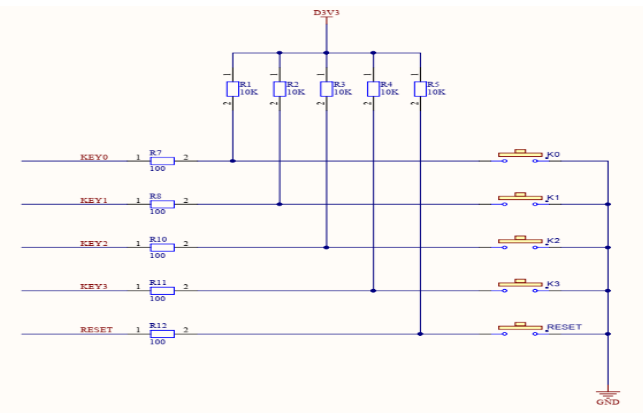

硬件介紹

開發板上面有四個按鍵,當按鍵按下時,將對應的網絡置成低電平;當按鍵釋放時,將對應的網絡置成高電平。

開發板上面有四個LED發光二極管,FPGA輸出高電平時,LED點亮;FPGA輸出低電平時,LED熄滅。

設計原理

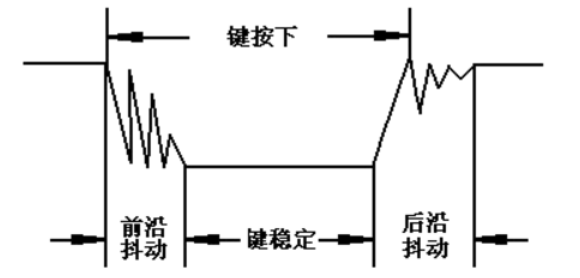

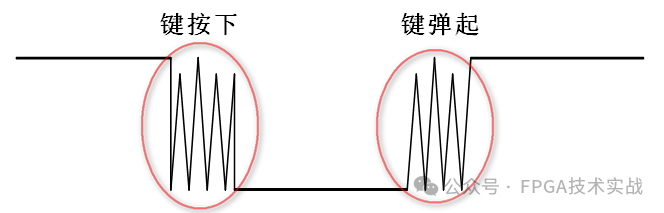

通常的按鍵所用開關為機械彈性開關,當機械觸點斷開、閉合時,由于機械觸點的彈性作用,一個按鍵開關在閉合時不會馬上穩定地接通,在斷開時也不會一下子斷開。因而在閉合及斷開的瞬間均伴隨有一連串的抖動。

按鍵抖動會引起一次按鍵被誤讀多次。為確保CPU對鍵的一次閉合僅作一次處理,必須去除鍵抖動。在鍵閉合穩定時讀取鍵的狀態,并且必須判別到鍵釋放穩定后再作處理。

抖動時間的長短由按鍵的機械特性決定,一般為5ms~10ms。這是一個很重要的時間參數,在很多場合都要用到。按鍵穩定閉合時間的長短則是由操作人員的按鍵動作決定的,一般為零點幾秒至數秒。

我們可以在按鍵和主控設備之間加入消抖電路(消抖芯片、電容等),此種方法會增大PCB面積和花費一定的物料費用。大多數的板子直接將按鍵和主控設備相連接,將帶有抖動的波形輸入到主控設備內部,由內部進行消抖處理。

單片機一般采用延遲重采樣的方式進行消抖。當檢測到信號為低時,延遲一段時間(一般為20ms),再次檢測信號是否為低,如果為低,則證明按鍵按下,否則認為按鍵沒有按下,繼續下一次檢查。

在FPGA設計時,筆者推薦另外一種方式:持續采樣。當檢測到信號持續為低10ms,認為按鍵按下;當檢測到信號持續為高10ms,認為按鍵釋放。

在設計時,需要考慮到外部的按鍵信號為異步信號,需要進行同步處理。具體請參考附錄2 FPGA中的同步信號、異步信號和亞穩態。

每次按鍵按下的時間的長短不一,經過消抖后,低電平的持續長度長短也不一樣。此長度遠遠大于一個時鐘周期的長度。要求每次按下只能夠切換一次LED的狀態,所以不能夠直接用此電平當做輸出翻轉的使能。

經過消抖的波形,每次按下只有一個下降沿(按鍵按下時)、只有一個上升沿(按鍵釋放時)。所以通過檢測下降沿(上升沿)的變化,產生一個新的信號------脈沖(一個時鐘周期的脈沖),利用此脈沖作為翻轉的使能即可。利用檢測到下降沿的脈沖翻轉時,LED的狀態會在按下時就會改變;利用檢測到上升沿的脈沖翻轉時,LED的狀態會在釋放時發生改變。本設計中采用檢測到下降沿的脈沖進行翻轉。

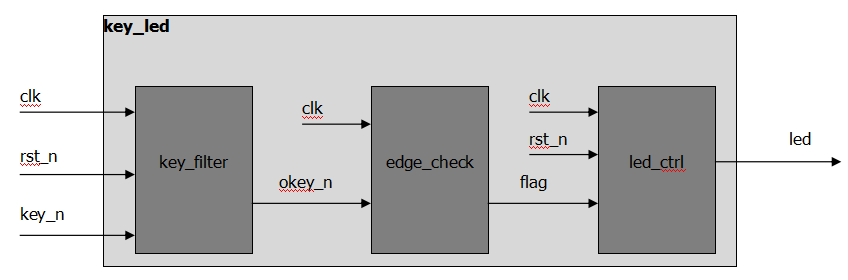

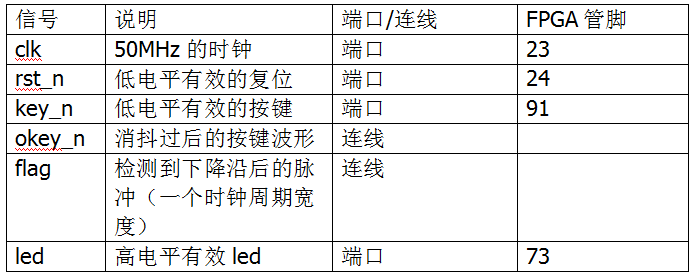

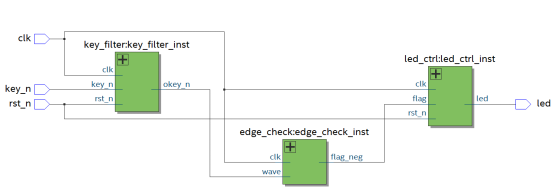

設計架構和信號說明

本設計模塊命名為key_led。

在設計中,共分為三個模塊。

key_filter(按鍵消抖模塊):將外部輸入的帶有抖動的波形進行消抖。

edge_check(邊沿檢測模塊):將消抖后的波形進行下降沿檢測,并產生對應的脈沖。

led_ctrl(led控制模塊):利用脈沖,翻轉led的輸出狀態。

key_filter設計實現

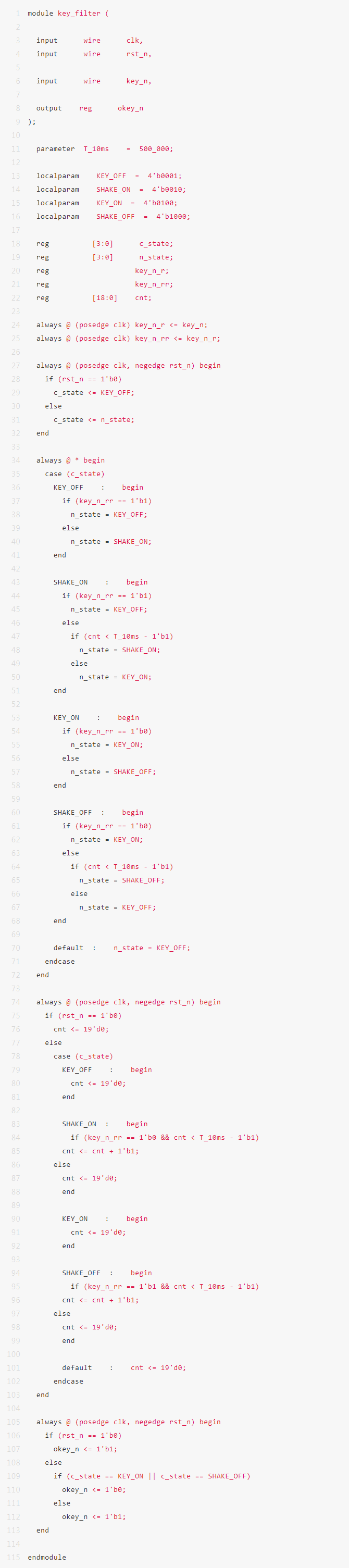

本設計采用狀態機實現,狀態機的具體原理請參看附錄3。

對key_n信號為異步信號,需要進行同步兩拍,命名為key_n_r和key_n_rr。狀態機的判斷信號為key_n_rr信號。

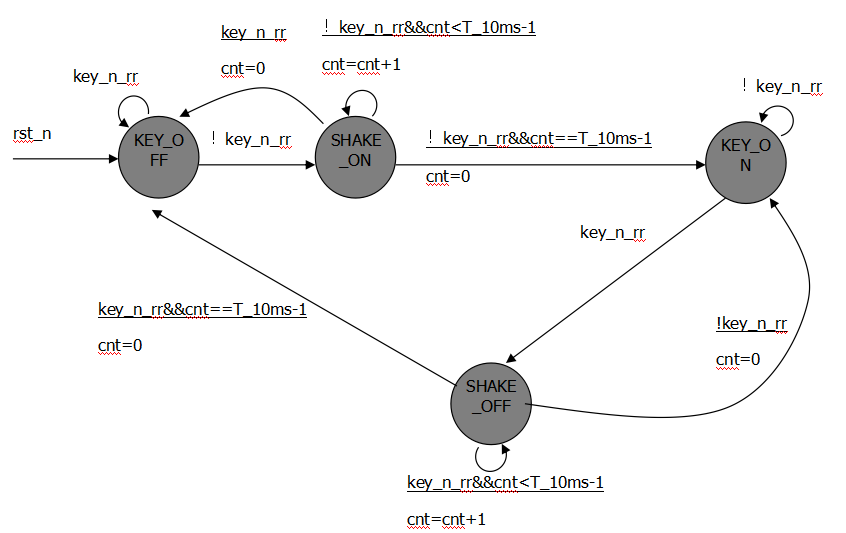

本設計共分為四個狀態,KEY_OFF(按鍵釋放狀態),SHAKE_ON(按鍵按下時抖動判斷狀態),KEY_ON(按鍵按下狀態),SHAKE_OFF(按鍵釋放時抖動判斷狀態)。

按鍵沒有按下時,一直KEY_OFF狀態,當按鍵信號變為低電平時,就轉入SHAKE_ON狀態,檢測低電平的持續時間。如果持續時間沒有達到T_10ms就變為高電平,則清零計數器并返回KEY_OFF狀態;如果持續時間沒有達到T_10ms并且也一直為低電平,則繼續在SHAKE_ON狀態計數;如果持續時間達到T_10ms并且為低電平,則清零計數器并進入KEY_ON狀態。在KEY_ON狀態,外部輸入為低電平時,則繼續在KEY_ON狀態;如果外部輸出為高電平,則轉入SHAKE_OFF狀態。在SHAKE_OFF狀態,如果持續時間沒有到達T_10ms就變為低電平,則清零計數器并返回KEY_ON狀態;如果持續時間沒有達到T_10ms并且一直為高電平,則繼續在SHAKE_OFF狀態計數;如果持續時間達到T_10ms并且一直為高電平,則清零計數器并轉入KEY_OFF狀態。

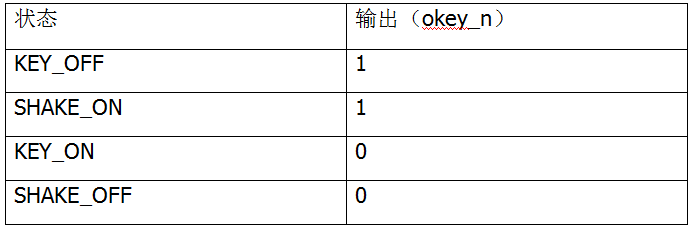

在KEY_OFF和SHAKE_ON狀態,認為按鍵沒有按下;在KEY_ON和SHAKE_OFF狀態,認為按鍵為按下。

狀態轉移圖如下:

設計代碼為:

localparam可以定義參數,與parameter的區別在于,parameter定義的參數可以在例化時進行參數修改,而localparam定義的參數在例化時則不能夠修改。定義狀態機狀態時,一般采用localparam的定義方式。在不希望別人修改參數時,也可以定義為localparam。

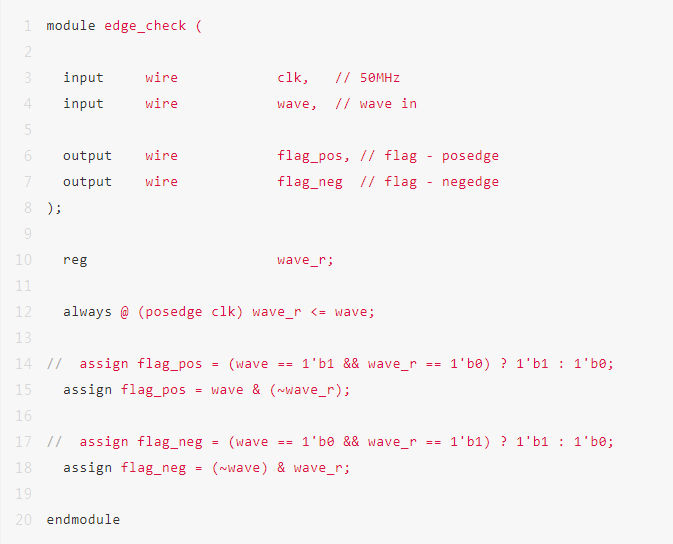

edge_check設計實現

在一個波形中,如果當前時刻為低電平,上一個時刻為高電平,則認為波形中有一個下降沿;如果當前時刻為高電平,上一個時刻為低電平,則認為波形中有一個上升沿。

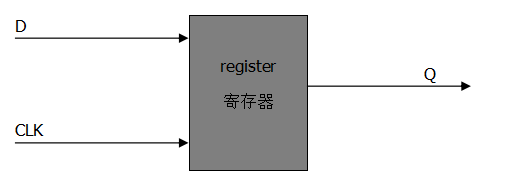

在數字電路設計時,可以采用寄存器來存儲上一個時刻的值。

在寄存器電路中,Q的值,永遠是上一個CLK的有效邊沿所采樣的D值。因此Q為上一時刻值,而D為當前時刻的值。

設計代碼為:

在設計中,注釋掉的兩行代碼和其下方的一行代碼的功能是相同的。例:對于上升沿脈沖來說,現在為1,過去為0即為上升沿。由于寄存器每個時鐘周期都刷新,滿足這個要求的只會存在一個時鐘周期,所以flag_pos為一個時鐘周期的脈沖。

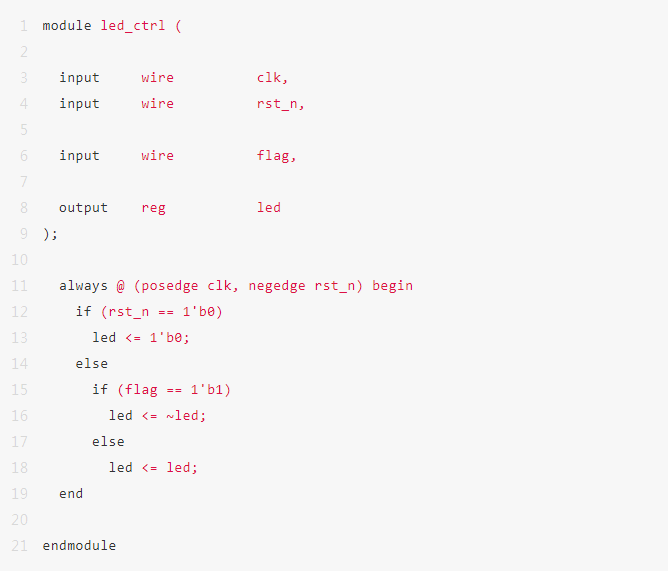

led_ctrl設計實現

本模塊中,利用脈沖進行led狀態的翻轉即可。

設計代碼為:

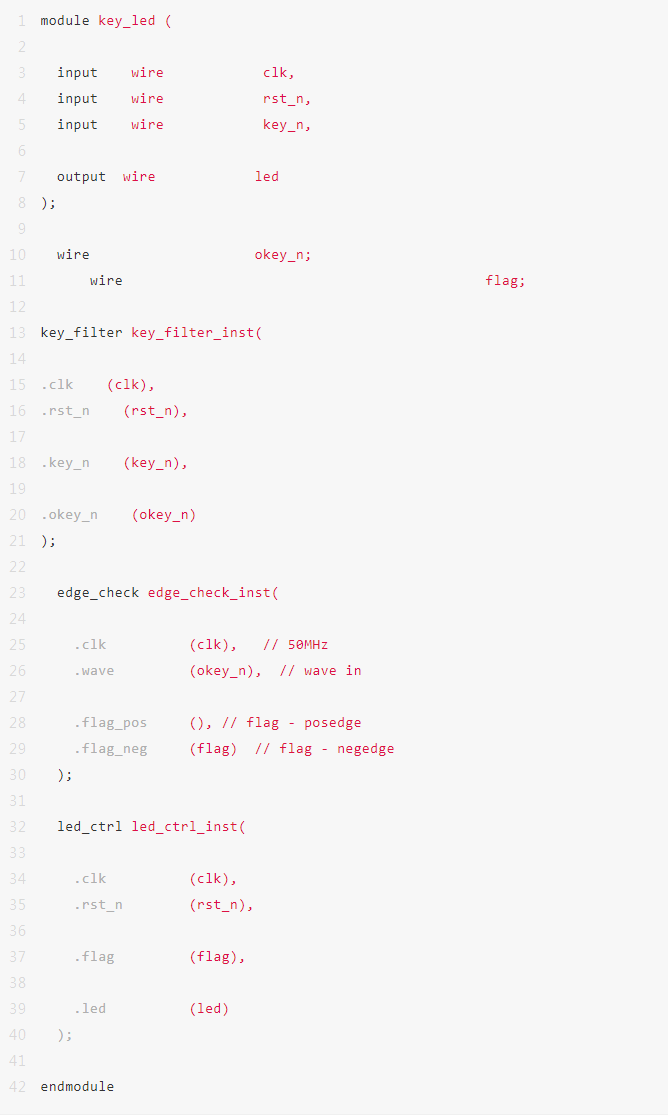

key_led設計實現

本模塊只是負責將上述的三個模塊按照架構圖的方式進行連接,形成最終的設計。

設計代碼為:

在設計中,采用了按鍵按下時的脈沖(檢測到下降沿的脈沖),按鍵按下時led的狀態即可進行翻轉。

功能仿真

在仿真時,將按鍵消抖中的T_10ms的參數修改為20,即持續時間不超過400ns都不認為是有效按下或者抬起。

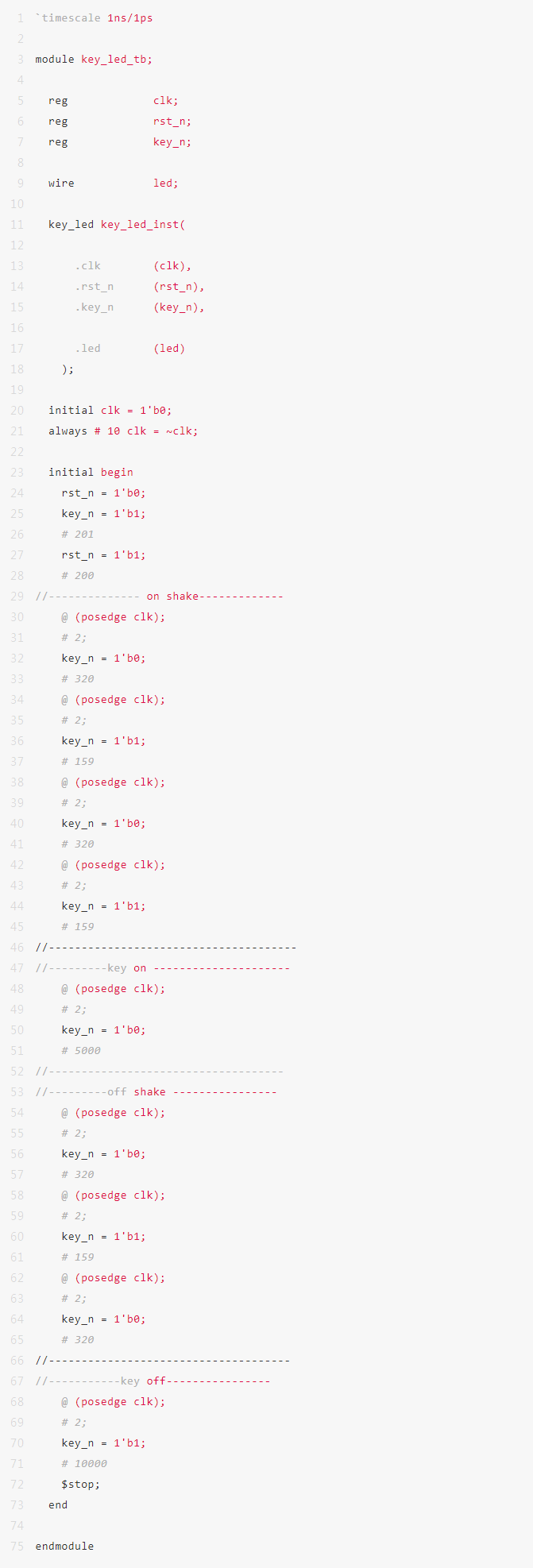

仿真代碼如下:

將okey_n、flag信號添加出來。

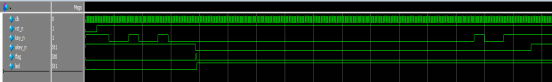

通過RTL仿真圖,可以清晰的看到okey_n信號將key_n的抖動濾除掉;flag信號為okey_n信號的下降沿時所產生的脈沖;led在flag信號為高時,反正翻轉。

分配管腳、下板測試之前,應該將按鍵消抖里面的T_10ms參數重新改為500_000,否則下板后可能會達不到消抖的效果。

下板成功后,可以修改在設計中使用上升沿的脈沖,得到的現象應該是按鍵釋放時,LED的狀態發生反轉。

切記:每次修改代碼,一定要進行重新編譯,否則更改將不會生效。

更多熱點文章閱讀

-

電子技術

+關注

關注

18文章

894瀏覽量

56104 -

電子發燒友論壇

+關注

關注

4文章

197瀏覽量

1112

原文標題:【教程分享】 FPGA零基礎學習:按鍵控制LED

文章出處:【微信號:gh_9b9470648b3c,微信公眾號:電子發燒友論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

告別繁瑣按鍵,雙觸摸LED讓你輕松調光調色!

零基礎嵌入式開發學習路線

基于FPGA實現按鍵消抖處理

【xG24 Matter開發套件試用體驗】通過按鍵控制LED

如何在FPGA中實現按鍵消抖

【xG24 Matter開發套件試用體驗】7-按鍵點亮LED

兩片stm8s實現can通信,發送端通過按鍵控制接受端的pwm應該怎么寫?

【紫光同創盤古PGX-Nano教程】——(盤古PGX-Nano開發板/PG2L50H_MBG324第三章)鍵控流水燈實驗例程

【紫光同創盤古PGX-MINI-4K教程】——(盤古PGX-MINI-4K開發板/PGC4KD-6ILPG144第三章)鍵控彩燈實驗例程

【紫光同創盤古PGX-Lite 7K教程】——(盤古PGX-Lite 7K開發板/PGC7KD-6IMBG256第三章)?鍵控彩燈實驗例程

32無法正常控制繼電器開關水泵或電機

從入門到放棄……為什么你會覺得FPGA難學?如何學習FPGA?

【教程分享】 FPGA零基礎學習:按鍵控制LED

【教程分享】 FPGA零基礎學習:按鍵控制LED

評論