Sanjay Rajasekhar 和 Arvind Shankar

在多路復用(muxed)逐次逼近寄存器模數(shù)轉換器(SAR ADC)應用中,一般會有尺寸和功耗限制,這通常取決于每通道模擬信號鏈的設計選擇。本文說明為什么采用模擬輸入高阻(高阻抗)技術的多路復用SAR ADC是在不影響性能和精度的情況下大幅減小解決方案尺寸和降低功耗的關鍵。

引言

多路復用SAR ADC通常用于需要不斷監(jiān)測系統(tǒng)中多個關鍵變量的應用。在光通信應用中,可以通過光功率測量監(jiān)測激光偏壓,而在VSM應用中可以監(jiān)測來自電極的EEG/ECG信號。這些多路復用應用有一些共同的要求:

有很多通道需要監(jiān)測。一般來說,ADC會按順序監(jiān)測所有通道。

通道電壓通常彼此不相關。

在系統(tǒng)尺寸和功耗方面存在嚴格的限制。

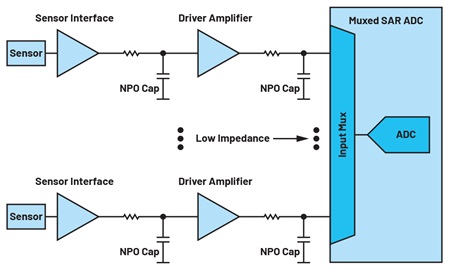

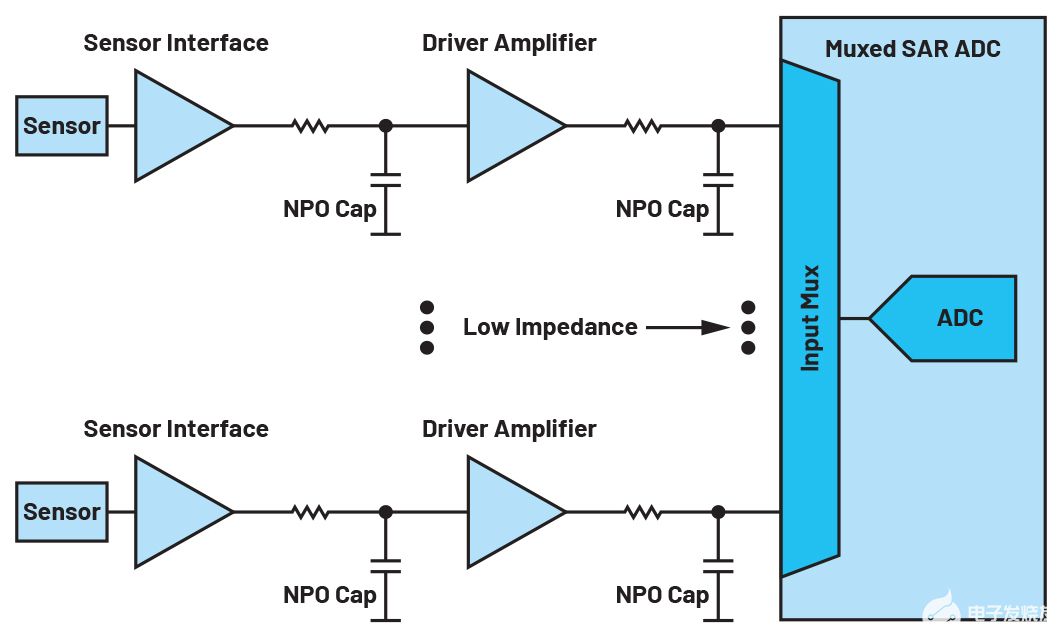

由于上述這些要求,設計人員會面臨一些挑戰(zhàn)。當ADC在一個通道上完成轉換時,ADC內(nèi)的采樣電容會充電至該通道電壓。如果采樣電容的電壓與序列中下一個通道的電壓相差很大,則必須通過信號鏈設計,使采樣電容能夠在允許的采樣時間內(nèi)準確地穩(wěn)定在新電壓。過去通常是使用一個寬帶驅(qū)動放大器,再配合一個RC濾波器來解決這個問題。典型的信號鏈如圖1所示。

圖1. 采用傳統(tǒng)多路復用SAR ADC的信號鏈。

傳感器可以輸出電壓或電流,而傳感器接口電路可以分別是一個儀表放大器或一個互阻抗放大器。電容通常為NP0/C0G型,因為其它類型的電容會造成明顯的失真。NP0電容線性度高,但密度低。選用的NP0電容也要比ADC內(nèi)部采樣電容的值大得多。它執(zhí)行兩個關鍵功能:

減少ADC采樣電容的反沖

濾除所需穩(wěn)定帶寬以外的噪聲,從而降低信號鏈的寬帶噪聲

在傳統(tǒng)的信號鏈中,每個通道必須使用驅(qū)動放大器和大電容。每個驅(qū)動放大器的功耗在零點幾毫安到幾毫安之間。每個電容(包括間隙)可能占據(jù)約1 mm2的電路板面積。如果多個通道都采用這種信號鏈,將非常不利于減小系統(tǒng)尺寸和降低功耗。這是當今多路復用SAR ADC應用中的主要問題之一。

什么是輸入高阻技術?

就模擬輸入而言,高阻技術是指一組電路技術,可在不消耗靜態(tài)或連續(xù)功率的情況下,大幅提高ADC的有效輸入阻抗。這使得ADC的輸入易于驅(qū)動。

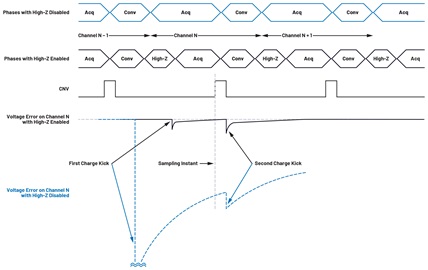

假設多路復用ADC正在通道N–1上轉換,下一個要轉換的通道是通道N。

在轉換啟動(CNV)的上升沿,對通道電壓進行采樣。在圖2中,CNV的第一個上升沿對通道N - 1的電壓進行采樣。然后ADC對通道N - 1上的采樣電壓進行轉換。轉換后,在禁用輸入高阻的情況下,ADC繼續(xù)獲取序列中的下一個通道,即通道N。通道N上的電壓通常與通道N–1上的電壓大不相同,此時要對ADC電容充電,達到通道N的電壓水平。這會在通道N(深藍色虛線)上產(chǎn)生巨大的電壓沖擊,并在采樣瞬間(CNV的第二上升沿)在通道電壓中引入較大誤差。因此需要一個較大的外部電容來吸收沖擊,并且需要一個驅(qū)動放大器來提供必要的電荷。

圖2. 啟用和禁用高阻功能時AD4696的相位。

當啟用輸入高阻時,會對ADC的內(nèi)部采樣電容充電,使其達到將要采集通道的當前電壓水平,然后開始真正的電壓采樣。在通道N–1上進行轉換后,立即引入高阻相位,將ADC采樣電容精確充電到通道N的當前電壓水平。這意味著,當ADC采樣電容連接到外部輸入時,它不會提供任何電荷,也不會導致任何反沖。在實踐中,由于內(nèi)部開關的電荷注入(第一次電荷沖擊),通常會有較小的殘余誤差。這種微小的殘余誤差使得通道N采樣瞬間的穩(wěn)定誤差幾乎可以忽略不計。在啟用高阻的情況下,這個電荷誤差將明顯改善系統(tǒng)的穩(wěn)定動態(tài)。

當通道N的采樣完成后,ADC必須繼續(xù)進行轉換。因此,內(nèi)部開關將ADC的采樣電容與外部輸入斷開。由于開關打開電荷注入,這會導致第二次電荷沖擊。通常情況下,第二次電荷沖擊的穩(wěn)定時間較長,所以第一次電荷沖擊的幅度決定了通道的穩(wěn)定誤差。因此,必須盡可能減小第一次電荷沖擊的幅度。

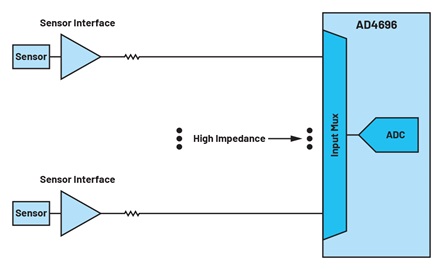

AD4696(新一代多路復用SAR ADC)采用了輸入高阻技術,作為EasyDrive?功能集的一部分。因此,AD4696在通道上開始電壓采樣時非常平穩(wěn)。每個通道不再需要反沖吸收電容和驅(qū)動放大器。這使得系統(tǒng)尺寸和功耗大幅減少,并且信號鏈明顯簡化,如圖3所示。

圖3. 采用AD4696多路復用SAR ADC的信號鏈。

在AD4696系列中實現(xiàn)輸入高阻有一個重要優(yōu)勢,就是執(zhí)行高阻功能的電路都可以按轉換速率進行循環(huán)上電。因此,高阻功能的功耗將與ADC的吞吐量成線性比例,就像核心SAR ADC本身一樣。與刻板的傳統(tǒng)信號鏈設計相比,這具有明顯的靈活性。

AD4696的 LTspice?模型 中也內(nèi)置了輸入高阻功能。對第一次和第二次電荷沖擊進行了精確建模,從而能夠可靠地仿真信號鏈設計中的穩(wěn)定偽影。

一些細節(jié)

回顧一下會發(fā)現(xiàn),NP0電容還提供了信號鏈的寬帶噪聲濾波。如果想去除這個電容,就必須找到其它方法來濾除噪聲。實現(xiàn)相同的有效信號鏈噪聲帶寬的一個簡單方法是增加外部串聯(lián)電阻。AD4696有一個60 pF的內(nèi)部電容,與一個240 Ω的典型內(nèi)部電阻串聯(lián)。通過設置外部電阻,我們可以將信號鏈噪聲帶寬調(diào)整到目標值。

在沒有NP0電容的情況下,外部電阻對信號鏈的噪聲性能、線性度和精度起著重要作用。小阻值電阻有助于快速穩(wěn)定采樣電荷沖擊,從而提高線性度和精度,但更高的有效噪聲帶寬會導致整體噪聲增加。相反,大阻值電阻可以更好地濾除噪聲,但線性度和精度會降低。

正如下一節(jié)所述,AD4696采用高阻技術的主要優(yōu)勢,就是它允許使用大阻值電阻(從而實現(xiàn)更好地濾除噪聲),且不會降低線性度和精度。它支持對信號鏈中的所有參數(shù)進行優(yōu)化,包括噪聲、線性度、精度、功耗和解決方案尺寸。

測量結果

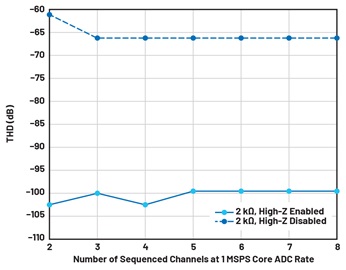

在沒有任何NP0電容的情況下,用一個2 kΩ的外部電阻進行測量。結果顯示,在啟用模擬輸入高阻的情況下,交流和直流性能得到了大幅改善。實驗中以1 MSPS的速度運行AD4696的核心ADC,但選擇了更多的通道作為輪詢序列的一部分。數(shù)據(jù)都在一個通道上收集,而序列中其它通道的輸入電壓為0 V。

圖4顯示了1 kHz、-1 dBFS信號音下相關信道的失真性能。當通道在禁用高阻的情況下進行排序時,由于采樣電容未充電到后續(xù)通道的電壓水平,因此會出現(xiàn)非線性穩(wěn)定誤差。這會導致嚴重失真。啟用高阻后,失真性能有了很大的改善。

圖4. THD與序列中通道數(shù)的關系。測試音:1 kHz, –1 dBFS。

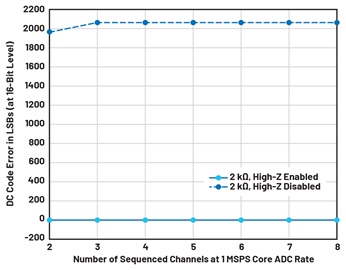

圖5顯示了有和沒有高阻功能的直流穩(wěn)態(tài)建立誤差。在這個測試中,相關的通道具有接近滿量程的輸入值,序列中的其它通道驅(qū)動電壓為0 V。在相關通道上進行轉換,同時將越來越多的通道添加到序列中,并繪制出平均輸出代碼與預期代碼的偏移。

圖5. 16位電平LSB中的直流穩(wěn)定誤差。

當核心ADC以低于1 MSPS的吞吐量運行時,用戶可能需要進一步降低有效的信號鏈噪聲帶寬,來限制模擬前端噪聲混疊。這將需要更高的電阻值,而高阻功能非常有助于在這些條件下保持性能。

結論

AD4696系列產(chǎn)品采用輸入高阻技術為多路復用SAR應用帶來了很大的優(yōu)勢,比如降低系統(tǒng)級功耗、減小尺寸和減少元件數(shù)量等,同時保持高水平的交流性能和直流精度。這樣每個通道不再需要專用驅(qū)動放大器和反沖吸收電容。高阻功能本身的功耗與ADC的吞吐量成比例,為系統(tǒng)級設計提供了良好的靈活性和多功能性。AD4696的LTspice模型可用于仿真用戶希望設計的任何系統(tǒng)中電荷沖擊的影響。

審核編輯:郭婷

-

放大器

+關注

關注

143文章

13583瀏覽量

213368 -

SAR

+關注

關注

3文章

416瀏覽量

45950 -

adc

+關注

關注

98文章

6495瀏覽量

544467

發(fā)布評論請先 登錄

相關推薦

新ESD技術減小芯片的I/O尺寸

減小隔離式同步柵極驅(qū)動器的尺寸并降低復雜性的方案

集成多路復用輸入ADC解決方案減輕功耗和高通道密度的挑戰(zhàn)

集成多路復用輸入ADC解決方案減輕功耗和高通道密度的挑戰(zhàn)

基于LTC7821設計可使DC-DC轉換器解決方案的尺寸減小50%

如何利用FPGA滿足電信應用中的降低功耗要求?

高功率硅開關怎么降低功耗和縮減尺寸

集成多路復用輸入ADC解決方案減輕功耗和高通道密度的挑戰(zhàn)

實現(xiàn)降低FPGA設計的動態(tài)功耗的解決方案

基于全新隔離技術的高電壓系統(tǒng)解決方案

高功率密度的解決方案

減小嵌入式SoC尺寸的解決方案

如何利用輸入高阻態(tài)技術降低解決方案功耗和尺寸

如何利用輸入高阻技術來降低解決方案的功耗并減小尺寸

如何利用輸入高阻技術來降低解決方案的功耗并減小尺寸

評論