Richard Houlihan, Naveen Dhull , 和 Padraig Fitzgerald

先進的數字處理器IC要求通過單獨的DC參數和高速數字自動測試設備(ATE)測試,以達到質保要求。這帶來了很大的成本和組織管理挑戰。本文介紹 ADGM1001 SPDT MEMS開關如何助力一次性通過單插入測試,以幫助進行DC參數測試和高速數字測試,從而降低測試成本,簡化數字/RF片上系統(SoC)的測試流程。

ATE挑戰

半導體市場在不斷發展,為5G調制解調器IC、圖像處理IC和中央處理IC等先進的處理器提供速度更快、密度更高的芯片間通信。在這種復雜性不斷提高、需要更高吞吐量的形勢下,保證質量成為如今的ATE設計人員面臨的終極挑戰。一個關鍵方面是:發射器(Tx)/接收器(Rx)通道數量不斷增加,需要進行高速數字和DC參數測試。這些挑戰導致半導體測試越來越復雜,如果不加以解決,會導致測試時間更長、負載板更復雜和測試吞吐量下降。而在現代ATE環境中,這會導致運營費用(OPEX)增加,產出降低。

要解決這些ATE挑戰,需要使用能在DC頻率和高頻率下運行的開關。ADGM1001能傳輸真正的0 Hz DC信號,以及高達64 Gbps的高速信號。這讓我們得以構建高效的單個測試平臺(一次插入),可配置為測試DC參數標準和高速數字通信標準,例如PCIe Gen 4/5/6、PAM4和USB 4。

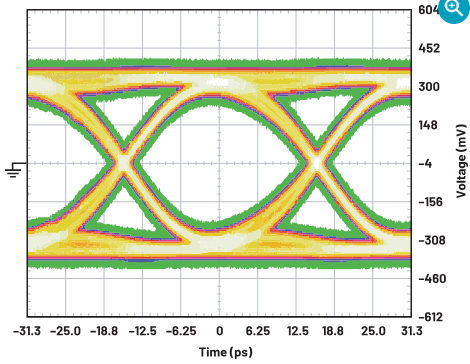

圖2.ADGM1001眼圖,32 Gbps(RF1至RFC,包含參考波形,使用的偽隨機測試碼PRBS 215-1)。

如何測試HSIO引腳?

在高產量生產環境中測試高速輸入輸出(HSIO)接口是一大挑戰。驗證HSIO接口的一種常見方法是采用高速環回測試結構。這會將高速測試路徑和DC測試路徑集成在同一個配置中。

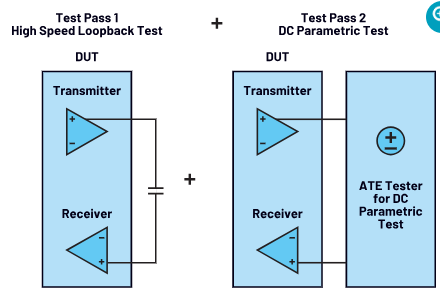

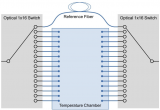

要執行高速環回測試,通常從發射器高速發射一個偽隨機位序列(PRBS),在負載板或測試板上環回之后由接收器接收,如圖3(左側)所示。在接收端,對序列進行分析,以計算誤碼率(BER)。

DC參數測試(例如連續性和泄漏測試)在I/O引腳上進行,以確保器件功能正常。要執行這些測試,需要將引腳直接連接到DC儀器上,用該儀器施加電流并測量電壓,以測試故障。

要在DUT I/O上執行高速環回測試和DC參數測試,可以使用多種方法來測試數字SoC;例如,使用MEMS開關或繼電器,或使用兩種不同類型的負載板,一種用于執行高速測試,另一種用于執行DC測試,這需要兩次插入。

使用繼電器執行高速測試和DC參數測試變得很有挑戰性,因為大多數繼電器的工作頻率不超過8 GHz,因此用戶必須在信號速度和測試范圍方面做出讓步。此外,繼電器體積大,會占用很大的PCB面積,這會影響解決方案的尺寸。繼電器的可靠性一直備受關注,它們通常只能支持1000萬個開關周期,這限制了系統的正常運行時間和負載板的壽命。

圖3顯示用于執行高速環回測試和DC參數測試的兩種插入測試方法。圖3中,左側顯示高速數字環回測試設置,其中DUT的發射器通過耦合電容接至接收器。圖3右側顯示DC參數測試設置,其中DUT引腳直接連接至ATE測試儀進行參數測試。到目前為止,受組件限制,還無法在同一個負載板上同時提供高速環回功能和DC測試功能。

圖3.兩種插入測試方法的示意圖。

與兩次插入測試相關的挑戰

管理兩套硬件:用戶必須維護和管理進行DC和環回測試所需的兩套負載板。這使成本大幅增加,尤其是在測試大量器件時。

延長測試時間,增加測試成本:兩次插入測試意味著每個DUT必須測試兩次,因此每次測試的索引時間將增加一倍,最終會增加測試成本,并顯著影響測試吞吐量。

測試時間優化:使用兩套硬件時,測試時間無法優化。如果一個器件導致第二次插入失敗,成本會進一步增加。第一次插入則會浪費測試儀時間。

更易出現操作錯誤:由于每個DUT都要測試兩次,出現操作錯誤的幾率也會翻倍。

解決方案設置× 2:兩種測試插入方法涉及兩組硬件,使得硬件設置時間翻倍。

組織管理成本:兩次插入測試,意味著需要移動更多組件。需要在兩個測試儀之間,甚至兩個測試室之間移動組件,帶來了規劃和組織管理挑戰。

ADI公司的DC至34 GHz開關技術如何利用出色密度解決兩次插入問題

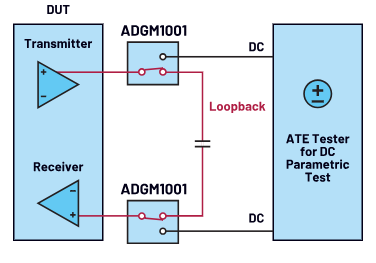

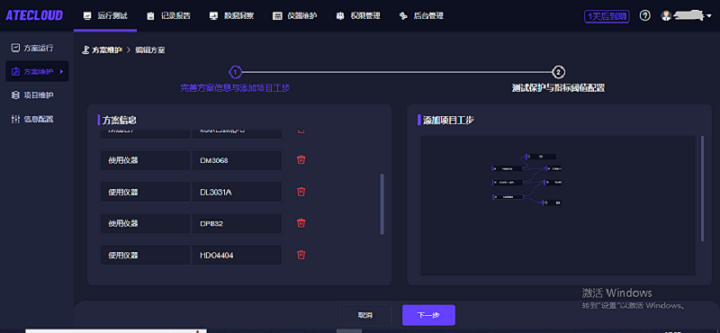

ADI公司的34 GHz MEMS開關技術采用小巧的5 mm × 4 mm × 0.9 mm LGA封裝,提供高速數字測試功能和DC測試功能,如圖4所示。要執行高速數字測試,來自發射器的高速信號經由開關,路由傳輸回到接收器,在解碼之后,進行BER分析。要執行DC參數測試,該開關將引腳連接到DC ATE測試儀進行參數測試,例如連續性和泄漏測試,以確保器件功能正常。在執行DC參數測試期間,MEMS開關還提供與ATE進行高頻通信的選項,可以滿足某些應用的需求。

圖4.ADGM1001支持高速數字測試和DC測試(只突出顯示P通道)。

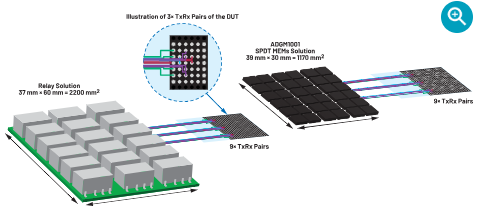

圖5顯示高速數字測試解決方案,分別使用繼電器和使用ADGM1001 MEMS開關進行比較。使用MEMS開關時,解決方案的尺寸比使用繼電器時縮減近50%,這是因為ADGM1001采用5 × 4 × 0.9 mm LGA封裝,比典型的繼電器小20倍。PCIe Gen 4/5、PAM4、USB 4和SerDes等高頻標準驅動多個發射器和接收器通道,這些通道需要緊密排布在PCB上,但不能增加布局復雜性,以消除通道與通道之間的差異。為了滿足這些不斷發展的高頻標準的要求,MEMS開關在負載板設計中提供致密和增強功能,以便執行數字SoC測試。

圖5.分別使用繼電器和ADGM1001的環回解決方案比較。

繼電器尺寸通常很大,只能提供有限的高頻性能。它們利用增強致密來支持更高的頻率標準,例如PCIe Gen 4/5、PAM4、USB 4和SerDes。大多數繼電器的工作頻率不超過8 GHz,在高頻率下具有很高的插入損耗,會影響信號的完整性并限制測試覆蓋范圍。

ADGM1001簡介

ADGM1001 SPDT MEMS開關在DC至34 GHz頻率范圍內提供出色的性能。該技術具有超低寄生效應和寬帶寬,開關對高達64 Gbps信號的影響很小,并且通道偏斜、抖動和傳播延遲都比較低,可實現高保真數據傳輸。它在34 GHz時提供1.5 dB的低插入損耗和3 ?低RON。它提供69 dBm的良好線性度,可以處理高達33 dBm的RF功率。它采用5 mm × 4 mm × 0.95 mm小型塑料SMD封裝,提供3.3 V電源和簡單的低壓控制接口。所有這些特性使ADGM1001非常適合ATE應用,支持通過單次測試插入實現高速數字測試和DC參數測試,如圖4所示。

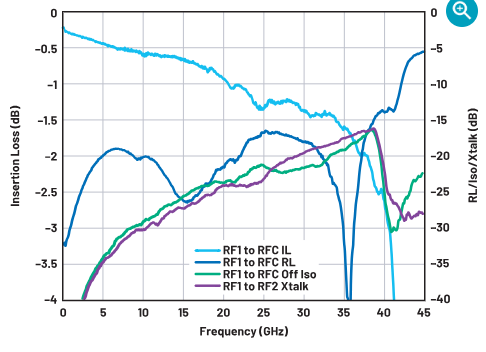

圖6.ADGM1001 RF性能。

圖7.封裝類型:5 mm × 4 mm × 0.9 mm 24引腳LGA封裝。

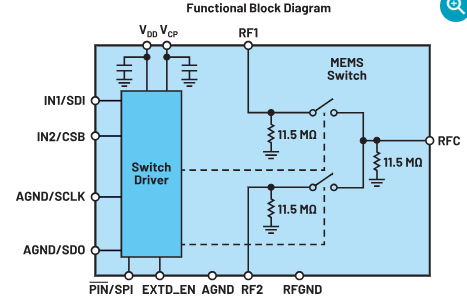

ADGM1001易于使用,為引腳23提供3.3 V VDD即可運行。但是,VDD可以使用3.0 V至3.6 V電壓。開關可以通過邏輯控制接口(引腳1至引腳4)或通過SPI接口進行控制。實現器件功能所需的所有無源組件都集成在封裝內,易于使用并且節省板空間。圖8所示為ADGM1001的功能框圖。

圖8.ADGM1001功能框圖。

使用ADGM1001實現單次插入測試的優勢

出色的高速和DC性能:實現從DC到34 GHz的寬帶寬是當今行業面臨的挑戰。ADGM1001的插入損耗、線性度、RF功率處理和RON等關鍵參數在DC到34 GHz范圍內都具有出色的性能。

降低運營費用:

減少硬件數量:單次插入測試只需使用一套測試硬件;因此,用戶無需投資購買兩套硬件和測試設備,可以大幅降低運營費用。

測試儀的運行時間:與繼電器相比,ADGM1001支持1億個循環周期,提供出色的可靠性,可延長測試儀的運行時間,最終降低運營費用。

提高測試吞吐量:ADGM1001允許使用單次插入測試,將索引時間減少一半,這會大幅縮短測試時間,提供更高的測試吞吐量和資產利用率。

密集解決方案,面向未來:ADGM1001提供更高的致密度和增強功能。MEMS開關技術提供可靠的路線圖,適用于DC至高頻運行開關,且與不斷發展的技術完全保持一致。

降低組織管理成本:使用單次插入方法時,需要移動的組件數量更少,可以降低組織管理成本和規劃難度。

減少組件移動:使用單次插入測試方法時,DUT只需一次插入進行測試,減少了組件移動,最終可降低發生操作錯誤的幾率。

結論

ADGM1001正在推動DC至34 GHz開關技術的發展,使得組合使用高速數字和DC參數解決方案進行SoC測試成為可能。它有助于縮短測試時間,改善電路板設計布局(實現更高的DUT數量和吞吐量),并延長運行時間(提高可靠性)。

ADGM1001是ADI MEMS開關系列的新產品,繼續推動滿足高速SoC測試需求。ADI公司的MEMS開關技術擁有可靠的發展路線,支持DC至高頻的開關功能,以滿足未來的技術需求。請大家持續關注ADI MEMS開關技術的未來更新。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19259瀏覽量

229653 -

mems

+關注

關注

129文章

3924瀏覽量

190583 -

soc

+關注

關注

38文章

4161瀏覽量

218167

發布評論請先 登錄

相關推薦

ADGM1121 0Hz/直流至18GHz DPDT MEMS開關IC

如何優化MEMS設計以提高性能

GY10-F100-DL磁感應開關抗干擾能力強有什么影響

提高帶負載能力引入什么反饋

新能源 加快構建新型電力系統行動方案--安科瑞張云18217320907

使用新型MEMS開關加快測試能力并提高系統產出

使用新型MEMS開關加快測試能力并提高系統產出

評論