**IBIS **模型簡介

IBIS(Input/Output Buffer Informational Specifation)是用來描述 IC 器件的輸入、輸出行為特性的文件。在IBIS模型里包含的核心內(nèi)容就是在給定負(fù)載情況下得到的幾條I/V和V/T曲線,有了這幾條曲線就可以描述buffer的行為特性。這就需要我們注意, IBIS 模型并不提供 IC 器件的功能信息、邏輯信息、輸入到輸出的時(shí)間延遲等信息。也就是說,IBIS 模型只是提供了I/O Buffer 的行為特性。所以對于器件商家而言 IBIS模型不會(huì)泄漏器件的內(nèi)部邏輯電路的結(jié)構(gòu)。仿真的時(shí)候把相應(yīng)的buffer添加到PCB板上電路的驅(qū)動(dòng)端和接收端就可以進(jìn)行 SI、串?dāng)_、EMC 以及時(shí)序的仿真分析。IBIS 模型可以通過實(shí)際的測量得出也可以通過器件的 SPICE模型轉(zhuǎn)換得到。由于它是一個(gè)行為級模型不包括IC內(nèi)部的電路信息,因此在仿真速度方面比相應(yīng)的Spice 的晶體管級模型要快 10~15 倍左右。

IBIS 模型是基于器件的。也就是說一個(gè) IBIS 模型是對于整個(gè)器件的管腳而言的,而不是幾個(gè)特殊的輸入、輸出或者是 I/O 管腳的 Buffer。因此,IBIS 模型中除了一些器件 Buffer 的電氣特性,還包括 pin-buffer 的映射關(guān)系(除了電源、地和沒有連接的管腳外,每個(gè)管腳都有一個(gè)特定的 Buffer),以及器件的封裝參數(shù)。還包括一些電氣說明如 Vinh、Vinl、Vmeas以及管腳的寄生參數(shù)(如管腳的引線 R、L、C)等。同時(shí)IBIS 有其特定的語法和書寫格式,模型中各個(gè)字段、各種信息都需要按照其語法格式進(jìn)行書寫。

一般情況,IBIS 模型包含以下一些信息,IBIS 模型的結(jié)構(gòu)如下圖 1.1 所示。

1.關(guān)于文件本身和器件名字的信息。這些信息用以下的關(guān)鍵詞描述: [IBIS Ver] IBIS的版本號, [File Name]文件的名稱, [File Rev]文件的版本號, [Component]器件的名稱和[Manufacturer]。器件的制造商。

2.關(guān)于器件的封裝電氣特性描述(寄生RLC),可以使用關(guān)鍵詞 [Package]和[Pin]描述。

3.為了表述器件管腳的Buffer所需要的相關(guān)的數(shù)據(jù)信息。關(guān)鍵詞 [Model] 是用來表示每個(gè)Buffer的數(shù)據(jù),具體的內(nèi)容有:Model_type(Buffer的類型)、Vinh、Vinl以及C_comp(IC芯片的電容)。在前面的內(nèi)容中提到了Buffer的特性描述,在IBIS模型中需要下面的一些關(guān)鍵詞描述:[Pull-up]、[Pull-down]、[GND clamp]、[Power clamp]和 [Ramp]。當(dāng)然對于不同的Buffer可能不需要上面的全部的關(guān)鍵詞來描述。如OC和漏極開路電路就不需要[Pull-up]關(guān)鍵詞的數(shù)據(jù)信息。

下面就圖 1.1的內(nèi)容作一個(gè)說明。在圖的右半部分的內(nèi)容有[…]的是 IBIS 模型中的關(guān)鍵詞;沒有方括號的條目則代表的是子參數(shù)的標(biāo)題。同時(shí)對于紅顏色的字符“Y”標(biāo)明在 IBIS 模型中是必選項(xiàng);而“N”則是表明該內(nèi)容在 IBIS 模型中為任選項(xiàng)。

IBIS 提供兩條完整的 V-I 曲線分別代表驅(qū)動(dòng)器為高電平和低電平狀態(tài),以及在確定的轉(zhuǎn)換速度下狀態(tài)轉(zhuǎn)換的曲線。V-I 曲線的作用在于為 IBIS 提供保護(hù)二極管、TTL 推拉驅(qū)動(dòng)源和射極跟隨輸出等非線性效應(yīng)的建模能力。

一般而言,IC 器件的輸入、輸出和 I/O 管腳的 Buffer 的行為特性是通過一定的形式描述的。下面分別對于輸入、輸出和 I/O 管腳 Buffer 的表述形式作一個(gè)介紹。

對于一個(gè) I/O(3-stateable)Buffer 需要 4 個(gè) I/V 曲線來表征其特性。其相應(yīng)的 4 個(gè)關(guān)鍵字分別是:

[Pullup]:在輸出為邏輯低時(shí),輸出管腳 Buffer 的 I/V 特性;

[Pulldown]:在輸出為邏輯高時(shí),輸出管腳 Buffer 的 I/V 特性;

[POWER Clamp]、[GND Clamp]:在輸出的電平強(qiáng)制在 Vcc以上和 GND 以下時(shí),輸出管腳 Buffer 的I/V 特性。此外,還需要Buffer 由一個(gè)狀態(tài)轉(zhuǎn)換為另一個(gè)狀態(tài)的轉(zhuǎn)換時(shí)間,以及Buffer 的輸出電容。

對于輸出 Buffer 只需要 2 套數(shù)據(jù)曲線就可以了。一個(gè)是 Pullup 曲線;另一個(gè)就是 Pulldown 曲線。兩個(gè)曲線的定義和前面的內(nèi)容是一致的。因?yàn)檩敵龉苣_沒有 3 態(tài)的模式,所以電源和地鉗位二極管的兩個(gè)曲線就不需要晶體管的曲線區(qū)分了。

對于漏極開路或者是集電極開路的器件需要 3 個(gè) I/V 曲線就可以了。3 個(gè)曲線分別是: [Pulldown]曲線、 [GND Clamp]以及[POWER Clamp]曲線。

輸入 Buffer 的數(shù)據(jù)。當(dāng)我們測量輸入 Buffer 的數(shù)據(jù)時(shí),我們可以使用同輸出或者 I/O Buffer 的方法。當(dāng)然我們必須將電壓源放置在輸入端。對于輸入 Buffer 只需要[POWER Clamp]和[GND Clamp]的 I/V 數(shù)據(jù)。此外還需要Buffer 的輸入電容。

對于上述的V-I、V-T曲線對應(yīng)下圖所示typ、min、max三種模式,在IBIS模型中對三種情況的定義如下:

IBIS模型使用

我們從IBIS模型中能夠獲得哪些信息

作為信號完整性工程師我們使用IBIS模型通常是用來做信號質(zhì)量仿真,并以仿真結(jié)果為依據(jù)來判斷互連設(shè)計(jì)是否滿足要求。其實(shí)我們通過IBIS模型中還可以獲得很大對設(shè)計(jì)有用的信息。

從IBIS模型中可以獲得信號上升時(shí)間信息

IBIS模型中的關(guān)鍵字[Ramp]定義了buffer輸出的上升下降沿的斜率。如下為micron的DDR3芯片的DQ_34_1600的[Ramp]語句。用 dv_r表示將R_load 接地情況下,邏輯電平狀態(tài)(由低到高)轉(zhuǎn)換的 20%到 80%的擺幅大小。

由DDR3 的IO電壓為1.5V可以計(jì)算出信號的上升下降時(shí)間為330ps左右(20%到 80%的上升時(shí)間為200ps這里為了仿真方便使用330ps)。由經(jīng)驗(yàn)法則“當(dāng)信號傳輸延時(shí)小于信號上升時(shí)間1/6時(shí),互連線處在集總區(qū)域,不會(huì)體現(xiàn)出傳輸線效應(yīng)。”可知,當(dāng)信號傳輸延時(shí)小于55ps時(shí),傳輸鏈路不會(huì)體現(xiàn)出傳輸線特性。也就是說如果當(dāng)信號線的延時(shí)小于55ps的時(shí)候我們可以考慮采用直連的形式,而不需要使用任何匹配。

在ADS中搭建仿真電路對其進(jìn)行驗(yàn)證。仿真電路中包含以下幾部分:信號源內(nèi)阻17ohm、負(fù)載阻抗為10Kohm和傳輸線阻抗并不匹配;信號源信號上升下降時(shí)間均為330ps、頻率800MHz輸出碼型“101010”;TLD1為延時(shí)可調(diào)的傳輸線。

將TLD1的delay分別設(shè)置為55ps(1/6上升時(shí)間)、165ps(1/2上升時(shí)間)、330ps(上升時(shí)間)進(jìn)行仿真對比,負(fù)載端接收的波形如下:

如上所示紅色實(shí)線為互連線延時(shí)為55ps的仿真結(jié)果,過沖只有170mV左右,而且振鈴也很小信號質(zhì)量沒有明顯惡化;藍(lán)色點(diǎn)線為互連線延時(shí)為1/2上升時(shí)間的仿真結(jié)果,可以看出此時(shí)信號的過沖達(dá)到了最大值幅度超過了600mV;粉色短劃線為互連線延時(shí)等于上升時(shí)間的仿真結(jié)果,此時(shí)不光過沖達(dá)到了最大值,而且過沖的寬度也有2倍的上升時(shí)間的寬度。

一個(gè)經(jīng)驗(yàn)豐富的信號完整性工程師通過IBIS模型中讀取了信號上升時(shí)間,并根據(jù)PCB布局情況估算布線延時(shí)就能夠大體得知接收端信號應(yīng)該有什么樣的特征,以及信號是否需要匹配。

確定buffer的輸出阻抗

由上一節(jié)的介紹我們能夠從IBIS模型中得到輸出buffer的上升時(shí)間,那么如果預(yù)估的布線延時(shí)超過了1/6的上升時(shí)間我們就需要通過增加匹配的方式來解決信號完整性問題。最簡單的匹配方式就是源端的串聯(lián)匹配,但如何確定最優(yōu)的串聯(lián)電阻值呢。我們也可以從IBIS模型中得到輸出buffer的驅(qū)動(dòng)能力,即buffer的輸出阻抗Zout,由于通常情況下傳輸線阻抗Zo控制在50ohm。那么就可以計(jì)算得到串聯(lián)匹配電阻值Rseries = Zo-Zout。下面我們來看如何得到驅(qū)動(dòng)器的輸出阻抗Zout。

IBIS模型中的pulldown和pullup曲線分別為輸出buffer的下管和上管的工作曲線。而數(shù)字電路只是簡單地工作在晶體管的飽和區(qū)或者可變電阻區(qū)。由模擬電路的知識(shí)我們可以畫出晶體管的直流負(fù)載線就可以找到操作點(diǎn)的電流電壓值,由此計(jì)算出輸出阻抗Zout。下面以pulldown曲線為例說明輸出阻抗Zout的求解過程。

一般情況IBIS模型中的每一條曲線都會(huì)對應(yīng)typ、min、max三種情況,分別代表了不同的電壓、溫度下晶體管表現(xiàn)出的不同特性。負(fù)載線由50ohm上拉到Vgs,對于micron DDR3的IBIS模型的DQ_34_1600 buffer的typ模式Vgs=Vddq=1.5V,由此可以確定直流負(fù)載線和兩個(gè)坐標(biāo)軸的交點(diǎn)(0V,30mA)、(1.5V,0A)。這樣就能畫出typ模式的直流負(fù)載線,進(jìn)而得到操作點(diǎn)的電壓和電流,計(jì)算得到Zout=600/17.8=23.7ohm。這個(gè)計(jì)算結(jié)果和DDR3手冊中的34ohm非常接近,由此可知這種方式計(jì)算輸出buffer的輸出阻抗是完全正確的。如此我們就可以不通過仿真估算出需要添加的匹配電阻值。

最優(yōu)的Rseries = 50-33.7 = 16.3ohm。在hyperlynx中搭建仿真電路進(jìn)行仿真驗(yàn)證,由于我們只是通過pulldown曲線來計(jì)算輸出阻抗,下面的仿真也只仿真一個(gè)下降沿。

如上所示的仿真結(jié)果來看信號基本沒有下沖,這就說明阻抗匹配已經(jīng)做的很好了。細(xì)心的讀者可能會(huì)想到,當(dāng)我們增加了16.3ohm的 之后,晶體管的直流負(fù)載線已經(jīng)發(fā)生了變化因?yàn)榈絍DDQ的電阻已經(jīng)由50ohm變?yōu)榱?0+16.3=66.3ohm了,對于在一些飽和區(qū)線性度比較高的晶體管這個(gè)影響并不是很大,而對于一些在飽和區(qū)電阻變化很快的晶體管就會(huì)導(dǎo)致匹配的不理想存在下沖和過沖。

我們也可以通過另一種更加簡便的方法來得到輸出阻抗Zout。源端阻抗匹配的目的就是要讓驅(qū)動(dòng)器輸出阻抗Zout加上源端串阻Rseries得到的等效輸出阻抗和傳輸線阻抗匹配。我們可以反過來思考當(dāng)驅(qū)動(dòng)器等效輸出阻抗等于傳輸線阻抗時(shí),驅(qū)動(dòng)器阻抗和傳輸線阻抗之間由于分壓使進(jìn)入傳輸線的入射電壓Vinc=Vddq/2,那么通過傳輸線Zo的電流為

對于上面的例子而言VDDQ=1.5V,Zo=50ohm,計(jì)算得到Iinc = 15mA。

由此,我們可以直接在pulldown曲線中找到15mA對應(yīng)的電壓500mV,計(jì)算得到Zout = 500/15 = 33.3ohm,進(jìn)而求得最佳的Rseries = 16.7ohm。

可以使用同樣的方法對pullup曲線進(jìn)行分析得到上管的輸出阻抗,然后可以根據(jù)上下管的輸出阻抗得到串阻的范圍,只需要在這個(gè)范圍內(nèi)選擇一個(gè)

就可以獲得最好的匹配效果。

確定各個(gè)管腳的封裝延時(shí)

IBIS模型中可能會(huì)包含三種形式的封裝信息,分別在[package] [pin] [package model]三個(gè)字段定義。下面來說明一下這三個(gè)字段的含義和區(qū)別。

首先來看[package]字段,它是定義關(guān)于R_pkg,L_pkg, C_pkg參數(shù)的一個(gè)字段,這里定義的參數(shù)是一個(gè)籠統(tǒng)的數(shù),為什么說它是籠統(tǒng)的呢,是因?yàn)樗挥幸唤M數(shù)就把器件所有的PIN腳都包括了。

顯然這種方式無法描述封裝內(nèi)不同管腳之間的寄生參數(shù)的差異性,在速率不是很高的情況下這種參數(shù)模型仿真得到的信號質(zhì)量可能和實(shí)際偏差不大,但是仿真結(jié)果不能表示封裝對信號時(shí)序的影響,同樣隨著信號速率的不斷提高如DDR3等接口的仿真如果想得到準(zhǔn)確的信號質(zhì)量和時(shí)序結(jié)果不能僅僅依靠[package]字段的參數(shù)。一般大的IC廠家都不會(huì)只弄這么一組數(shù)據(jù),還會(huì)在[pin]字段里描述了每個(gè)PIN腳的package參數(shù),同時(shí)與管腳的編號、管腳的信號名稱、管腳的模型名稱相對應(yīng),如下所示:

[pin]字段和[package]字段一樣,僅僅用一階的RLC電路來描述整個(gè)package的特性,可能在頻率不太高的情況下可以做個(gè)參考,但是到了高頻后這顯然是不夠的,PIN與PIN之間的耦合信息是沒有的。最理想的做法是用3D全波電磁場建模解決問題,但這種想法并不現(xiàn)實(shí)package的3D模型不是每個(gè)廠家都能提供的。但是我們已經(jīng)可以從[pin]字段的L_pin、C_pin中得到每個(gè)pin在封裝內(nèi)的延時(shí)信息:

這樣我們就可以通過PCB的布線控制來補(bǔ)償芯片封裝內(nèi)部的延時(shí)偏差,高速總線的時(shí)序設(shè)計(jì)將能夠得到最大限度的保障。

IBIS5.0版本又引入了[package model]字段,讓手頭僅有的資源發(fā)揮出最大的作用。[package model]字段內(nèi)容可以出現(xiàn)在.ibs文件里,也可以出現(xiàn)在一個(gè)單獨(dú)的以.PKG為后綴名的文件里。先看一下它的整體結(jié)構(gòu):

接下來3個(gè)字段[Manufacturer],[OEM],[Description]屬于描述性質(zhì)的,大家完全可以忽略,對仿真沒有什么影響。

[Number Of Pins],這個(gè)看字面意思應(yīng)該也能理解了,就是器件的引腳個(gè)數(shù)。[Pin Numbers]字段中列出了封裝中所有pin的編號。

接下來的[Model Data]將是[package model]的核心內(nèi)容,包含了[Resistance Matrix],[Inductance Matrix],[Capacitance Matrix],翻譯過來就是電阻矩陣,電感矩陣和電容矩陣。后面有Banded_matrix,Sparse_matrix等關(guān)鍵字,分別表示為一維矩陣,多維矩陣。一維矩陣的情況就和[pin]字段中定義的R_pin、L_pin、C_pin效果一樣并不包含pin和pin之間存在的耦合信息,多維矩陣則包含了pin和pin之間的耦合信息不僅能夠進(jìn)行信號質(zhì)量仿真也可以進(jìn)行串?dāng)_仿真。

通過上面的分析可知,我們可以在[pin]、[package model]字段中獲得每個(gè)管腳封裝內(nèi)部的延時(shí)信息,獲得這一延時(shí)對我們來說有著怎樣的意義呢?

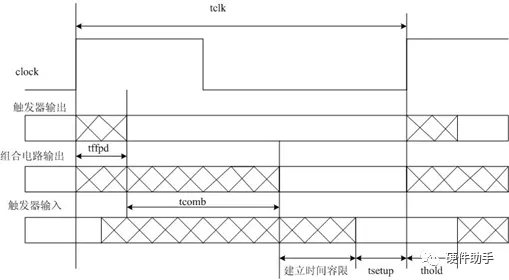

首先,我們知道互連線延時(shí)超過信號上升時(shí)間延時(shí)1/6時(shí)互連線就會(huì)表現(xiàn)出傳輸線效應(yīng)。我們已經(jīng)了解匹配電阻的布局必須足夠靠近驅(qū)動(dòng)器才能和驅(qū)動(dòng)器的輸出電阻看成是集總電路,才能獲得最好的匹配效果。由[ramp]參數(shù)可以讀出驅(qū)動(dòng)器的上升下降時(shí)間,我們可以用1/6信號上升時(shí)間減去封裝內(nèi)部的延時(shí)作為封裝管腳到匹配電阻的PCB布線延時(shí)的約束。

第二,由于我們在進(jìn)行信號質(zhì)量測試時(shí)只能在靠近輸入管腳的封裝處選擇測試點(diǎn)。而對于一個(gè)輸入管腳如果封裝延時(shí)很大,我們在封裝處測試得到的信號波形和芯片DIE實(shí)際接收到的波形將會(huì)存在很大的差異。

在ADS中搭建仿真電路,有8.6nH的電感和2.25pF的電容來模擬封裝參數(shù),仿真來觀測Vpkg和Vdie兩點(diǎn)的電壓波形差異。

計(jì)算得到封裝延時(shí),

此時(shí)的仿真結(jié)果如下圖所示(紅色實(shí)線為die內(nèi)接收波形,藍(lán)色短劃線為封裝處的測試波形)

如上所示,兩個(gè)波形存在比較明顯的差異。封裝處的測試波形在上升和下降沿都存在100ps左右的回溝,而且邊沿要比die內(nèi)測試到的波形要緩,幅度要比die內(nèi)信號波形低。這一現(xiàn)象可以用反射的理論來解釋,在封裝處測試的波形實(shí)際上是由發(fā)送端的入射波和接收端反射產(chǎn)生的反射波的疊加產(chǎn)生,由于封裝參數(shù)的存在導(dǎo)致入射波和反射波之間有一定的延時(shí),在疊加的時(shí)候就導(dǎo)致回溝或者臺(tái)階的出現(xiàn)。

如此我們可以試著減小封裝參數(shù)來看是否回購有效減小或者消失。將封裝參數(shù)更改為電感6.01nH、電容1.52pF,計(jì)算得到封裝延時(shí)

此時(shí)的仿真結(jié)果如下圖所示(紅色實(shí)線為die內(nèi)接收波形,藍(lán)色短劃線為封裝處的測試波形)

如上所示,兩個(gè)波形之間的差異已經(jīng)很小。封裝處的測試波形在上升下降沿的回溝都消失了,只是邊沿要比die內(nèi)測試到的波形要緩一點(diǎn),幅度要比die內(nèi)信號波形低。

-

二極管

+關(guān)注

關(guān)注

148文章

9991瀏覽量

169838 -

驅(qū)動(dòng)器

+關(guān)注

關(guān)注

54文章

8508瀏覽量

148687 -

PCB板

+關(guān)注

關(guān)注

27文章

1462瀏覽量

52859 -

IBIS

+關(guān)注

關(guān)注

1文章

55瀏覽量

20119 -

GND

+關(guān)注

關(guān)注

2文章

541瀏覽量

39409

發(fā)布評論請先 登錄

集成電路和信號完整性的設(shè)計(jì)

基于信號完整性分析的高速數(shù)字PCB的設(shè)計(jì)方法

Altium Designer中進(jìn)行信號完整性分析

基于信號完整性分析的高速數(shù)字PCB板的設(shè)計(jì)開發(fā)

用IBIS模型對高速PCB進(jìn)行信號完整性分析,出現(xiàn)報(bào)錯(cuò)顯示沒有有效的連接器插針模型

如何利用IBIS模型研究信號完整性問題?

利用IBIS模型研究信號完整性問題

信號完整性計(jì)算和器件的特性阻抗研究

基于IBIS模型的信號完整性分析

如何使用IBIS模型用于信號完整性計(jì)算和確定PCB設(shè)計(jì)解決方案的概述

如何使用IBIS模型來確定PCB板的信號完整性問題

基于信號完整性的高速PCB設(shè)計(jì)

評論