在systemverilog中,net用于對(duì)電路中連線進(jìn)行建模,driving strength(驅(qū)動(dòng)強(qiáng)度)可以讓net變量值的建模更加精確。net變量擁有4態(tài)邏輯值(0,1,z,x),它的driving strength有(supply,strong,pull,weak,highz)。net的值由連接到net的driver源(驅(qū)動(dòng)源)決定的,這些driver源可以是連續(xù)賦值語(yǔ)句(例如assign),也可以是門級(jí)建模原語(yǔ)(例如門級(jí)or或and或cmos等)。

在每個(gè)Δ仿真周期中,仿真器通過查看net上所有驅(qū)動(dòng)源的邏輯值(logical value)和強(qiáng)度值(strength level)來(lái)決定該net的邏輯值和強(qiáng)度值。如果net沒有驅(qū)動(dòng)源,那么它的值將是’z’態(tài)。如果net只有1個(gè)驅(qū)動(dòng)源,那么它的邏輯值和強(qiáng)度值等于驅(qū)動(dòng)源的值和強(qiáng)度。但是,如果net有多個(gè)驅(qū)動(dòng)源,那么需要比較它們的強(qiáng)度值了,強(qiáng)度最大的驅(qū)動(dòng)源將成功驅(qū)動(dòng)net。不過如果有多個(gè)強(qiáng)度最大的驅(qū)動(dòng)源,但它們的邏輯值不一樣的話,net的邏輯值將會(huì)是’x’態(tài),強(qiáng)度值是最強(qiáng)的strength。

需要注意的是driving strength是用于gate輸出和連續(xù)賦值語(yǔ)句輸出的(assign)。對(duì)于非net類型的多驅(qū)動(dòng),仿真工具會(huì)報(bào)多驅(qū)的編譯錯(cuò)誤。

Systemverilog的driving strength level(驅(qū)動(dòng)強(qiáng)度)有以下幾種:

上述strength level可以歸為3類:

- Driving strength:supply,strong,pull和weak

- Charge storage strength:large,medium和small

- High impedance:highz

Charge storage strength只用于trireg類型的net。

Driving strength的語(yǔ)法如下:

drive_strength ::=

( strength0 , strength1 )

| ( strength1 , strength0 )

| ( strength0 , highz1 )

| ( strength1 , highz0 )

| ( highz0 , strength1 )

| ( highz1 , strength0 )

strength0 ::= supply0 | strong0 | pull0 | weak0

strength1 ::= supply1 | strong1 | pull1 | weak1

charge_strength ::= ( small ) | ( medium ) | ( large )

strength0表示當(dāng)驅(qū)動(dòng)源驅(qū)動(dòng)net為0時(shí)的驅(qū)動(dòng)強(qiáng)度。Strength1表示當(dāng)驅(qū)動(dòng)源驅(qū)動(dòng)net為1時(shí)的驅(qū)動(dòng)強(qiáng)度。

net默認(rèn)的strength level是(strong0, strong1)。對(duì)于pullup和pulldown gate,默認(rèn)的strength level是pull。trireg默認(rèn)的strength level是medium。Supply net的默認(rèn)strength level是supply。另外從上面syntax看出,(highz1, highz0)和(highz0, highz1)的strength level組合是非法的。

結(jié)合上面的理論講解,給出1個(gè)例子如下:

module strength;

logic i1, i2;

wire logic out;

assign (supply1, weak0) out = i1;

assign (pull1, supply0) out = i2;

initial begin

i1 = 1'b0;

i2 = 1'b0;

$strobe("[time:%0t],i1:%b, i2:%b, out:%b, out_strength:%v", $time, i1, i2, out, out);

#1ns;

i1 = 1'b0;

i2 = 1'b1;

$strobe("[time:%0t],i1:%b, i2:%b, out:%b, out_strength:%v", $time, i1, i2, out, out);

#1ns;

i1 = 1'b1;

i2 = 1'b0;

$strobe("[time:%0t],i1:%b, i2:%b, out:%b, out_strength:%v", $time, i1, i2, out, out);

#1ns;

i1 = 1'b1;

i2 = 1'b1;

$strobe("[time:%0t],i1:%b, i2:%b, out:%b, out_strength:%v", $time, i1, i2, out, out);

end

endmodule

使用Questasim仿真輸出的log結(jié)果為:

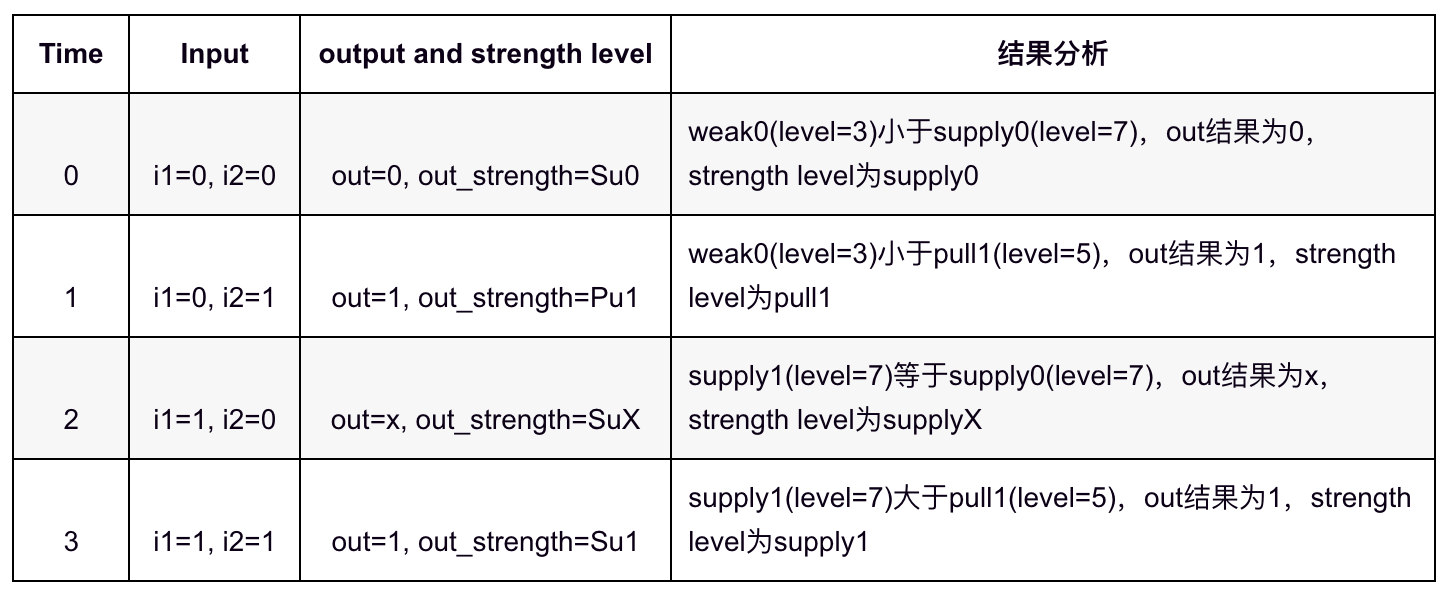

# [time:0],i1=0, i2=0, out=0, out_strength=Su0

# [time:1],i1=0, i2=1, out=1, out_strength=Pu1

# [time:2],i1=1, i2=0, out=x, out_strength=SuX

# [time:3],i1=1, i2=1, out=1, out_strength=Su1

"assign (supply1, weak0) out = i1"行給net類型的out驅(qū)動(dòng)i1的值,其中strength1為supply1(level=7),strength0為weak0(level=3)。12行給net類型的out驅(qū)動(dòng)i2的值,其中strength1為pull1(level=5),strength為supply0(level=7)。

" assign (pull1, supply0) out = i2"行給net類型的out驅(qū)動(dòng)i2的值,其中strength1為pull1(level=5),strength為supply0(level=7)。

Driving strength還有很多其它的組合,大家可以復(fù)制上述代碼,并修改assign out語(yǔ)句的strength0與strength1去產(chǎn)生其它的組合并分析結(jié)果。

另外,大家可能好奇如何打印出net變量的strength level?在systemverilog中提供了%v格式化打印。%v的輸出是3個(gè)字符的string類型,前2個(gè)字符指示strength類型,第三個(gè)字符指示當(dāng)前邏輯值。比如上述log中的Su0或Pu1或SuX或Su1。

-

驅(qū)動(dòng)器

+關(guān)注

關(guān)注

54文章

8646瀏覽量

149378 -

仿真器

+關(guān)注

關(guān)注

14文章

1034瀏覽量

85119 -

Verilog語(yǔ)言

+關(guān)注

關(guān)注

0文章

113瀏覽量

8512

發(fā)布評(píng)論請(qǐng)先 登錄

SystemVerilog中的Virtual Methods

SystemVerilog中的“const”類屬性

protel中的“have no driving source”問題

SystemVerilog Assertion Handbo

SystemVerilog的斷言手冊(cè)

SystemVerilog中$cast的應(yīng)用

SystemVerilog中的操作方法

SystemVerilog中可以嵌套的數(shù)據(jù)結(jié)構(gòu)

SystemVerilog中的package

SystemVerilog中的Shallow Copy

SystemVerilog中的Semaphores

帶你了解SystemVerilog中的關(guān)聯(lián)數(shù)組

評(píng)論