本文著重介紹ADI公司的軟件定義無線電(SDR)中的射頻(RF)鎖相環(huán)(PLL)相位同步特性。這個功能有助于降低天線校準(zhǔn)的復(fù)雜性,特別是對于采用大型天線陣列的系統(tǒng)。關(guān)于同步的控制和配置,請參見用戶指南1。本文著重介紹其應(yīng)用和優(yōu)勢。

相位相干信號

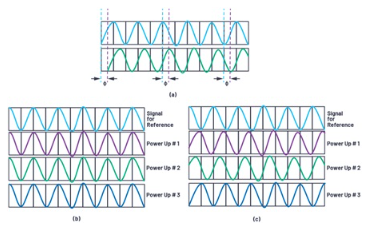

相干性是波的一種特性,定義了單個波或兩個或多個波之間的物理量中存在的關(guān)系。在電子學(xué)中,物理系統(tǒng)處理連續(xù)波和時鐘信號的相位、頻率和振幅。一般來說,隨著時間流逝,如果兩個信號之間的差別始終保持恒定不變和穩(wěn)定,那么這兩個信號就是相位相干的。圖1a顯示了隨著時間不斷流逝,兩個信號的相位。這兩個信號表現(xiàn)出相干相位關(guān)系,因為它們之間的相位保持不變。圖1b比較了系統(tǒng)中的基準(zhǔn)信號在不同上電周期中的初始相位。從這個圖中,還可以看出在每次上電后,兩個信號之間的相干相位關(guān)系。但是,在圖1c所示的示例中,相位是不相干的,因為在每次上電后,信號都以隨機(jī)相位作為開始。

圖1. 相干相位關(guān)系和不相干相位關(guān)系示例。

多通道和多天線系統(tǒng)中的相位缺陷和消除

相控陣和大規(guī)模MIMO系統(tǒng)具有多個天線和多個射頻通道。從數(shù)字后端到天線陣列,在多平面上保持相位相干和時序同步,這是這類系統(tǒng)的主要要求。例如,在介質(zhì)訪問級別需要幀同步,數(shù)字接口需要相干性(例如,確定性延遲),在多個轉(zhuǎn)換器或芯片對多個通道進(jìn)行采樣時需要同步,要生成射頻,需要多個本地振蕩器(LO)之間相位相干,以及,需要天線陣列的各元件之間保持確定性相位關(guān)系。因此,在不同階段保持相干關(guān)系至關(guān)重要。但是,因為一些現(xiàn)實因素,這一任務(wù)非常具有挑戰(zhàn)性,例如器件與器件之間的差異、印刷電路板上的線路、組件之間的非線性、耦合效應(yīng)、分頻器比率、硬件老化、時鐘漂移、溫度漂移,以及本地振蕩器漂移。

如果一個系統(tǒng)中使用多個射頻本地振蕩器,還需要注意本地振蕩器相位漂移會隨通道和時間的變化而變化。使用不同的架構(gòu)可以生成相干的射頻LO信號。

射頻LO分布:LO信號由一個共同的LO產(chǎn)生,然后分布在系統(tǒng)中。但因為頻率較高,這實施起來并不簡單,射頻損耗和射頻耦合使其變得相當(dāng)困難。

參考時鐘分布:為了避免射頻損耗,會在本地生成LO信號。但是,由于鎖相環(huán)或壓控振蕩器(VCO)之間存在差異,要同步單個生成的LO信號,還需要付出更多努力。

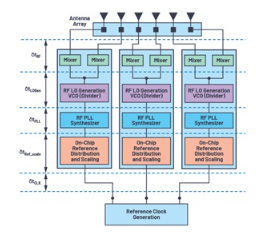

圖2顯示了一個多通道和多天線射頻子系統(tǒng)架構(gòu)示例,該架構(gòu)是基于集成式收發(fā)器芯片。其中包括一個片上頻率合成器(一個鎖相環(huán))和一個VCO,用于生成射頻LO。參考時鐘在收發(fā)器芯片外部生成,然后分別分配給每個芯片的器件時鐘輸入。在芯片上完成對參考時鐘的進(jìn)一步擴(kuò)展和分配。圖2分解顯示從系統(tǒng)參考時鐘到天線的傳輸路徑。該路徑可以分為不同的段,每個段都造成傳輸延遲。傳輸延遲的變化會引起系統(tǒng)相位差的變化,從而影響系統(tǒng)的相位相干性。

圖2. 多通道和多天線系統(tǒng)中的相位缺陷來源。

我們采用校準(zhǔn)技術(shù)來消除這種真實缺陷。通過使用校準(zhǔn)方法,我們確定未知因素,然后加以校正。在相控陣和大規(guī)模MIMO系統(tǒng)中,由于相位差的存在,各個射頻通道的頻率響應(yīng)各不相同。此外,它本質(zhì)上是隨時間變化的。通過出廠校準(zhǔn),可以補(bǔ)償系統(tǒng)中可以測量的靜態(tài)因素。使用初始校準(zhǔn),可以消除與部署相關(guān)的因素,在系統(tǒng)每次啟動時,也可以運行這種校準(zhǔn)。為了消除動態(tài)和時變因素的影響,需要定期對天線進(jìn)行校準(zhǔn)。除了溫度漂移外,LO相位漂移也是這樣一個動態(tài)因素,會隨通道和時間變化。如果在運行期間執(zhí)行這些校準(zhǔn),它們會消耗寶貴的系統(tǒng)資源,例如時間頻率。因此,產(chǎn)生了一個優(yōu)化問題:用最少的資源進(jìn)行校準(zhǔn),以最大化系統(tǒng)性能。

使用射頻鎖相環(huán)相位同步特性簡化校準(zhǔn)

ADRV9009是ADI公司的 RadioVerse? 產(chǎn)品系列中的一款雙通道、高度集成的軟件定義無線電。它提供兩個發(fā)射和兩個接收通道,分別將數(shù)字IQ位轉(zhuǎn)換為射頻和將射頻轉(zhuǎn)換為數(shù)字IQ位。它基于零中頻架構(gòu),該架構(gòu)能夠最大限度降低系統(tǒng)功耗,并提供出色的發(fā)射機(jī)和接收機(jī)射頻性能。此器件可在不使用外部組件的情況下,使用片上功能生成完整頻率。其中包括三個片上頻率合成器,射頻LO合成器為其中之一。每個合成器都有一個集成式VCO和一個環(huán)路濾波器。在整個受支持的頻率范圍內(nèi)生成頻率時,這種高度集成和出色性能能提供很高的靈活性。

在數(shù)字端,ADRV9009采用JESD204B協(xié)議作為執(zhí)行數(shù)字?jǐn)?shù)據(jù)傳輸?shù)拇薪涌?。它利用JESD SYSREF信號,從內(nèi)部支持多芯片同步。因此,可以創(chuàng)建大規(guī)模相控陣和大規(guī)模MIMO系統(tǒng)。

除了多芯片同步,ADRV9009還提供射頻鎖相環(huán)同步特性,使內(nèi)部生成的LO信號具有相位相干性,且與采用的參考時鐘一致。基于這個特性,可在大規(guī)模系統(tǒng)中輕松實現(xiàn)以下這些功能:

上電時相位相干:在每個上電周期,實現(xiàn)恒定不變、確定性和穩(wěn)定的相位值

運行期間相位相干:在啟動之后跟蹤相位值

多器件之間相位相干:進(jìn)一步支持多芯片同步

校準(zhǔn)算法需要占用數(shù)字硬件中的計算和存儲器資源。例如,算法通常在基帶處理鏈中實現(xiàn),并利用FPGA/DSP資源。這個特性間接降低了系統(tǒng)校準(zhǔn)所用的功耗和資源。因此,啟用該特性可以優(yōu)化整個系統(tǒng)的性能和效率。因為復(fù)雜的校準(zhǔn)算法,系統(tǒng)從啟動到達(dá)到穩(wěn)定狀態(tài)需要更長的時間。可以通過在啟動時啟用射頻鎖相環(huán)同步特性來最大限度縮短這個時間。會定期執(zhí)行校準(zhǔn)程序,以跟蹤LO相位中的漂移,尤其是溫度導(dǎo)致的漂移。否則,這些漂移會影響多天線系統(tǒng)的波束成型模式。借助射頻鎖相環(huán)同步跟蹤特性,可以最小化校準(zhǔn)頻率,同時保持所需的波束成型性能。可以使用四種模式來控制相位同步特性:

模式1:禁用片上射頻鎖相環(huán)同步特性。

模式2:啟用射頻鎖相環(huán)同步,僅用于初始化。

模式3:在初始化時執(zhí)行射頻鎖相環(huán)同步,僅進(jìn)行一次跟蹤。

模式4:連續(xù)跟蹤射頻鎖相環(huán)相位。

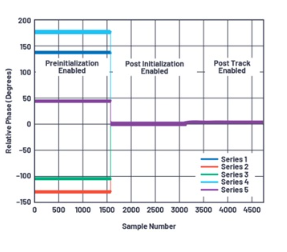

圖3顯示在多芯片和多通道環(huán)境下,在多次上電時測量得出的相位差結(jié)果。測量設(shè)置使用兩個完全相同的評估板生成4個射頻通道,其中一個是 ADRV9009-W/PCBZ。利用矢量網(wǎng)絡(luò)分析儀,測量每個上電周期中發(fā)射機(jī)輸出信號之間的相位差的變化。

圖3. 通過射頻鎖相環(huán)相位同步周期,進(jìn)行發(fā)射機(jī)輸出相位比較1(射頻調(diào)諧頻率 = 1800 MHz)。

測量五次上電周期的值,并在不同運行模式下比較這些值。啟動系統(tǒng)時,未啟用射頻鎖相環(huán)同步特性。可以看出,在每個上電周期,相位都是隨機(jī)的。在啟用射頻鎖相環(huán)同步特性之后,所有5個相關(guān)相位值轉(zhuǎn)換為公差為±2°的可重復(fù)值。啟動連續(xù)跟蹤之后,它以一定的延遲來保持該相關(guān)相位值。這種延遲導(dǎo)致相關(guān)相位增大1°至2°。所以,從圖中可以看到少量漂移。利用此特性,可以在確定性公差內(nèi)實現(xiàn)穩(wěn)定的相位值。這會降低動態(tài)因素帶來的影響,并簡化系統(tǒng)的整個同步和校準(zhǔn)過程。

結(jié)論

ADI公司提供的先進(jìn)的高度集成軟件定義無線電(包括ADRV9009雙通道收發(fā)器)具備射頻鎖相環(huán)同步特性。如果使用此器件構(gòu)建大型天線陣列系統(tǒng),可以使用射頻鎖相環(huán)同步特性來簡化天線校準(zhǔn)。提供各種運行模式,可根據(jù)應(yīng)用要求進(jìn)行選擇。可以使用軟件API功能來輕松控制和配置該特性。ADRV9009用戶指南1詳細(xì)介紹了該特性的功能和使用方法。

審核編輯:郭婷

-

射頻

+關(guān)注

關(guān)注

104文章

5573瀏覽量

167694 -

pll

+關(guān)注

關(guān)注

6文章

776瀏覽量

135131 -

無線電

+關(guān)注

關(guān)注

59文章

2139瀏覽量

116436

發(fā)布評論請先 登錄

相關(guān)推薦

鎖相環(huán)的原理,特性與分析

鎖相環(huán)相位噪聲與環(huán)路帶寬的關(guān)系是什么

LabVIEW鎖相環(huán)(PLL)

鎖相環(huán)原理

模擬鎖相環(huán)與載波同步實驗

實驗 數(shù)字鎖相環(huán)與位同步

多速率鎖相環(huán)相位同步方法的研究

鎖相環(huán)相位噪聲與環(huán)路帶寬的關(guān)系分析

PLL鎖相環(huán)的特性、應(yīng)用與其基本工作過程

使用具有射頻鎖相環(huán)相位同步特性的SDR簡化天線校準(zhǔn)

使用具有射頻鎖相環(huán)相位同步特性的SDR簡化天線校準(zhǔn)

評論