在時序分析時,我們常會碰到的一類現象是:關鍵路徑上的邏輯單元過于分散,導致布線延遲過大,從而造成時序違例。對此,我們可以通過相對位置約束或絕對位置約束來限定相關邏輯的位置關系。就相對位置約束而言,即使芯片型號發生了改變也依然可以繼承原有約束;而對于絕對位置約束,一旦芯片型號發生改變就要確認是否要調整相應位置。此外,如果時序違例路徑較多,這種方法的有效性將大大降低。

我們還可以采用手工布局的方式,這對于時序違例路徑集中在某一個模塊或某一個層次內的情形較為適用。使用此方法時需要注意Pblock的大小。Pblock不能太小,否則會增加布局布線的壓力;Pblock也不能太大,否則會浪費資源。實際上,Vivado針對Pblock的資源利用率也提供了指導值,該指導值跟整個芯片的資源利用率指導值一致,可通過命令report_failfast查看。Pblock的形狀也是一個重要的因素。通常建議為標準的矩形。不規則的形狀如在矩形框中挖掉一個小的矩形形成“回”字形狀會嚴重危害時序性能且導致編譯時間增長。Pblock的位置也是一個重要因素。可以先讓工具自動布局,在此基礎上觀察關鍵模塊的分布情況,然后參考此位置確定Pblock的位置。可以看到,使用Pblock要求工程師有一定的工程經驗,需要考慮的因素也較多。如果Pblock的位置不合理,可能會出現顧此失彼的情形(Pblock內的模塊時序改善了,而其他模塊的時序又惡化了)。Pblock的另一弊端是缺乏靈活性。當芯片型號發生改變時很有可能重新確定Pblock的大小或位置。

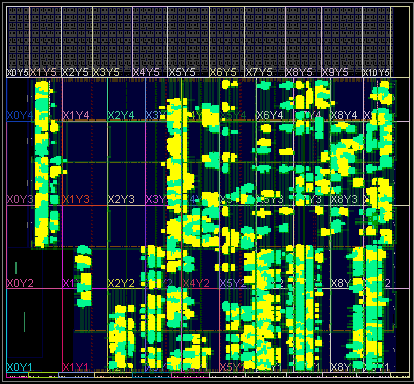

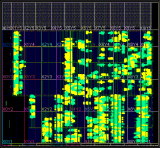

好在Vivado提供了一個新的約束屬性USER_CLUSTER(要求Vivado版本為2022.2或之后)。該屬性的作用是指導工具在布局時將指定層次/模塊下的邏輯單元放得更緊湊一些。為便于說明,我們看一個例子。在沒有使用該屬性時,布局結果如下圖所示。可以看到整個設計的資源利用率并不高,但卻比較分散。

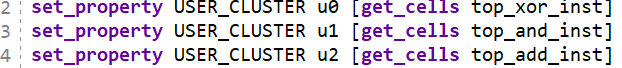

接下來我們使用屬性約束USER_CLUSTER。該屬性的屬性值為用戶定義的組名,屬性施加的對象為get_cells的返回值,也就是用戶通過get_cells指定的模塊,如下圖所示。

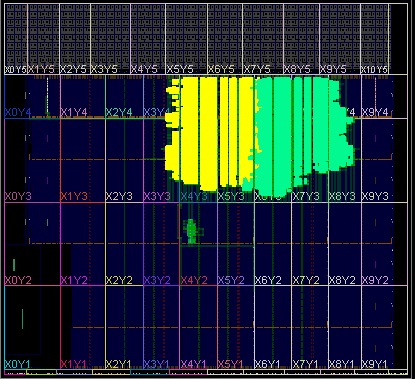

使用此約束之后,最終的布局結果如下圖所示。可以看到,相關資源已經非常緊湊了。

相比于手工布局,USER_CLUSTER更為靈活,更為易用。只是需要用戶確認哪些模塊下的邏輯單元需要放置得緊湊些。

審核編輯:湯梓紅

-

芯片

+關注

關注

456文章

50892瀏覽量

424342 -

模塊

+關注

關注

7文章

2716瀏覽量

47543 -

時序分析

+關注

關注

2文章

127瀏覽量

22570 -

Vivado

+關注

關注

19文章

812瀏覽量

66624

原文標題:如何讓同一層次的模塊在布局時更緊湊一些

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何讓同一層次的模塊在布局時更緊湊一些

如何讓同一層次的模塊在布局時更緊湊一些

評論