通常,開發任何類型的硬件(包括芯片,作為電子設備大腦的微小電子元件),都是從用正常語言描述硬件應該做什么開始的。然后,經過專門訓練的工程師將該描述翻譯成硬件描述語言(HDL),例如 Verilog,以創建允許硬件執行其任務的實際電路元件。

自動化此翻譯可以減少工程過程中的人為錯誤來源。但是,直到最近,AI 才展示了基于機器的端到端設計翻譯的能力。一些大型語言模型(LLM),如 OpenAI 的 ChatGPT 和谷歌的 Bard,聲稱能夠生成各種編程語言的代碼;但它們在硬件設計中的應用尚未得到廣泛研究。

近日,來自紐約大學和新南威爾士大學的研究團隊使用簡單的英語「對話」與 AI 模型制造了一個微處理芯片,這是一項史無前例的成就,可以加快芯片開發速度,并允許沒有專業技術技能的個人設計芯片。

研究團隊展示了兩名硬件工程師如何用標準英語與 ChatGPT-4「交談」,以設計一種新型微處理器架構。然后,研究人員將設計送去制造。

在該研究中,LLM 能夠通過來回對話生成可行的 Verilog。隨后將基準測試和處理器發送到 Skywater 130 納米穿梭機上進行流片(tapeout)。

研究共同作者 Hammond Pearce 說:「我們認為這項研究產生了第一個完全由 AI 生成的 HDL,用于制造物理芯片。這項研究表明,AI 也可以使硬件制造受益,特別是當它被用于對話時,你可以來回地完善設計。」

研究背景

隨著數字設計的能力和復雜性不斷增長,集成電路 (IC) 計算機輔助設計 (CAD) 中的軟件組件已在整個電子設計自動化流程中采用機器學習 (ML)。傳統方法試圖對每個過程進行正式建模,而基于 ML 的方法則側重于識別和利用可概括的高級特征或模式——這意味著 ML 可以增強甚至取代某些工具。盡管如此,IC CAD 中的 ML 研究仍傾向于關注后端過程。

在此,研究團隊探索了將新興類型的 ML 模型應用于硬件設計過程的早期階段時面臨的挑戰和機遇:硬件描述語言 (HDL) 本身的編寫。

雖然硬件設計以 HDL 表示,但它們實際上以自然語言(例如英語需求文檔)提供的規范開始設計 lifecycle。將這些轉換為適當的 HDL(例如 Verilog)的過程必須由硬件工程師完成,這既耗時又容易出錯。使用高級合成工具等替代途徑可以讓開發人員使用 C 語言等高級語言指定功能,但這些方法是以犧牲硬件效率為代價的。這激發了對 AI 或基于 ML 的工具的探索,將其作為將規范轉換為 HDL 的替代途徑。

最新的 LLM (如 OpenAI 的 ChatGPT 和 Google 的 Bard)為其功能提供了不同的「會話」聊天界面。

會話式 LLM 用于迭代設計硬件

受 LLM 發展的啟發,研究人員提出以下問題:將這些工具集成到 HDL 開發過程中有哪些潛在優勢和障礙?

為了理解這項新興技術的重要性,進行像這樣的觀察性研究至關重要。對會話式 LLM 對硬件設計的影響的調查既相關又及時。

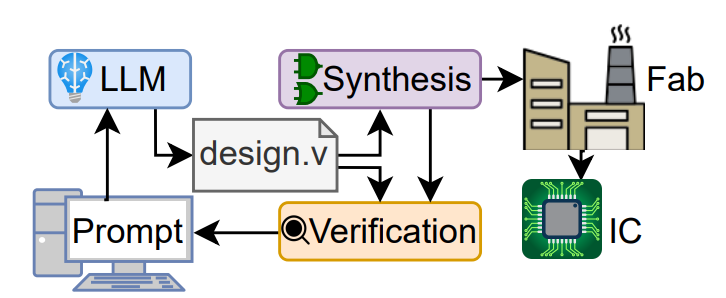

圖 1:會話式 LLM 能否用于迭代設計硬件?(來源:論文)

該研究的貢獻如下:

首次對對話式 LLM 在硬件設計中的使用進行了研究。

開發基準以評估 LLM 在功能硬件開發和驗證方面的能力。

利用 ChatGPT-4,對硬件中復雜應用程序的端到端協同設計進行觀察性研究。

首次使用 AI 為流片編寫完整的 HDL,實現了一個重要的里程碑。

為在硬件相關任務中有效利用尖端會話 LLM 提供實用建議。

研究人員進行了兩個對話實驗。第一個實驗涉及預定義的對話流程和一系列基準挑戰,而第二個實驗需要一個開放式的「自由聊天」方法,LLM 在一個更大的項目中擔任聯合設計師。

從本質上講,有無數種方法可以與對話模型「聊天」。為了探索使用會話式 LLM 實現「標準化」和「自動化」流程的潛力,研究人員定義了一個嚴格的「腳本化」對話基于一系列基準。

然后,研究人員使用一致的指標評估一系列 LLM,根據通過附帶測試平臺所需的指令水平確定對話的相對成功或失敗。然而,雖然對話流在結構上保持相同,但它在測試運行之間固有地存在一些差異,這取決于評估者需要決定 (a) 每個步驟中需要什么反饋,以及 (b) 如何格式化人類反饋。

下圖詳細說明了與 LLM 對話以創建硬件基準的一般流程。

圖 2:簡化的 LLM 對話流程圖。(來源:論文)

真實世界的硬件設計具有更廣泛和更復雜的要求。考慮到以前使用的方法時,這是一個挑戰,該方法編寫并限制了人類與 LLM 交互的方式。然而,鑒于不同層次的人類反饋相對成功,研究人員試圖研究非結構化對話是否可以帶來更高水平的表現和相互創造力。對此進行調查通常會通過大規模的用戶研究來完成,硬件工程師在開發過程中會與該工具配對。研究目標是通過執行概念驗證實驗來推動硬件領域的此類研究,將 ChatGPT-4 與經驗豐富的硬件設計工程師(論文作者之一)配對, 并在執行更復雜的設計任務時定性地檢查結果。

挑戰與機會

挑戰:雖然很明顯,使用對話式 LLM 來協助設計和實現硬件設備總體上是有益的,但該技術尚不能僅通過驗證工具的反饋來一致地設計硬件。當前最先進的模型在理解和修復這些工具出現的錯誤方面表現不夠好,無法僅通過初始人機交互來創建完整的設計和測試平臺。

機會:盡管如此,當人類反饋被提供給功能更強大的 ChatGPT-4 模型,或者用于協同設計時,語言模型似乎是一個「力量倍增器」,允許快速設計空間探索和迭代。總的來說,ChatGPT-4 可以生成功能正確的代碼,這可以在實現通用模塊時節省設計人員的時間。

未來可能的工作可能涉及更大規模的用戶研究以調查這種潛力,以及開發特定于硬件設計的會話式 LLM 以改進結果。

審核編輯:劉清

-

HDL語言

+關注

關注

0文章

47瀏覽量

8913 -

OpenAI

+關注

關注

9文章

1082瀏覽量

6483 -

ChatGPT

+關注

關注

29文章

1560瀏覽量

7597 -

LLM

+關注

關注

0文章

286瀏覽量

327

原文標題:對話式 LLM 用于硬件設計,首個完全由 AI 輔助創建的微處理芯片誕生

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【比特熊充電棧】實戰演練構建LLM對話引擎

對比解碼在LLM上的應用

Stability AI發布首個用于編程的生成式LLM AI產品—StableCode

在線研討會 | 基于 Jetson 邊緣計算平臺構建 Azure OpenAI LLM 安全護欄

對話式LLM用于硬件設計

對話式LLM用于硬件設計

評論