點擊上方“泰克科技” 關注我們!

點擊上方“泰克科技” 關注我們!■憶阻器

憶阻器英文名為memristor, 由“Memory” 與”Resistor“合成,用符號M表示,與電阻R,電容C,電感L構成四種基本無源電路器件,能夠實現0、1信息存儲,是一種新一代非易失存儲器,通常稱為阻變存儲器(RRAM)。憶阻器具有高速、低功耗、易集成、以及與CMOS工藝兼容等優勢②。

今年的泰克云上大講堂,也有為大家詳細介紹過憶阻器的發展及測試方案,本期的白皮書內容可與直播回放結合觀看喔~

本期白皮書內容主要包括:

■概述

■憶阻器測試

?憶阻器參數表征、分類及測試流程

?憶阻器基礎研究測試

?憶阻器性能研究測試

i. 非易失存儲器性能測試

ii.神經突觸阻變動力學測試

?憶阻器集成及應用研究測試

?憶阻器/神經元網絡測試系統的必要性

■泰克憶阻器/神經元網絡測試系統

概述

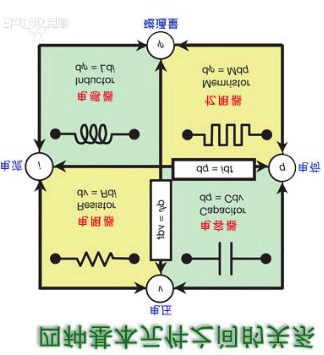

憶阻器是連接磁通量與電荷之間關系的紐帶(圖一),在無源電路器件中,R揭示了電壓與電流之間的關系,L揭示了電流與磁通量之間的關系,C揭示了電壓與電量之間的關系,而電量與磁通量之間的關系,很久以來一直未受到關注。1971年,美籍華裔科學家蔡紹棠教授從電路理論完備性角度預測除電阻、電容、電感之外,還存在第四種遺失的無源基本電路元件,表征電荷與磁通量之間的關系,并從數學上進行了推到(圖二),將該遺失的無源器件命名為憶阻器②。

圖一①

圖二

盡管理論上早已推導出憶阻器的概念,但由于上世紀七八十年代半導體器件的飛速發展,這一理論并未引起重視。直到2006年,HP實驗室才證明了Crossbar 結構的憶阻器的存在,并于2008年在《Nature》上發表。

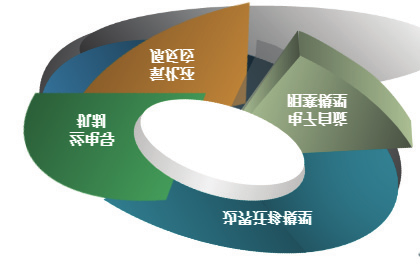

隨著憶阻器研究的不斷深入,多種實現機制被發現(圖三),主要分為無機憶阻物理機制與有機憶阻物理機制。現階段各方面性能均衡且接近實用的RRAM主要是基于氧空位或金屬絲導電通道的憶阻器件,這兩類器件的研究最廣泛,物理機制了解得最深入,調控方法也最完善。相比而言,其它機理的憶阻器件還需更多更深入的研究工作②。

圖三④

在憶阻器研究不斷取得新成果的同時,基于憶阻器的多功能耦合器件也成為研究人員關注的熱點,成為新型信息器件的重要發展路徑。這些新型耦合器件包括:磁耦合器件、光耦合器件、超導耦合器件、柔性憶阻器件、鐵電耦合器件等②。

憶阻器研究涉及微電子、凝聚態物理、材料學、電路與系統、計算機、自動化、人工智能和神經生物學等多學科領域,屬于新興交叉學科②。

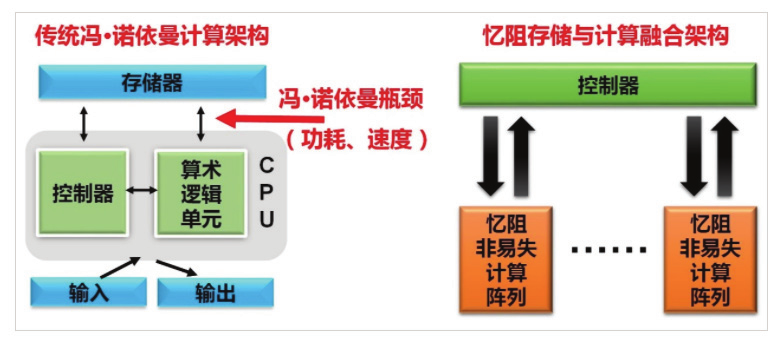

憶阻器備受關注的重要應用領域包括:非易失存儲(Nonvolatile memory),邏輯運算(Logic computing),以及類腦神經形態計算(Brain-inspired neuromorphic computing)等。這三種截然不同又相互關聯的技術路線,為發展信息存儲與處理融合的新型計算體系架構,突破傳統馮·諾伊曼架構(圖四左)瓶頸,提供了可行的路線。

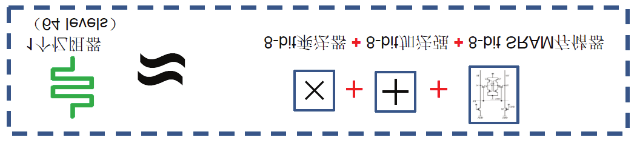

基于憶阻器非易失性邏輯運算的架構為數字式信息存儲與處理融合方式(圖四右),圖五示意出一個64 level的憶阻器,相當于8bit 乘法器+8bit加法器+8bit存儲器,完美詮釋了憶阻存儲與計算的融合。

圖四⑤

圖五③

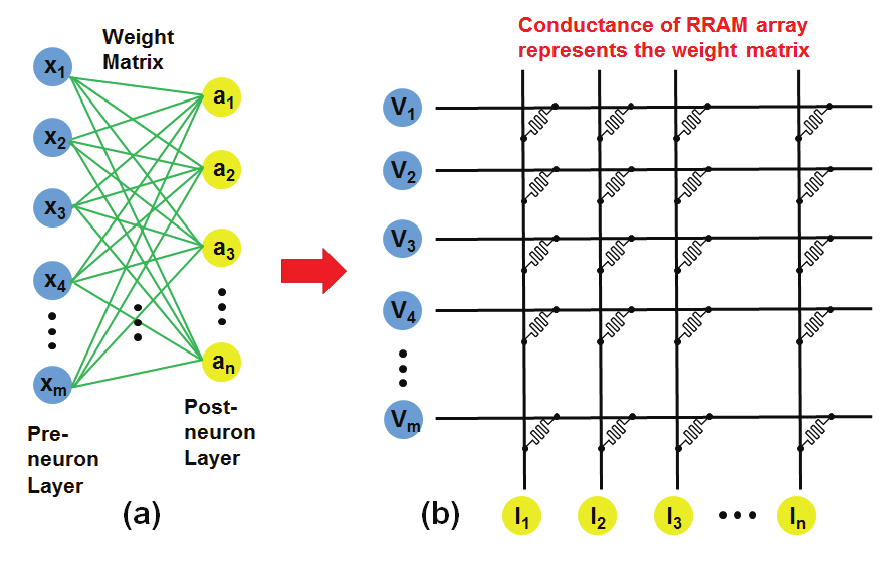

基于憶阻器的類腦神經形態計算架構為模擬式信息存儲與處理融合方式。類腦計算是借鑒神經科學處理信息的基本原理,面向人工智能,發展新的非馮諾依曼計算技術。類腦計算系統是人工智能的基石,擁有極為廣闊的應用前景。神經形態計算芯片集成了受神經生物學系統啟發的一系列功能,物理結構類似于人工神經網絡,每個神經形態芯片都包含許多與人工神經元相對應的小型計算單元,這些單元相互連結,形成非線性復雜網絡系統。人工神經元網絡的單元由新型高速非易失存儲器組成的陣列構成,圖六為將神經元網絡映射為憶阻器陣列的示意圖。

圖六③

目前,國內憶阻器研究在材料體系、物理機制、性能優化、規模集成、非線性電路和類腦神經形態計算等方面取得了令人鼓舞的進展,但在憶阻器可靠性、陣列的控制電路設計,以及CMOS集成工藝等方面還需要研究者和廣大工程技術人員協同攻關②,更需要針對憶阻器不同研究階段的專業的測試系統保駕護航。

?

?解鎖完整版白皮書

掃描二維碼,下載完整版白皮書,并申請泰克憶阻器測試方案報價/演示!

憶阻器測試

1

憶阻器參數表征、分類及測試流程

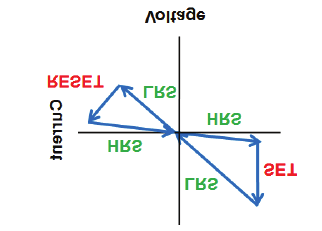

憶阻器具有阻變存儲的功能,因此有類似存儲器“置0”和“置1”以及及讀操作,只不過“置0”被稱為“RESET”,即從低阻態(LRS)重置為高阻態(HRS),反之被稱為SET,即“置1”操作(圖七)。

圖七③

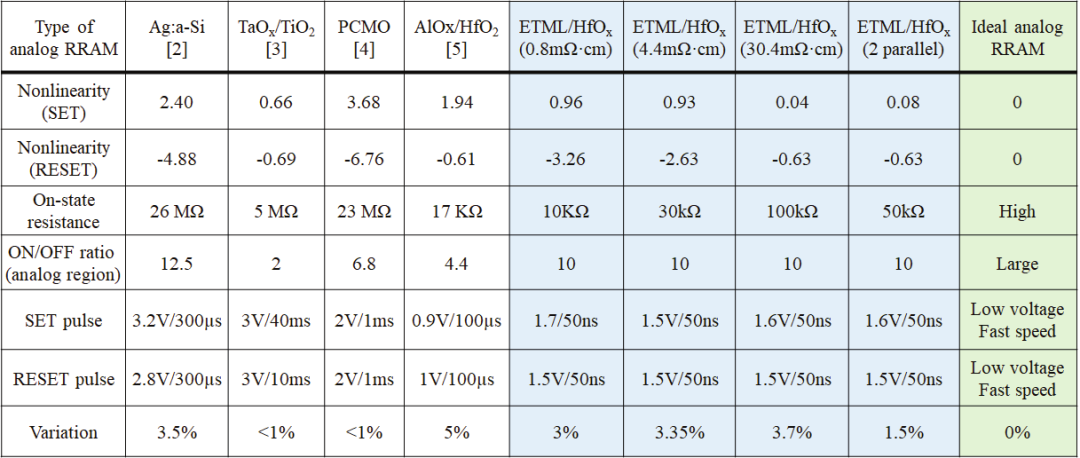

由圖七可以看出,SET/RESET 電壓、電流,LRS/HRS 電阻等都是憶阻器的基本參數。通過對這些參數測試并進行相應的計算,即可得到圖八表中的信息對憶阻器進行表征。根據使憶阻器發生電阻轉變所需的電壓極性,可以將憶阻器分為單極性和雙極性兩類。根據憶阻器的電阻轉變過程中是否存在明確的開關閾值電壓,還可以將憶阻器大致分為數字式與模擬式憶阻器。憶阻器可以是非易失性的,也可以是易失形的;可以是無源的,也可以是有源的②。

圖八

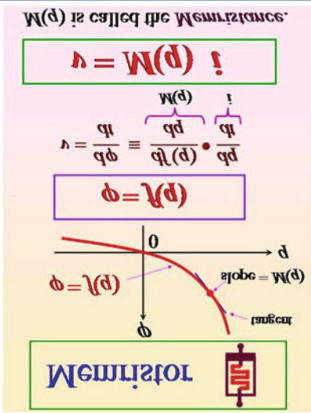

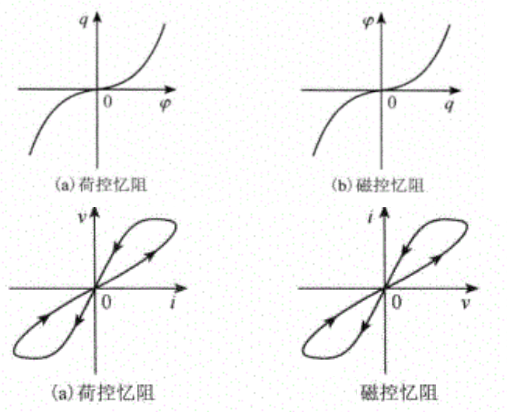

憶阻器基本參數測試以I-V或V-I曲線測試為主。1971年,蔡紹棠教授推導出兩類理想憶阻器公式:

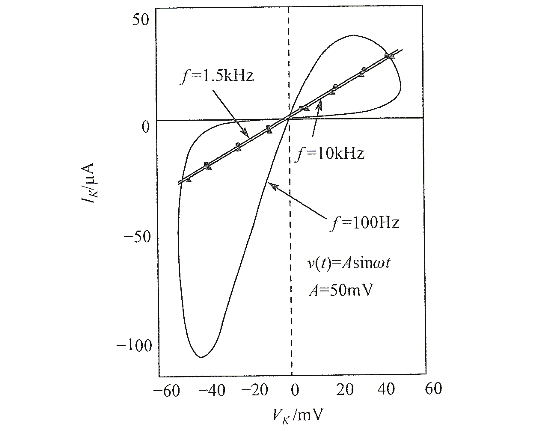

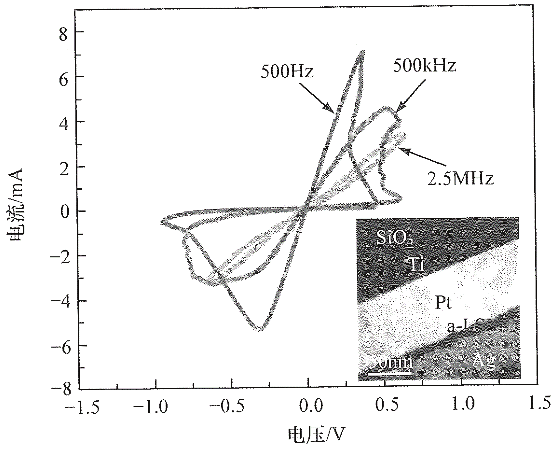

式(1)中M為憶阻值,被稱為電荷控制型理想憶阻器,或電流控制型理想憶阻器。式(2)中W為憶導值,被稱為磁通控制型理想憶阻器,或電壓控制型理想憶阻器。電荷控制型與磁通控制型理想憶阻器在數學上是等價的,如果對理想憶阻器施加任意周期性電壓(電流)信號,然后將激勵電壓(電流)和響應電壓(電流)作圖,得到的李薩如曲線是一個斜“8”字形的緊捏型遲滯回線(Pinched hysteresis loop)(圖九),蔡紹棠教授與《憶阻器導論》編著者們商議后,將其簡寫為“捏滯回線”,并以此作為憶阻現象的標志性判據②。

圖九⑥

近年來,研究人員在多種材料和器件中都發現了捏滯回線這一特征現象,并將這類器件都稱為憶阻器或具有憶阻特性的器件。基于此,蔡紹棠教授2011年撰文提出,不管何種阻變材料或者何種機制,只要二端器件能夠展現捏滯回線這一特征,就是憶阻器。之后又在2013年總結了憶阻器的三條簡單判據②:

·在雙極性周期電信號激勵下,器件在V-I平面的點特性為一個捏滯回線;

·當電信號掃描頻率增大時,捏滯回線波瓣面積持續減小;

·當掃描頻率趨近無窮大時,捏滯回線收縮為一條單值函數(圖十)。

圖十②

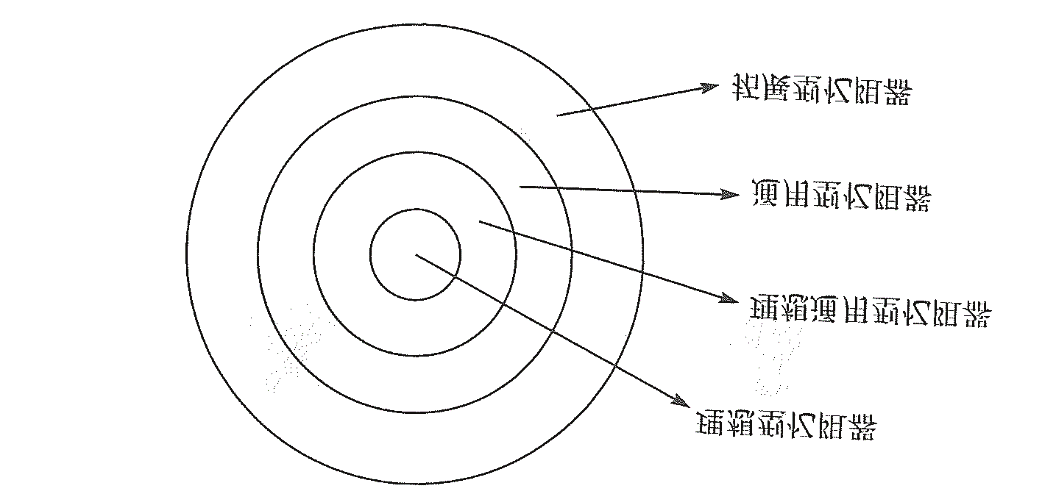

為進一步理清憶阻器的概念,完善憶阻器理論,2015年蔡紹棠教授再次撰文將憶阻器分類為理想型憶阻器、理想通用型憶阻器、通用型憶阻器和拓展型四類憶阻器,圖十一示意出這四類憶阻器之間的關系②。

圖十一

在憶阻系統的概念逐漸被人們接受后,另外兩種記憶電路元件的概念,憶容(Memcapacitor)與憶感(Meminductor)也被相繼提出,其感念是否正確,是否能夠物理實現以及潛在的應用價值得到研究人員的廣泛關注與探討②。

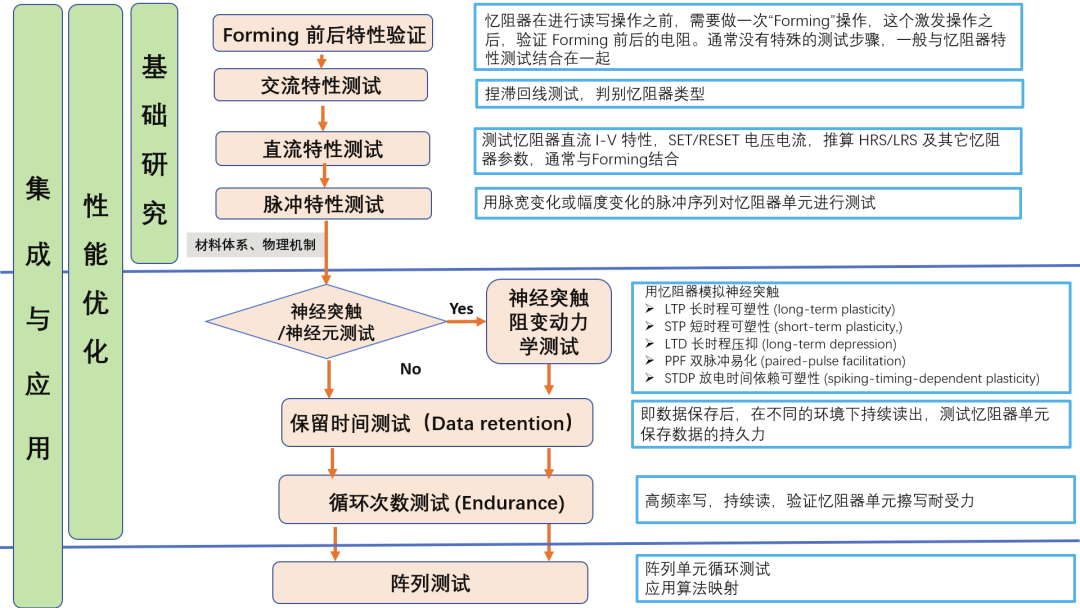

圖十二

憶阻器材料體系和物理機制的研究是憶阻器基礎研究,捏滯回線的測試最為重要。在基礎研究的基礎上,需要對憶阻器進行性能優化,規模集成以及神經形態計算、圖像識別等應用層面的研究。不同的研究領域都需要特定的測試儀器,圖十二示意出憶阻器研究測試流程。

點擊閱讀原文,

下載完整版白皮書并申請技術支持!

欲知更多產品和應用詳情,您還可以通過如下方式聯系我們:

郵箱:china.mktg@tektronix.com

網址:www.tek.com.cn

電話:400-820-5835(周一至周五900)

將您的靈感變為現實

我們提供專業的測量洞見信息,旨在幫助您提高績效以及將各種可能性轉化為現實。

泰克設計和制造能夠幫助您測試和測量各種解決方案,從而突破復雜性的層層壁壘,加快您的全局創新步伐。我們攜手共進,一定能夠幫助各級工程師更方便、更快速、更準確地創造和實現技術進步。

掃碼添加“泰克工程師小助手”

立享1對1專屬服務!

點擊“閱讀原文”了解更多!

原文標題:一文深入了解憶阻器/神經元網絡測試!(附白皮書下載&直播回顧)

文章出處:【微信公眾號:泰克科技】歡迎添加關注!文章轉載請注明出處。

-

泰克科技

+關注

關注

2文章

175瀏覽量

19125

原文標題:一文深入了解憶阻器/神經元網絡測試!(附白皮書下載&直播回顧)

文章出處:【微信號:泰克科技,微信公眾號:泰克科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一文深入了解憶阻器/神經元網絡測試!(附白皮書下載&直播回顧)

一文深入了解憶阻器/神經元網絡測試!(附白皮書下載&直播回顧)

評論